Clock control circuit, chip and clock control method

A clock control and clock technology, applied in electrical digital data processing, instruments, general-purpose stored program computers, etc., can solve problems such as clock stop, clock discontinuity, and chip system hanging, so as to improve adaptability and ensure clock security , the effect of improving safety

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0052] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

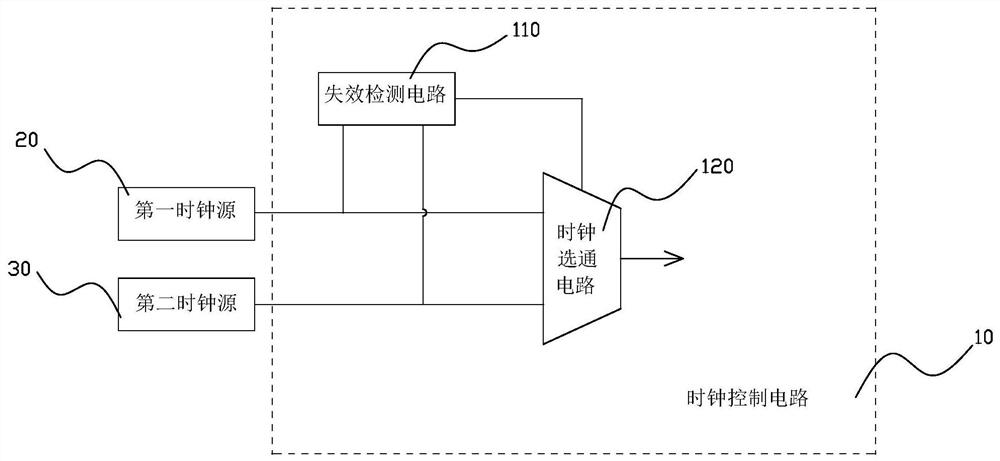

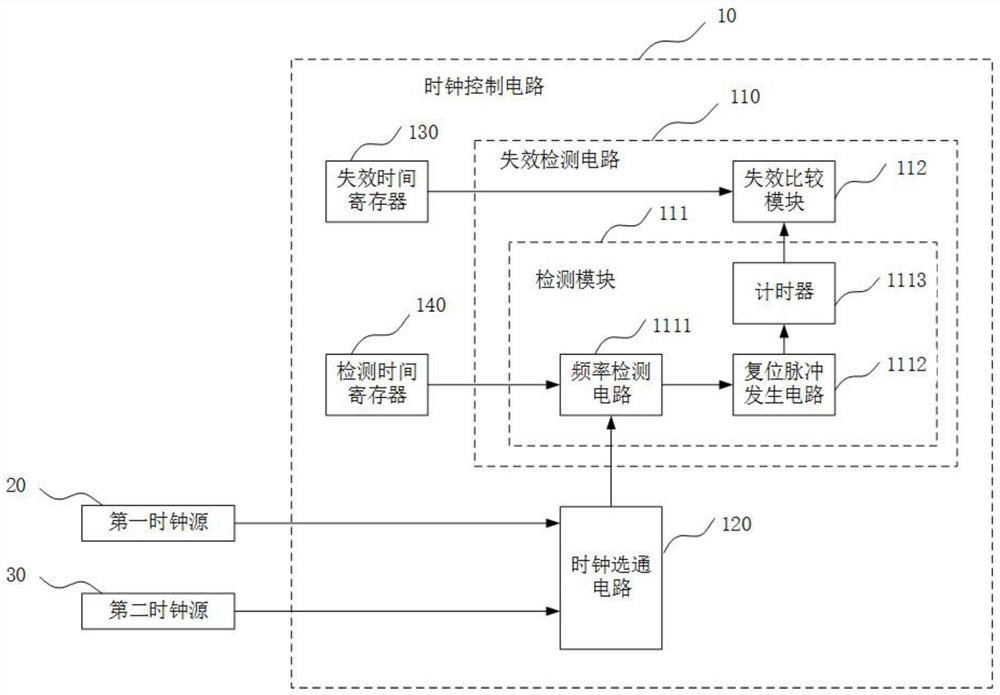

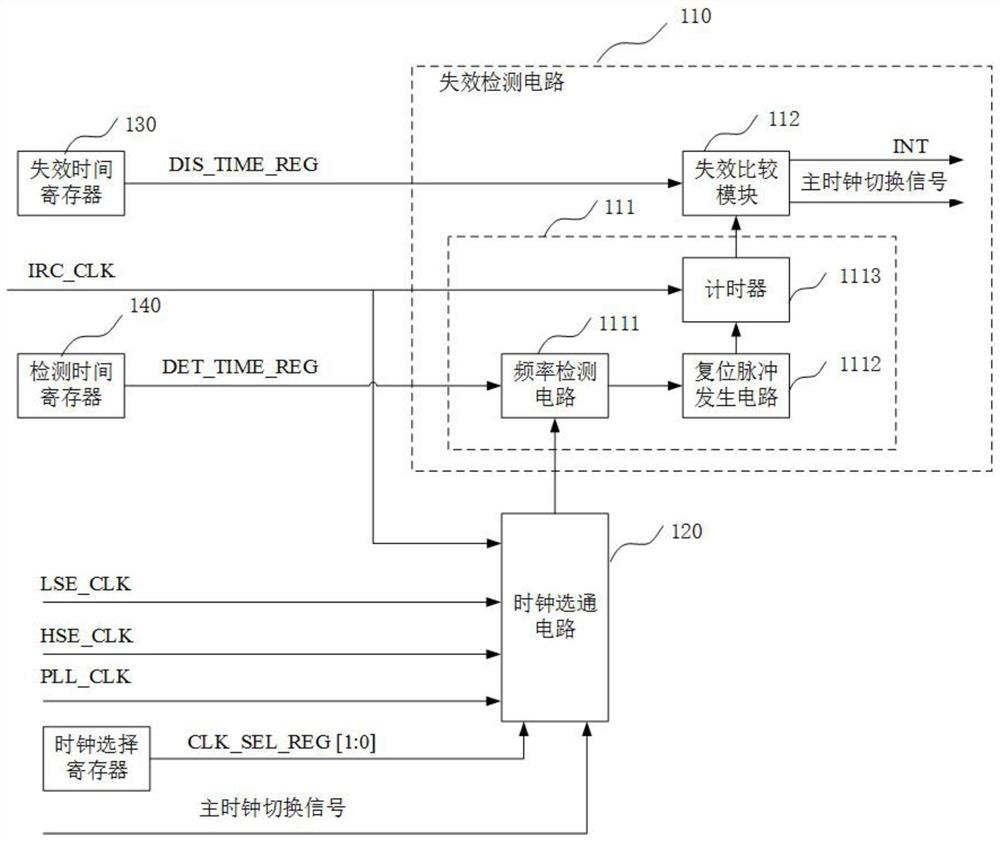

[0053] combine figure 1 Shown is a structural block diagram of a clock control circuit implemented in the present invention, and the clock control circuit can be applied to a chip. Such as figure 1As shown, the chip is provided with a first clock source, and the clock control circuit 10 includes a failure detection circuit 110 and a clock gating circuit 120; the failure detection circuit 110 is respectively connected to the first clock source 20 and the preset second clock source 30, and the failure The detection circuit 120 is used to detect whether the currently selected chip main clock source ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More