FPGA-based high-speed data transmission system frame synchronization parallel implementation method

A system frame, high-speed technology, applied in the field of FPGA-based high-speed data transmission system frame synchronization and parallel implementation, to achieve the effect of taking into account detection probability and false detection probability, reducing calculation delay, and achieving simplicity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

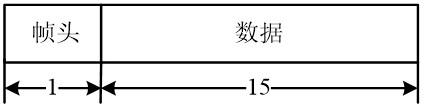

[0050] The highest data transmission rate of the system is 6 Gbit / s, and the sampling rate of AD is 2.6 GHz, which is output in parallel by 8 routes, and the clock of each route is 325 MHz. The frame format of the high-speed data transmission system is attached figure 1 As shown, it includes frame header and data. The data part adopts OFDM modulation of QPSK or 64QAM. There are 15 OFDM symbols in one frame, each symbol contains 1024 subcarriers, and the CP length is 1 / 32 symbol length.

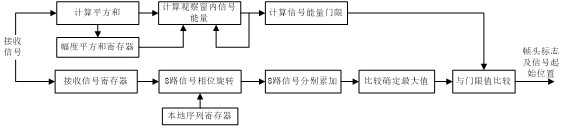

[0051] After quadrature down-conversion and filtering processing, each subcarrier is sampled according to one sample point, and the frame header has a total of 1056 sample points. BPSK single-carrier modulation is adopted, and the length is the same as that of one OFDM symbol. The length of the register for receiving signals is designed to be 1063, and the length of the register for the square sum of the signal amplitudes of 8 channels is 132.

[0052] The implementation process of receivin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More