Method for forming multi-wafer stacking structure

A technology of stacking structure and wafers, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as the inability to meet the needs of multi-wafer bonding and trimming

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0084] Combine below figure 2 , Figure 3a-3d as well as Figure 4a ~ 4f A method for forming a multi-wafer stack structure provided by an embodiment of the present invention is described in detail.

[0085] The multi-wafer stacking structure of this embodiment includes a carrier wafer 110 and two wafers stacked on the carrier wafer 110 in sequence.

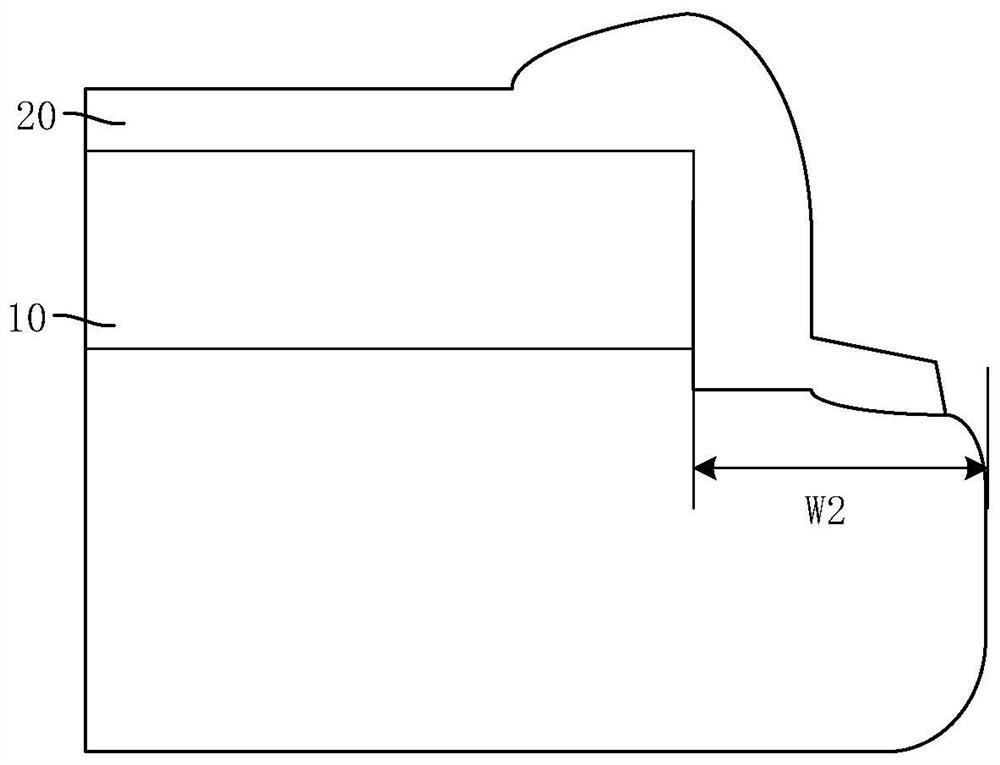

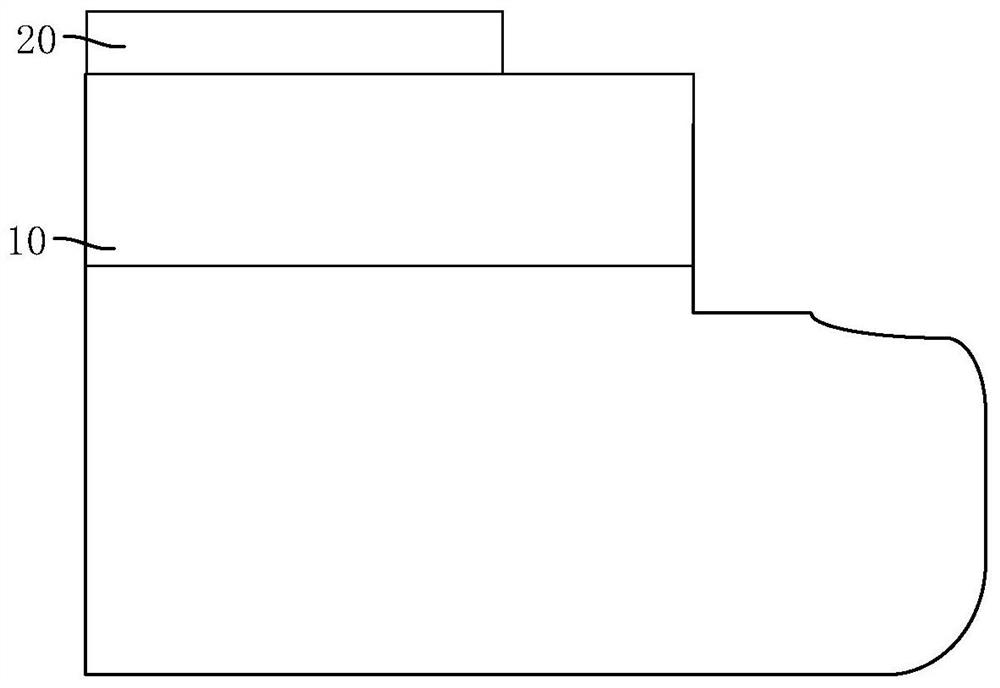

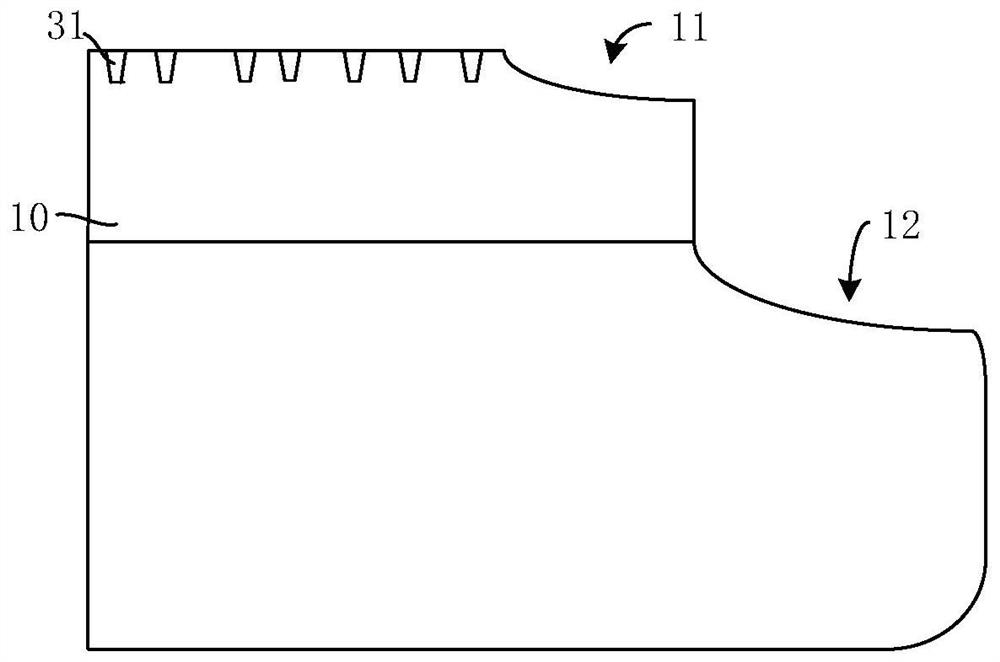

[0086] Figure 3a It is a schematic cross-sectional structure diagram of the first stack structure provided in this embodiment. like Figure 3a As shown, step S1 is first performed to bond the first wafer 120 whose front edge area has been trimmed to the carrier wafer 110, and then grind and thin the first wafer 120 from the back side 120b of the first wafer 120. circle 120, to reserve part of the thickness of the first wafer 120, and form a first stack structure 100, the first stack structure is in the shape of a boss,

[0087] Wherein, the first stack structure 100 has an edge gap area M1 at the edge of the bonding surf...

Embodiment 2

[0110] Compared with Embodiment 1, the multi-wafer stacking structure of this embodiment includes a carrier wafer 110 and N wafers sequentially stacked on the carrier wafer 110 , where N≥3, and N is a positive integer. And after the second stack structure in step S3 is formed, then step S42 is performed to form the (i-1)th bonding hole on the front surface of the (i-1)th stack structure, and ) bonding holes are filled with the (i-1)th metal layer, the (i-1)th metal layer also covers the front side of the (i-1)th stack structure, and then the (i-1)th trimming the edge area of the front side of the stack structure to remove the edge gap area of the (i-1)th stack structure, and then planarizing the (i-1)th metal layer to form the (i-1)th bond fit pad.

[0111] Then step S5 is performed, bonding the i-th wafer whose front edge area has been trimmed to the (i-1) stacked structure, and then grinding and thinning the i-th wafer from the back side of the i-th wafer circle, to re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More