Logic resource evaluation method

A logic resource and resource technology, applied in the field of logic resource evaluation, can solve problems such as inability to complete wiring, inability to quickly predict the number of hardware resources, inability to complete technology mapping, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The present invention will be described in further detail below in conjunction with specific examples, but the embodiments of the present invention are not limited thereto.

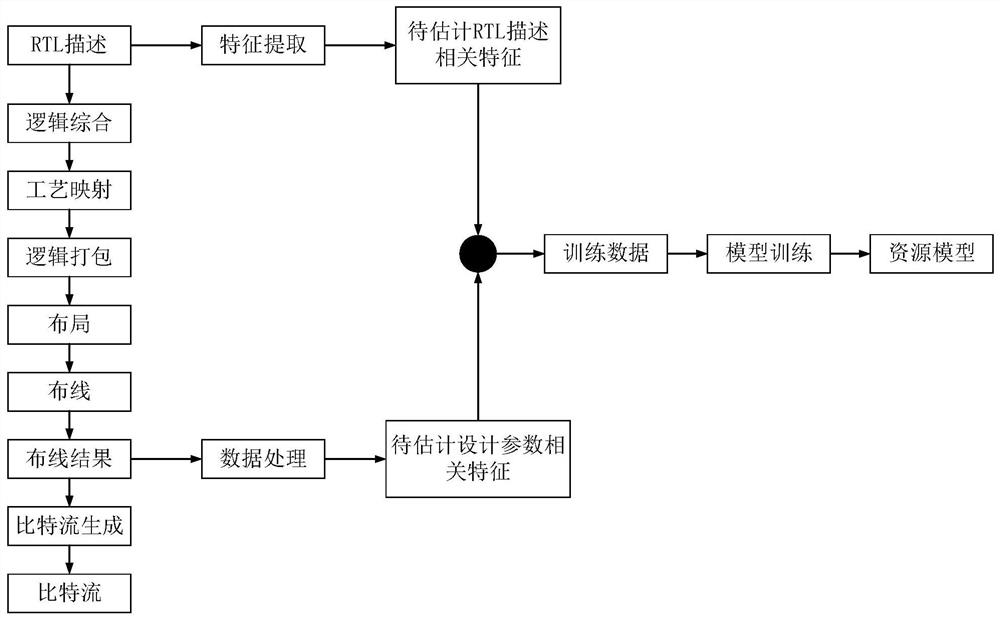

[0031] See figure 1 and figure 2 , figure 1 is a flow chart of a logic resource evaluation method provided by an embodiment of the present invention, figure 2 It is a flow chart of another logical resource evaluation method provided by the embodiment of the present invention. A logical resource assessment method comprising:

[0032] Step 1. Obtain a list of related features to be estimated.

[0033] Specifically, in this embodiment, a list of related features to be estimated needs to be acquired before performing the machine learning-based RTL-level FPGA resource usage estimation.

[0034] Further, step 1 also includes:

[0035] Step 1.1. Obtain the related features of the RTL description to be estimated and the related features of the design parameters to be estimated respectively.

[003...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More