Three-dimensional memory having four stacked layers

A memory, layer stacking technology, applied in the semiconductor field, can solve problems such as inability to provide bit density, competition, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] In order to make the technical solutions and advantages of the embodiments of the present invention more clear, the specific technical solutions of the invention will be further described in detail below in conjunction with the drawings in the embodiments of the present invention.

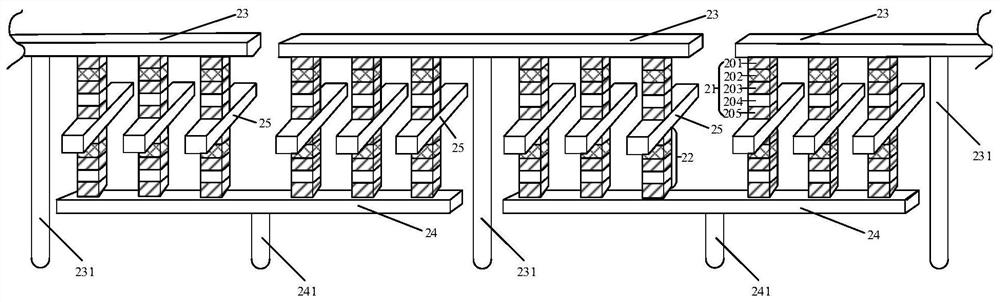

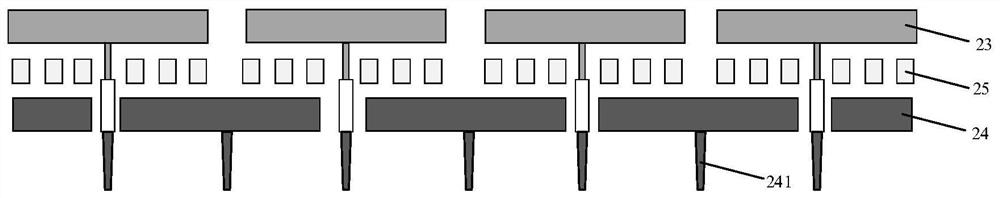

[0041] figure 1 It is a schematic diagram of a three-dimensional phase-change memory cell array observed by a scanning electron microscope. From figure 1 It can be seen that the three-dimensional phase change memory chip is composed of a plurality of small memory cell array blocks with a single bit line, word line and memory cells. A three-dimensional phase-change memory generally includes a top bit line, a word line, a bottom bit line, and a memory cell located at the intersection of the bit line and the word line. In practical application, the word line, top bit line and bottom bit line are usually formed by 20nm / 20nm constant line width (L / S, line / space) formed after the patterning proc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More