FPGA-based embedded data caching system

A data cache and embedded technology, applied in the field of FPGA, can solve the problem of data inconsistency in data cache

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

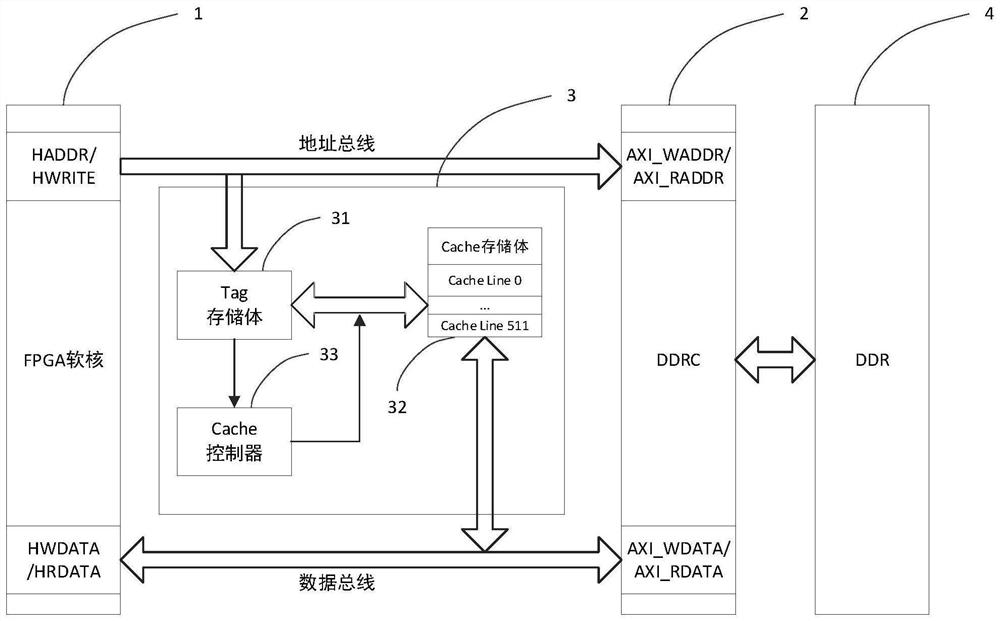

[0035] Please also refer to Figure 1 to Figure 5 , the embodiment of the present invention provides a kind of embedded data caching system based on FPGA, comprises FPGA soft core 1, and it is Cortex M1 soft core, and DDR controller (DDR Controller) 2, it is used for the storage device DDR4 of off-chip Data access, and the Dcache module 3, are used for forced refresh or forced write-back of data, and the FPGA soft core 1 is connected with the DDR controller 2 and the Dcache module 3 through bus communication.

[0036] see figure 1 , the HADDR / HWRI TE data channel of the FPGA soft core 1 communicates with the AXI_WADDR / AXI_RADDR data channel of the DDR controller 2 through an address bus, and the HWDATA / HWDATA data channel of the FPGA soft core 1 communicates with the DDR controller 2 AXI_WDATA / AXI_WDATA data channels communicate through the data bus. The FPGA soft core 1 sends a forced refresh or a forced write-back instruction, and the Dcache module 3 receives a forced refr...

Embodiment 2

[0061] Please also refer to Figure 1 to Figure 5 , the embodiment of the present invention provides a kind of embedded data caching system based on FPGA, comprises FPGA soft core 1, and it is Cortex M1 soft core, and DDR controller 2, it is used for the data access of off-chip storage device DDR4, and The Dcache module 3 is used for forced refresh or forced write-back of data, and the FPGA soft core 1 is connected to the DDR controller 2 and the Dcache module 3 through bus communication.

[0062] see image 3 The HADDR / HWRITE data channel of the FPGA soft core 1 communicates with the AXI_WADDR / AXI_RADDR data channel of the DDR controller 2 through an address bus, and the HWDATA / HWDATA data channel of the FPGA soft core 1 communicates with the DDR controller 2 The AXI_WDATA / AXI_WDATA data channel communicates through the data bus. The FPGA soft core 1 sends a forced refresh or a forced write-back instruction, and the Dcache module 3 receives a forced refresh and clears the T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com