A One-Dimensional dct/idct Transformer Using Bit-Vector Transform, Accumulate and Shift

A vector transform and bit vector technology, applied in the field of one-dimensional DCT/IDCT converter, discrete cosine transform/inverse discrete cosine transform, can solve the problems of low resource utilization efficiency, unusability, different symmetry of basis vectors, etc. Effects of timing design, logic cell saving, register saving

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The technical solutions in the embodiments of the present invention will be clearly and completely described below with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only a part of the embodiments of the present invention, but not all of the embodiments. Based on the embodiments of the present invention, all other embodiments obtained by those of ordinary skill in the art without creative efforts shall fall within the protection scope of the present invention.

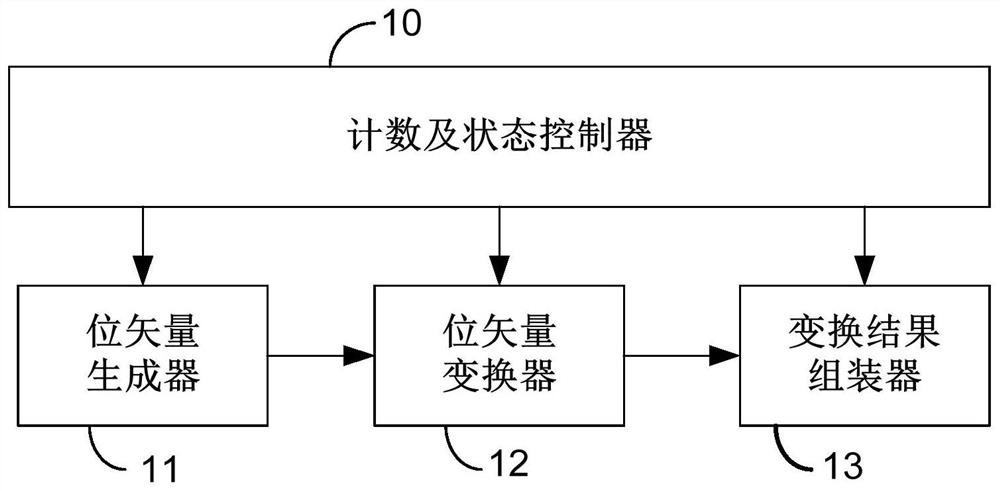

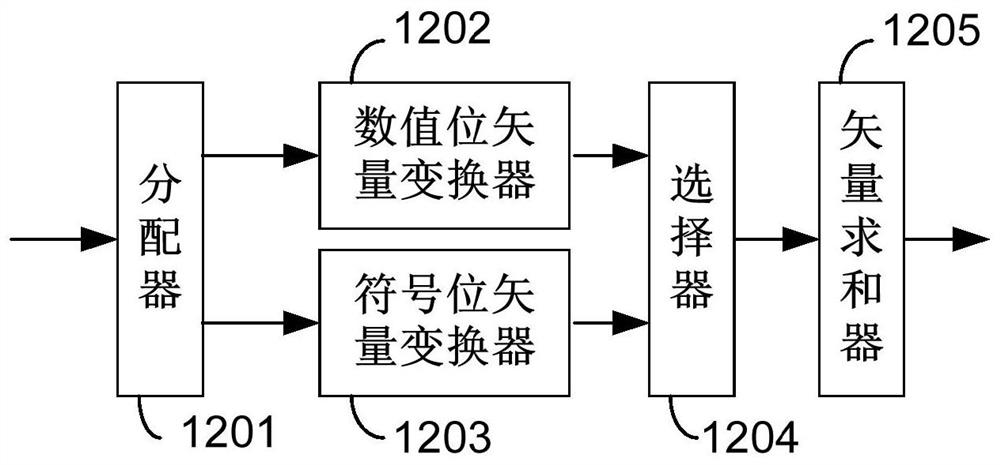

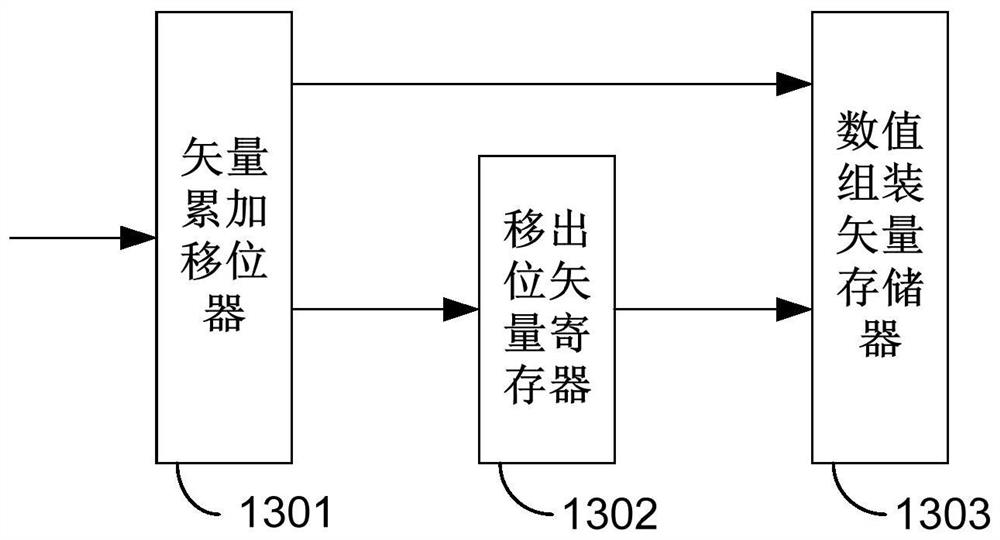

[0032] like figure 1 As shown in the figure, a one-dimensional DCT / IDCT converter that transforms, accumulates and shifts a bit vector includes a counting and state controller 10, a bit vector generator 11, a bit vector converter 12, and a transformation result assembler 13; counting and state control The device 10 is respectively connected with the bit vector generator 11, the bit vector converter 12 and the transformation result ass...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More