Platform architecture design method of multi-core CPU operation mode

A technology of operating mode and platform architecture, applied in the direction of program control design, calculation, multi-program device, etc., can solve problems such as difficulty in taking into account reliability, real-time performance and CPU processing capability, and non-uniform underlying architecture of multi-core processors. Achieve the effect of improving security and system reliability, taking into account reliability, best real-time performance and flexible expansion capabilities

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

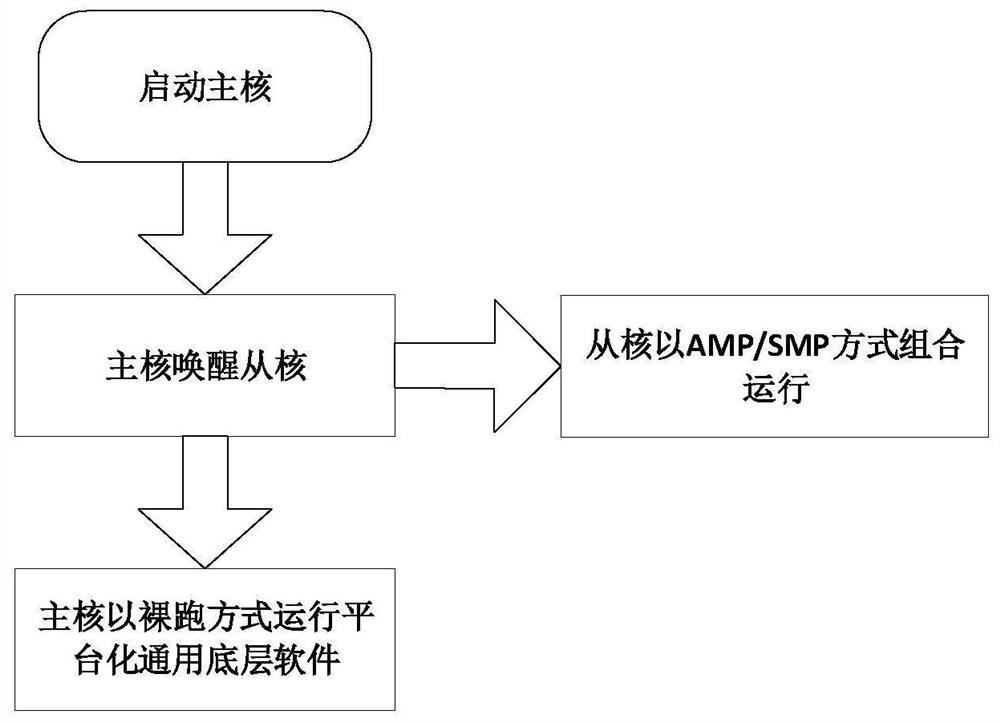

[0031] figure 1 It is a schematic diagram of the multi-core CPU operation mode method, such as figure 1 As stated, the implementation steps of the multi-core enhanced hybrid processing mode include:

[0032] Step 1. After the multi-core CPU is powered on, the main core is first started.

[0033] In this step, start core0 first, that is, core0 is used as the master core, and the other three cores are used as slave cores.

[0034] Step 2, the master core wakes up the slave core.

[0035] In this step, the master core core0 wakes up the three slave cores core1, core2, and core3 in sequence.

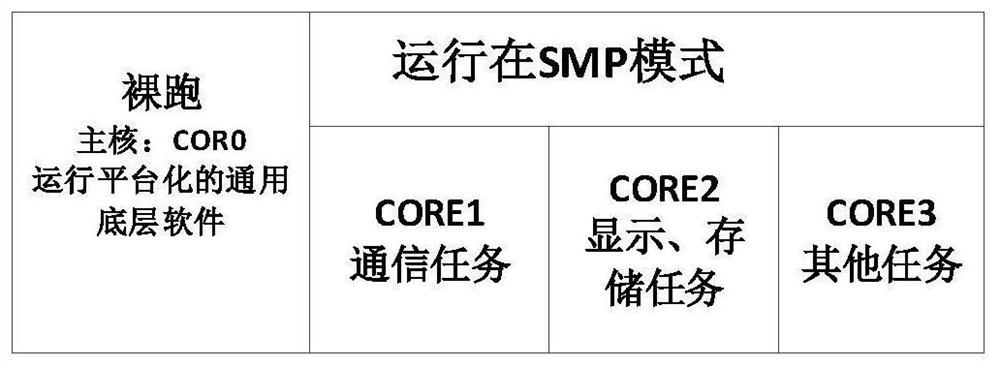

[0036] Step 3, free combination of operating modes from the core.

[0037] In this step, three slave cores run the same operating system and applications.

[0038] Step 4, the main core runs the naked running business.

[0039] In this step, core0 runs its own naked running business program, and tasks with high real-time and reliability are run in the naked running program of core0.

...

Embodiment 2

[0043] figure 1 A schematic diagram of a method for enhancing a hybrid multi-core processing mode for a multi-core CPU, such as figure 1 Said, the steps of the method for multi-core enhanced symmetric multiprocessing include:

[0044] Step 1. After the multi-core CPU is powered on, the main core is first started.

[0045] In this step, core0 is first started, that is, core0 is used as the main core, and the other three cores are used as slave cores.

[0046] Step 2, the master core wakes up the slave core.

[0047] In this step, the master core core0 wakes up the three slave cores core1, core2, and core3 in sequence.

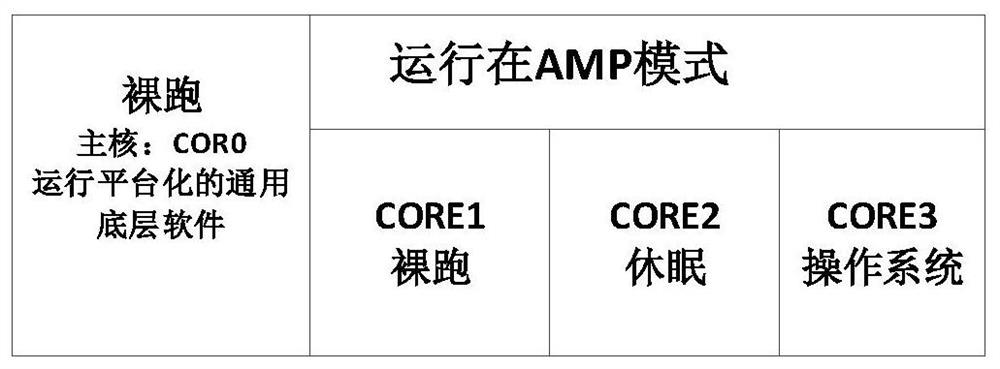

[0048] Step 3, free combination of operating modes from the core.

[0049] In this step, core1 of the three slave cores runs naked, core2 sleeps without running programs, core3 runs the operating system, and core1 and core3 run applications independently.

[0050] Step 4, the main core runs the naked running business.

[0051] In this step, core0 and core1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More