Patents

Literature

36 results about "Asymmetric multiprocessing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An asymmetric multiprocessing (AMP) system is a multiprocessor computer system where not all of the multiple interconnected central processing units (CPUs) are treated equally. For example, a system might allow (either at the hardware or operating system level) only one CPU to execute operating system code or might allow only one CPU to perform I/O operations. Other AMP systems might allow any CPU to execute operating system code and perform I/O operations, so that they were symmetric with regard to processor roles, but attached some or all peripherals to particular CPUs, so that they were asymmetric with respect to the peripheral attachment.

Mapping a computer program to an asymmetric multiprocessing apparatus

ActiveUS20080114937A1Quicker and less-expensiveNot easy to make mistakesMemory adressing/allocation/relocationDetecting faulty computer hardwareMemory hierarchyTheoretical computer science

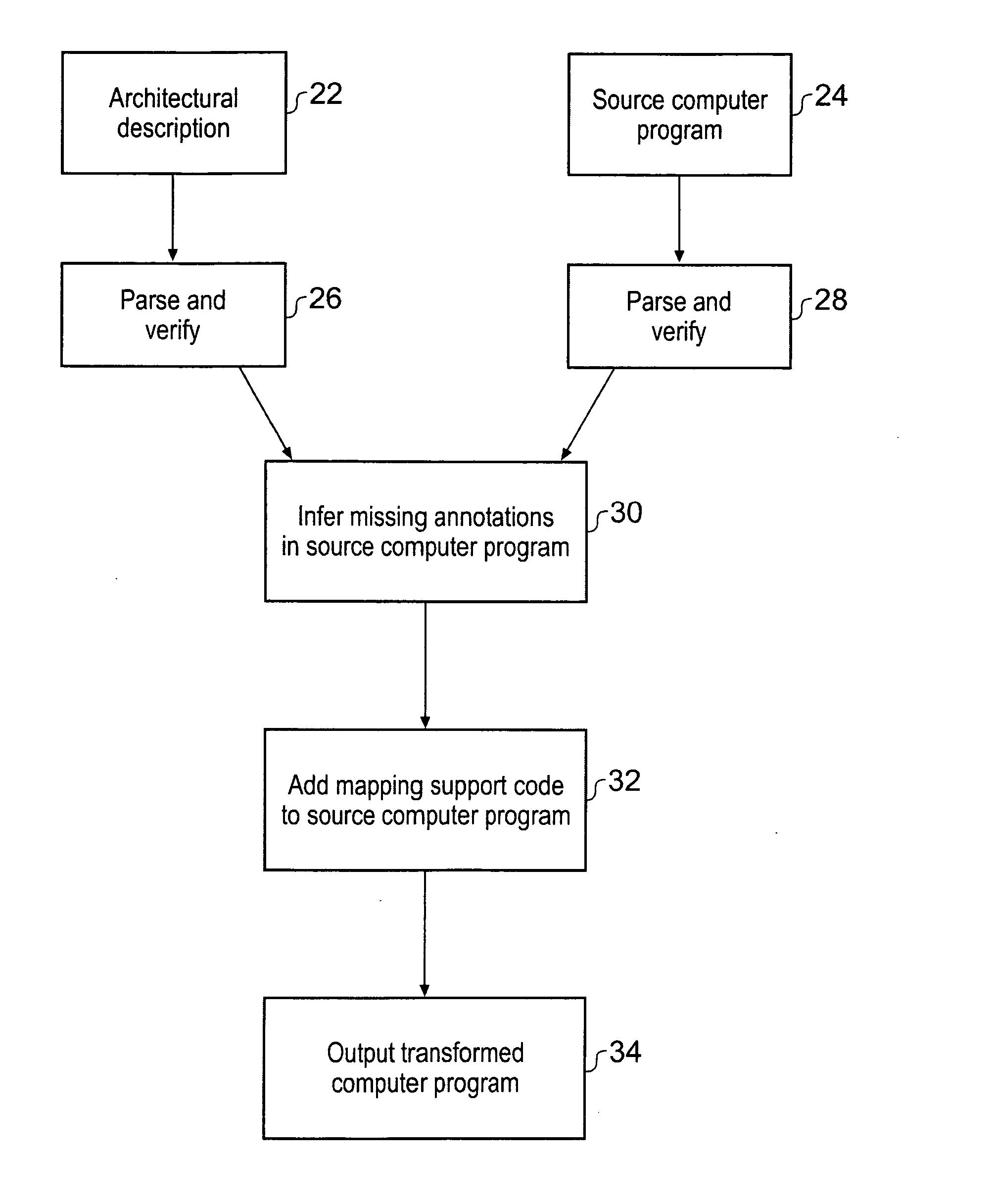

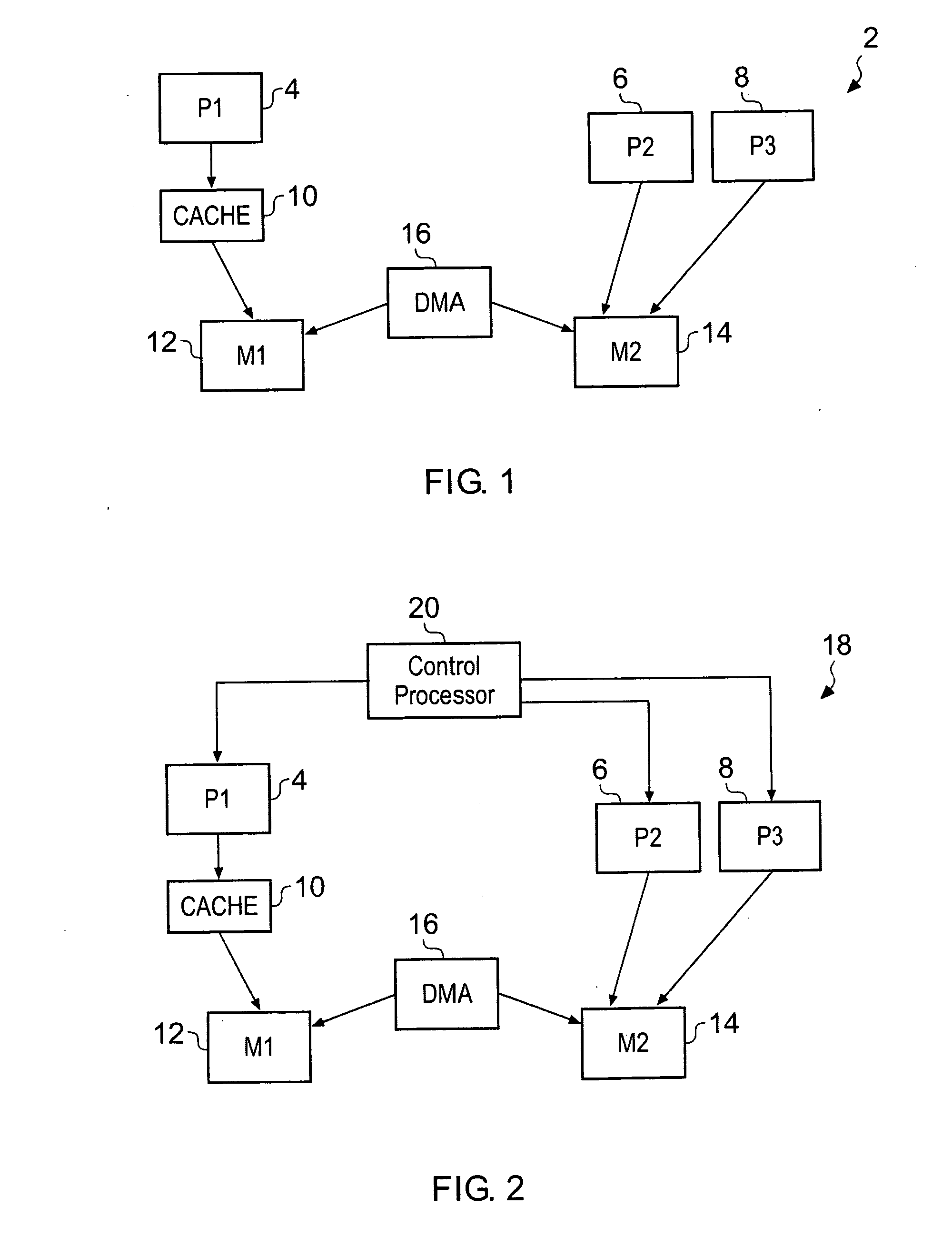

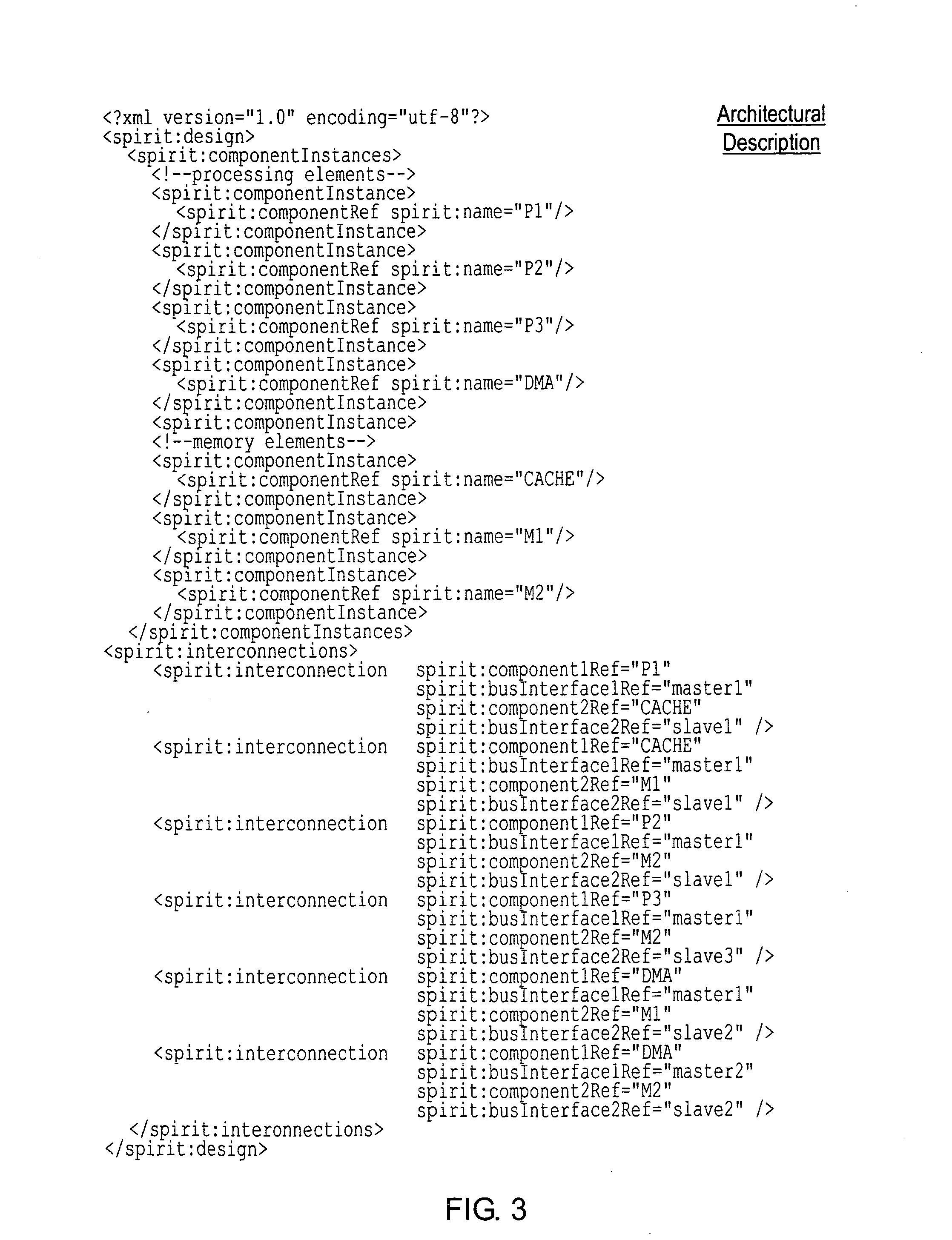

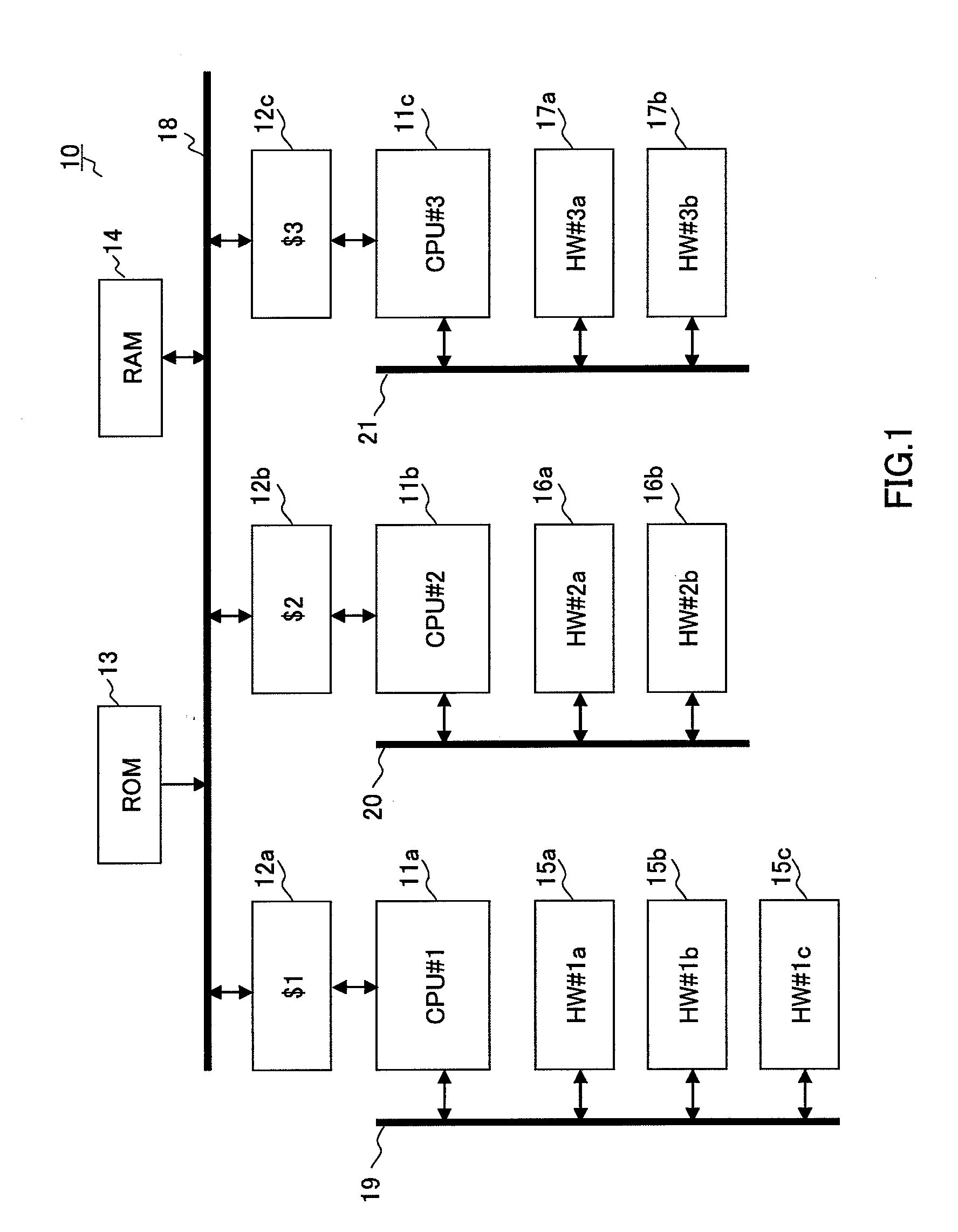

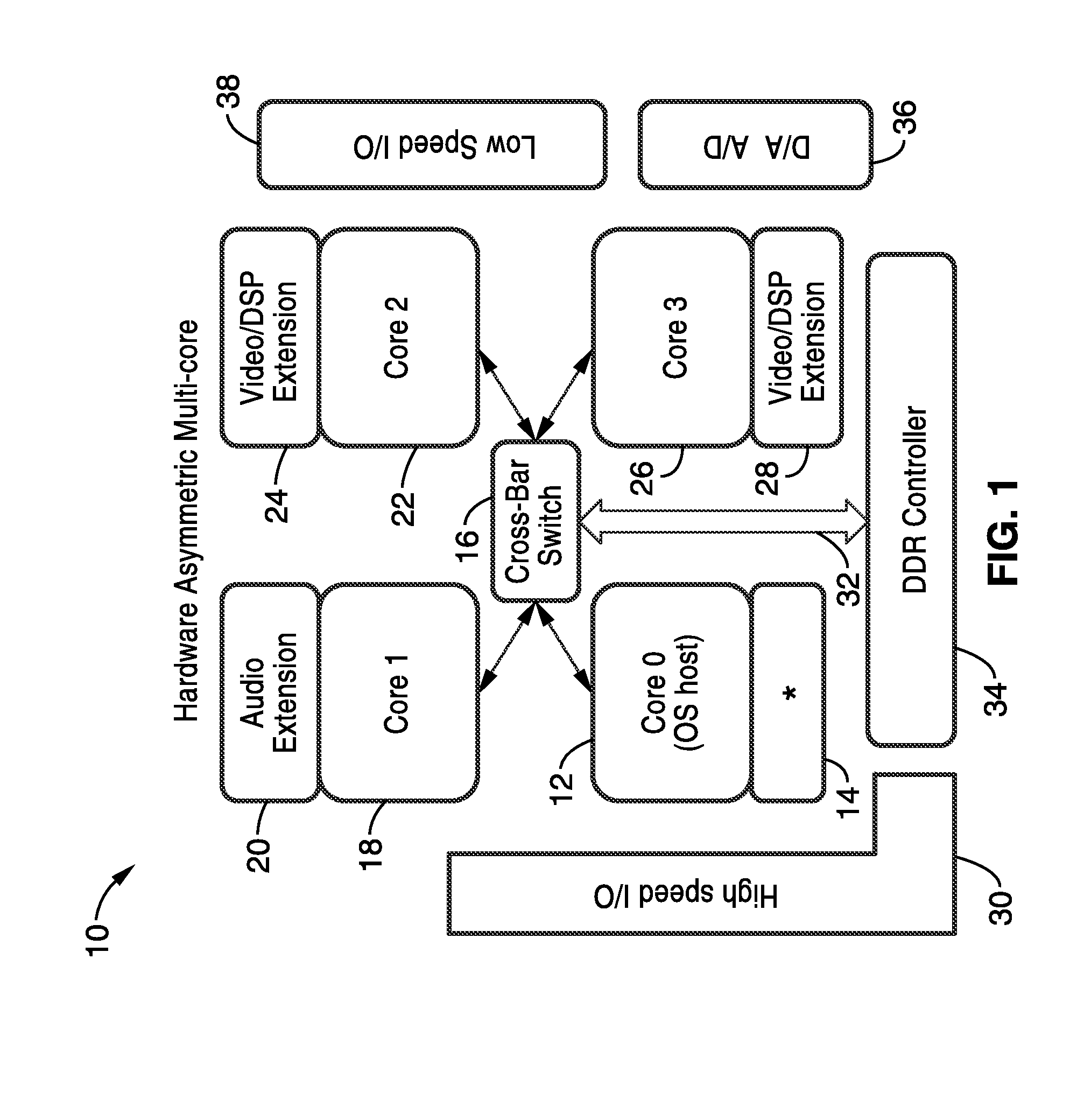

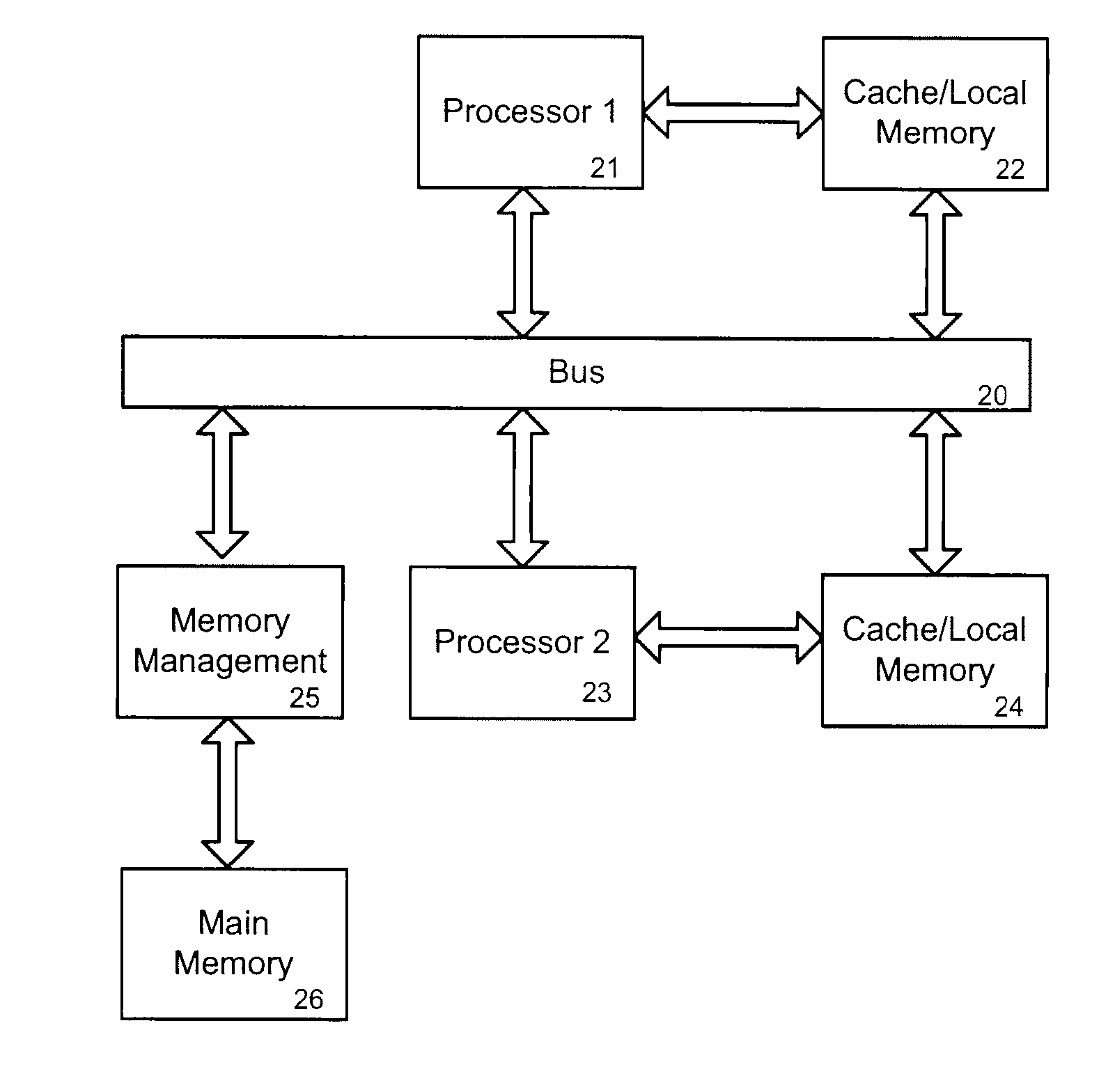

A computer implemented tool is provided for assisting in the mapping of a computer program to an asymmetric multiprocessing apparatus 2 incorporating an asymmetric memory hierarchy formed of a plurality of memories 12, 14. An at least partial architectural description 22, 40 is provided as an input variable to the tool and used to infer missing annotations within a source computer program 24, such as which functions are to be executed by which execution mechanisms 4, 6, 8 and which variables are to be stored within which memories 12, 14. The tool also adds mapping support commands, such as cache flush commands, cache invalidate commands, DMA move commands and the like as necessary to support the mapping of the computer program to the asymmetric multiprocessing apparatus 2.

Owner:ARM LTD

Analyzing and transforming a computer program for executing on asymmetric multiprocessing systems

InactiveUS20080098208A1Easy to implementImprove system performanceDetecting faulty computer hardwareDigital computer detailsParallel computingData shipping

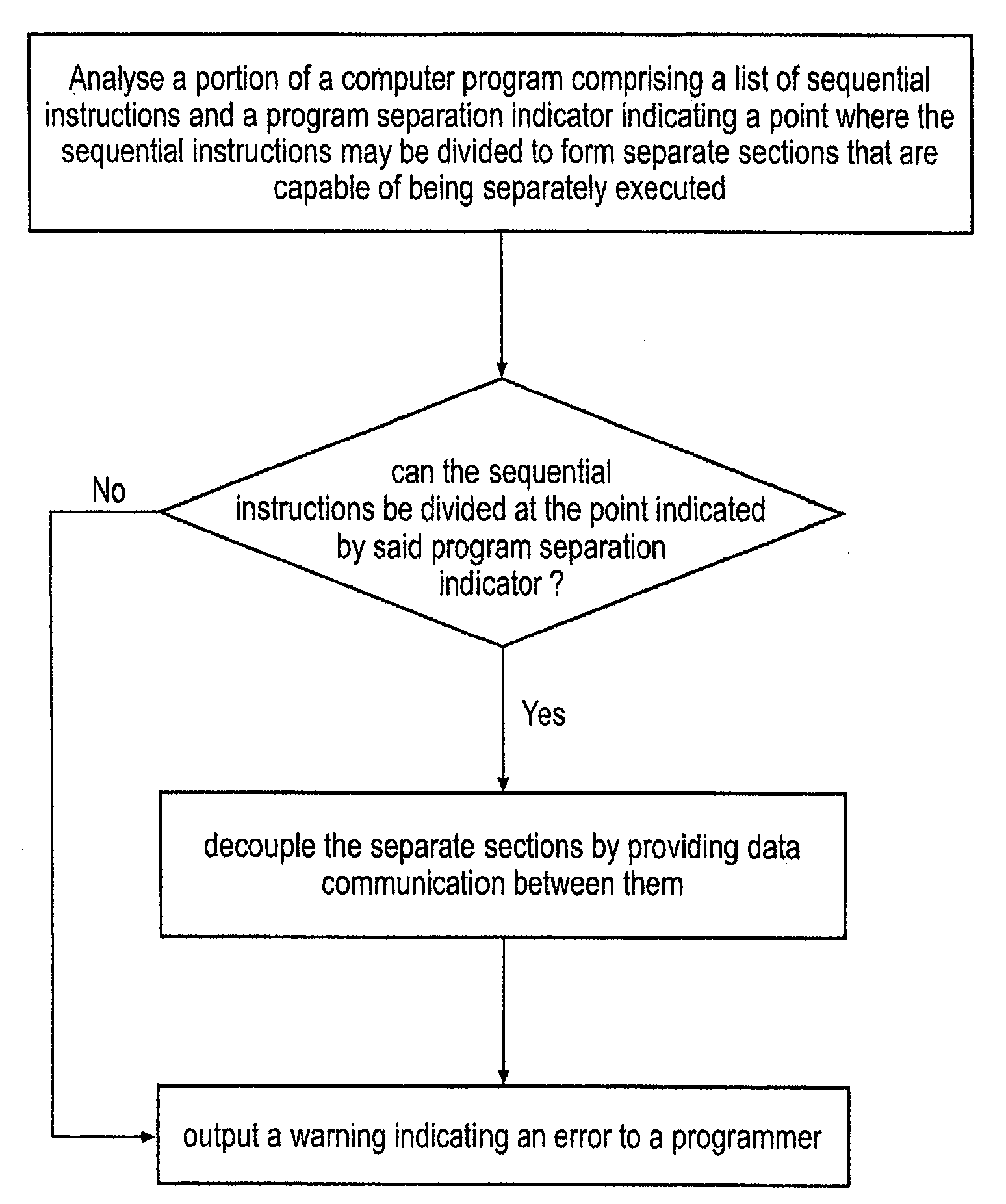

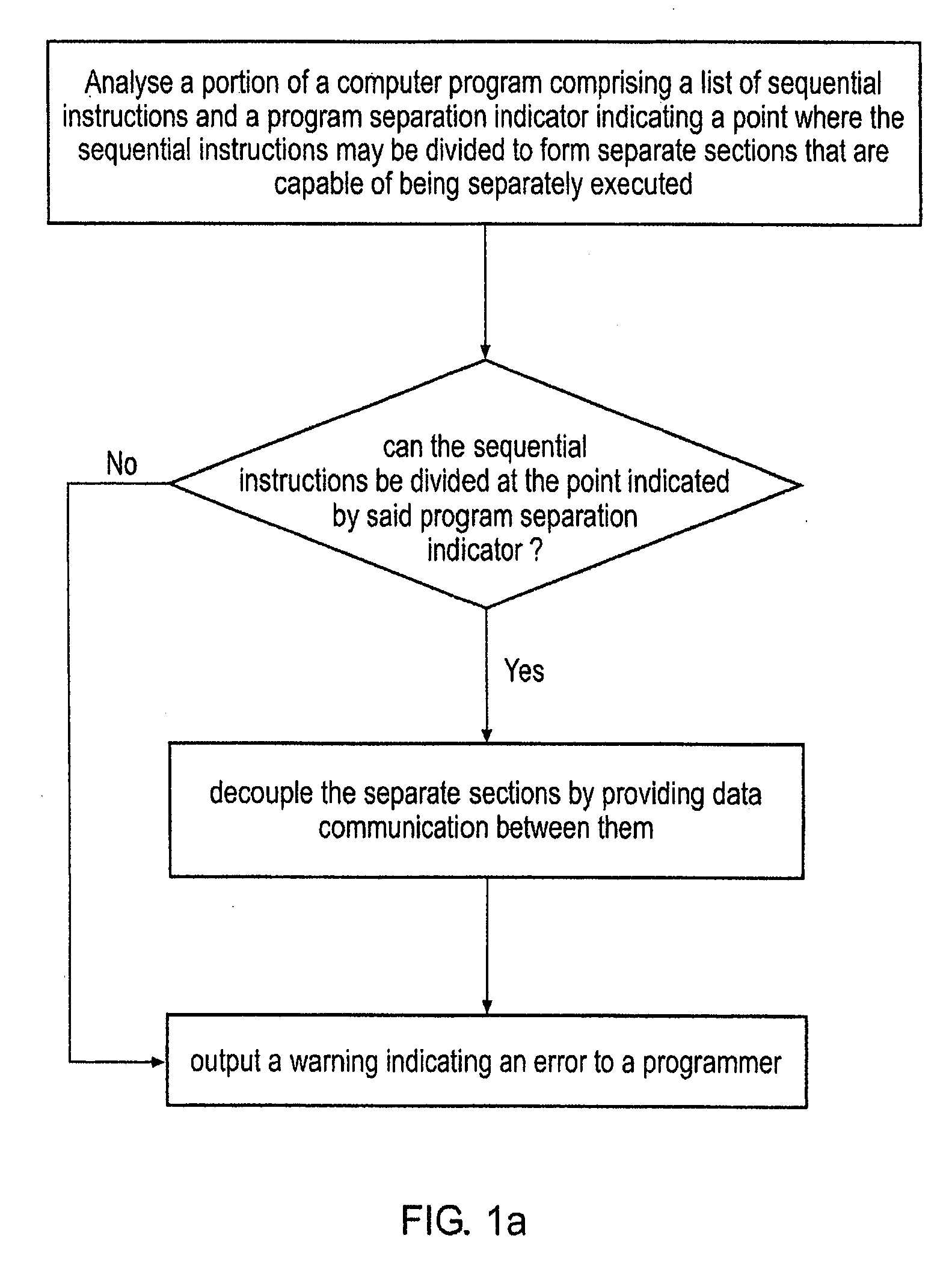

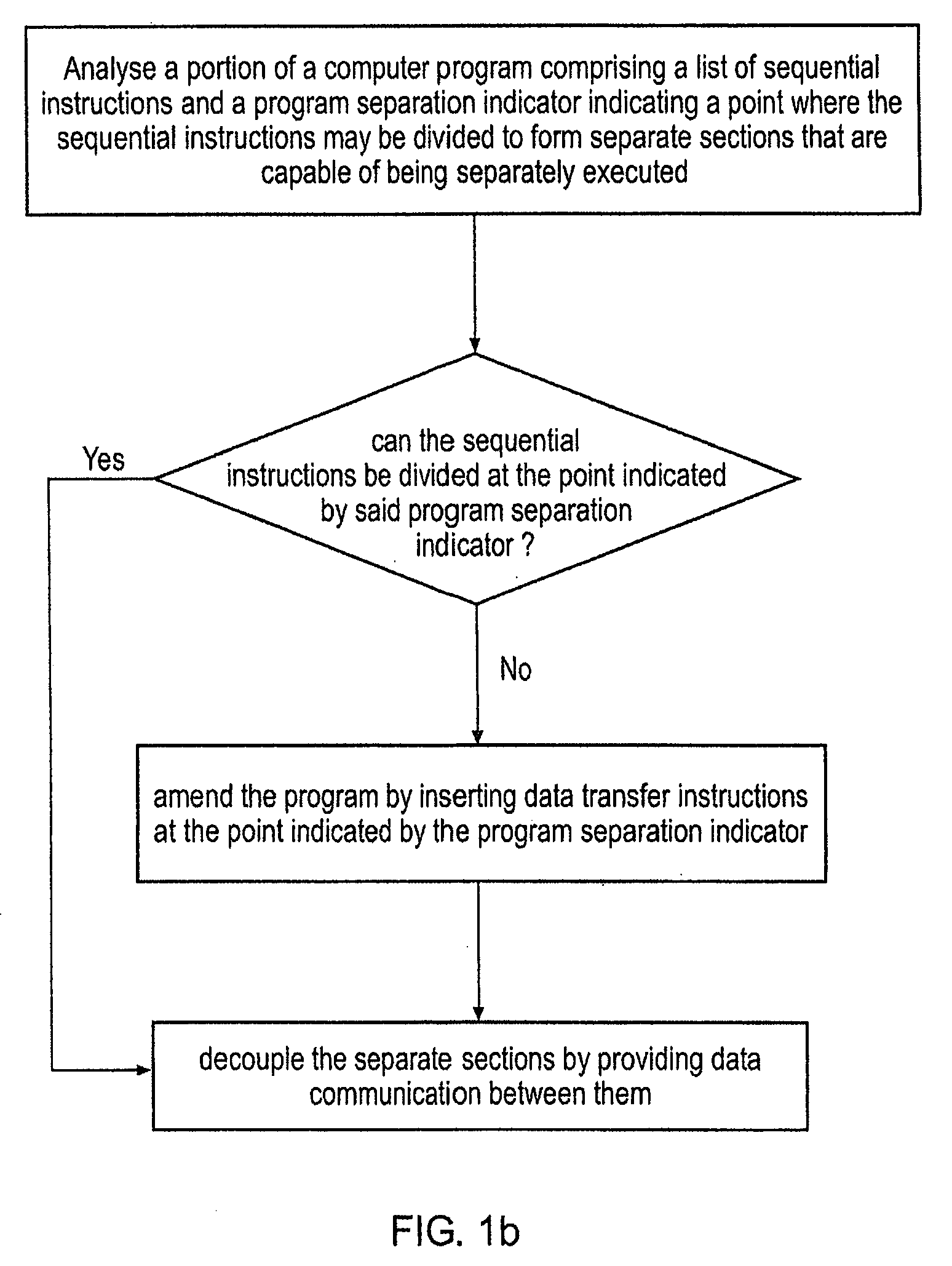

A method is disclosed for transforming a portion of a computer program comprising a list of sequential instructions comprising control code and data processing code and a program separation indicator indicating a point where said sequential instructions may be divided to form separate sections that are capable of being separately executed and that each comprise different data processing code. The m method comprises the steps of: (i) analysing said portion of said program to determine if said sequential instructions can be divided at said point indicated by said program separation indicator and in response to determining that it can: (iia) providing data communication between said separate sections indicated by said program separation indicator, such that said separate sections can be decoupled from each other, such that at least one of said sections is capable of being separately executed by an execution mechanism that is separate from an execution mechanism executing another of said separate sections, said at least one of said sections being capable of generating data and communicating said data to at least one other of said separate sections; and in response to determining it can not: (iib) not performing step (iia). If step (iia) is not performed then a warning may be output, or the program may be amended so it can be separated at that point, or the program separation indicator may be removed and the sections that were to be separated merged.

Owner:RGT UNIV OF MICHIGAN +1

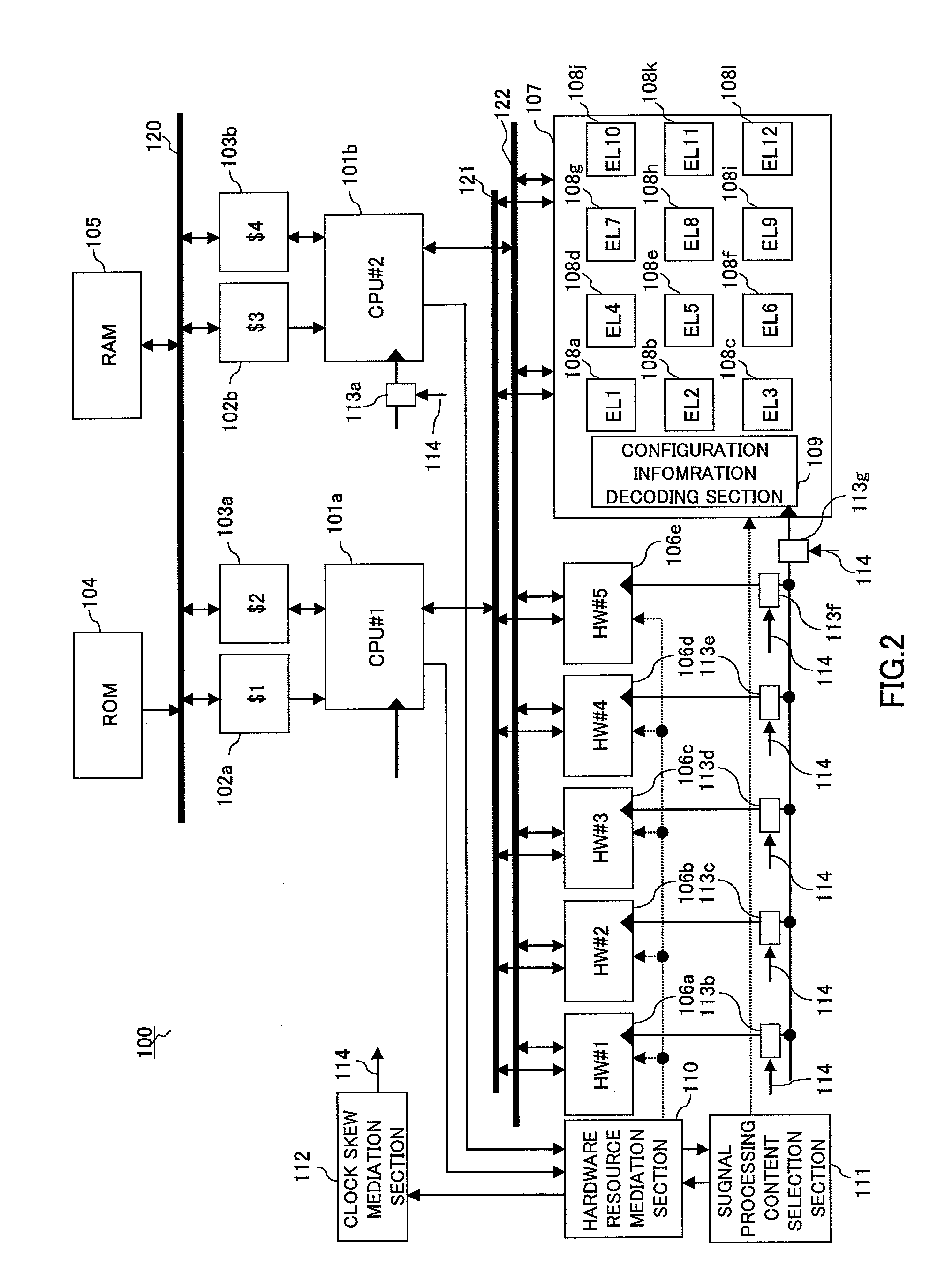

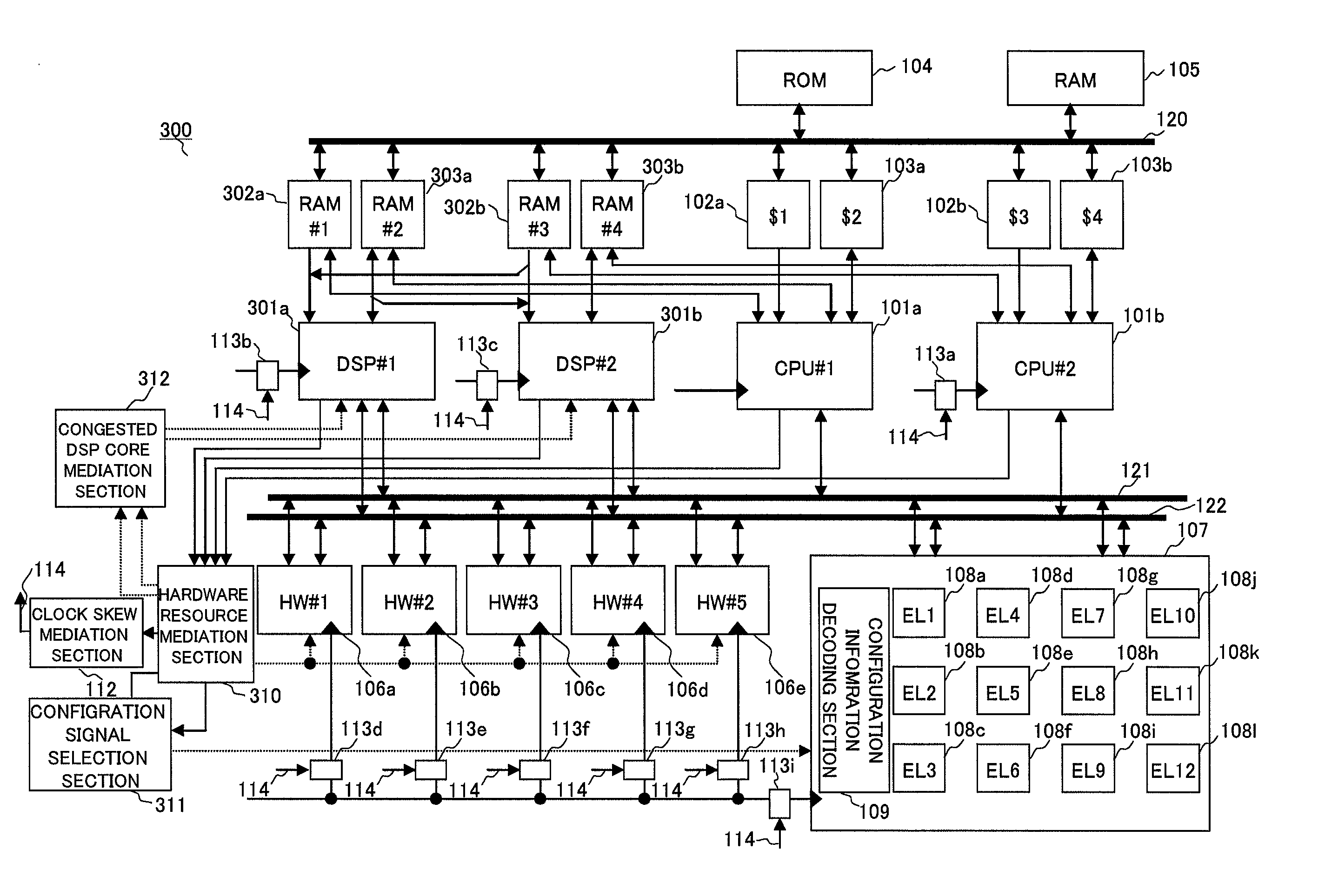

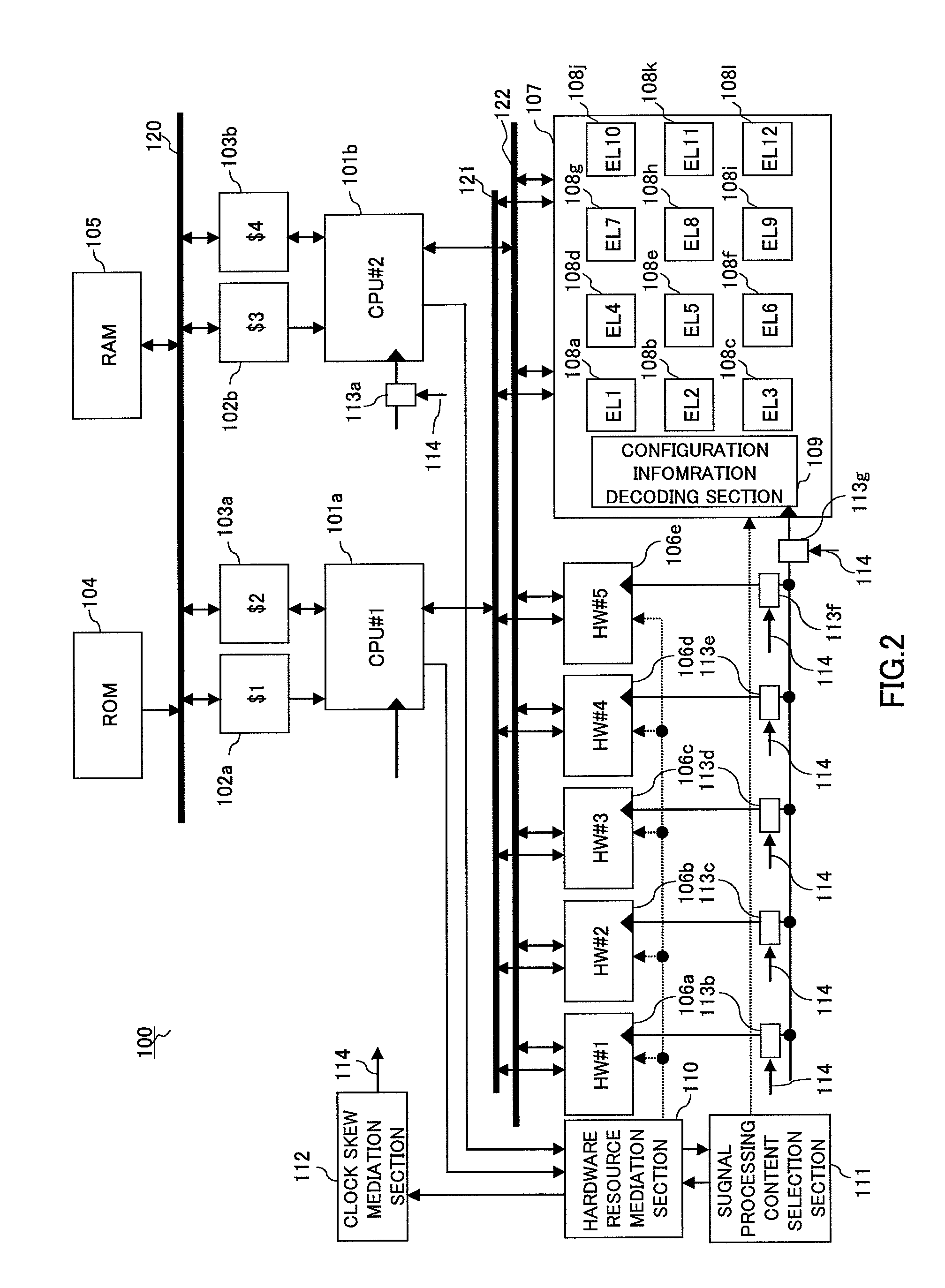

Asymmetric multiprocessor

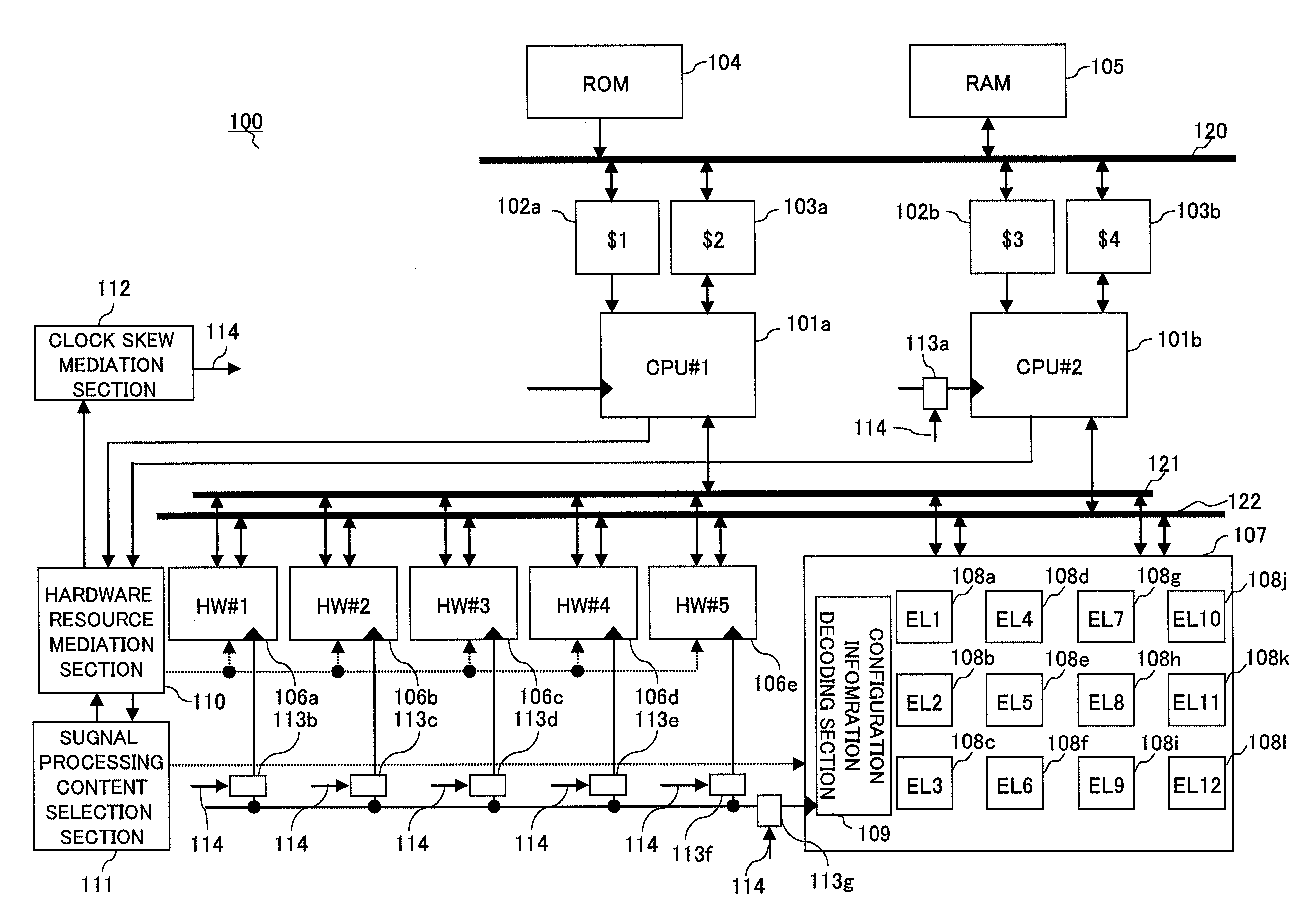

InactiveUS20070283128A1Increase freedomLoad minimizationEnergy efficient ICTGeneral purpose stored program computerExecution controlClock phase

An asymmetric multiprocessor capable of increasing the degree of freedom of distributed processing, minimizing the processing load on each processor (CPU), and achieving a large reduction in power consumption by reducing the operating frequency or lowering the power supply voltage. Asymmetric multiprocessor (100) includes a hardware resource mediation section (110) that mediates request signals requesting permission to use arbitrary hardware accelerators from CPU cores (101a and 101b) ; a signal processing content selection section (111) that selects signal processing content of dynamically reconfigurable signal processor section (107) connected as a slave; a clock skew mediation section (112) that performs control to arbitrarily shift a clock phase relationship among groups; and clock delay generation sections (113a through 113g) that delay a clock signal based on clock skew selection enable signal (114).

Owner:SOCIONEXT INC

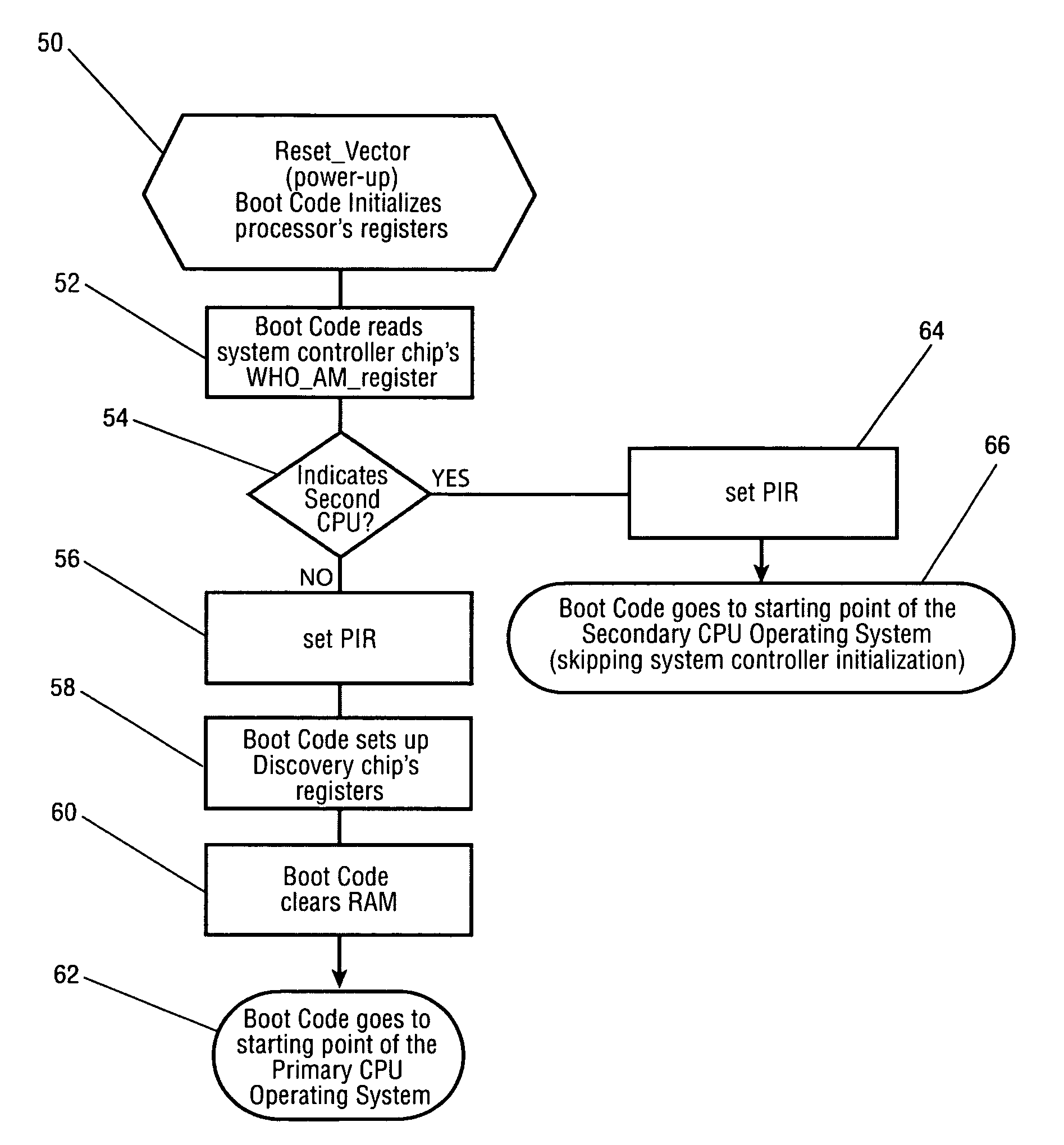

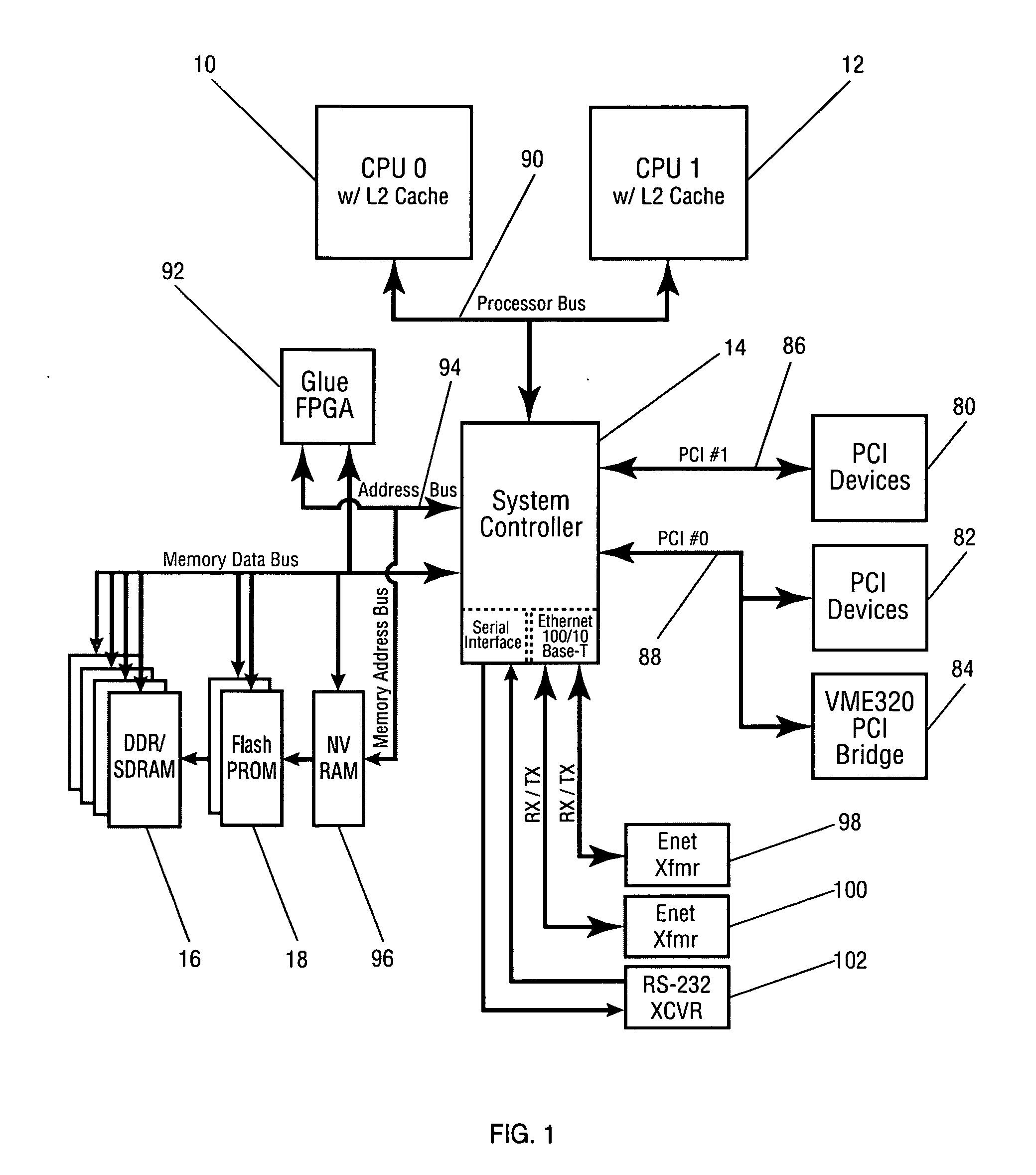

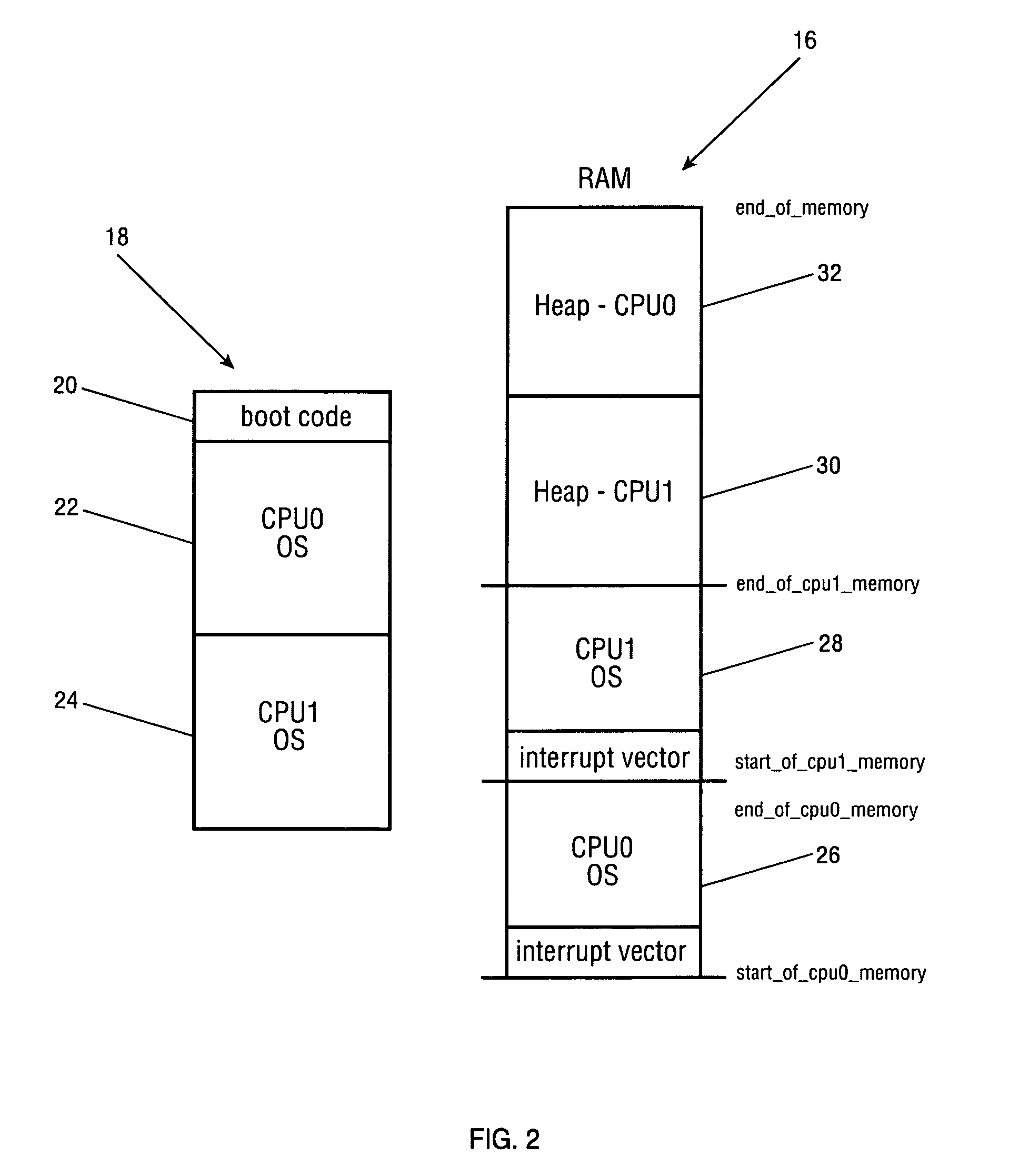

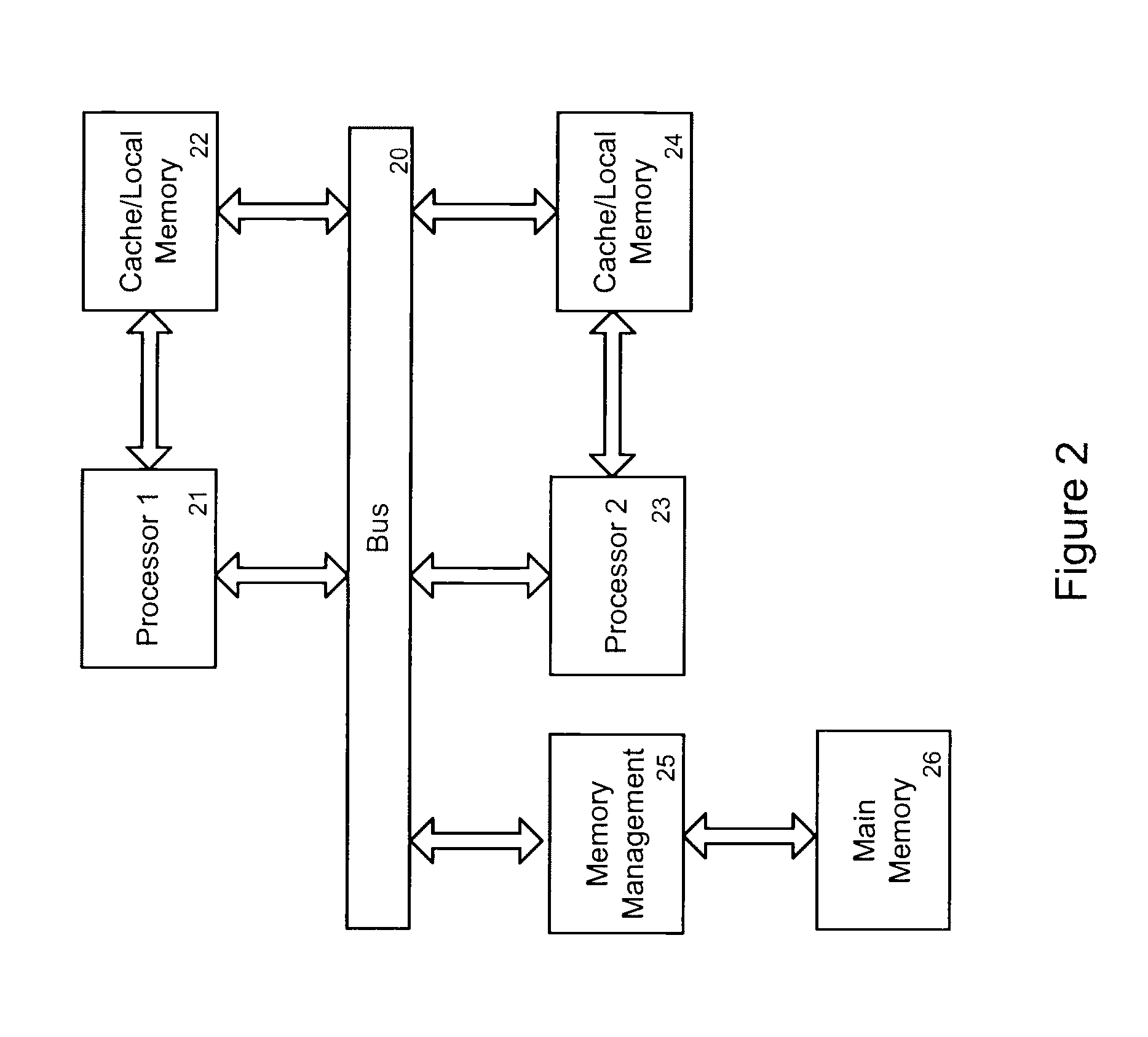

Cooperative asymmetric multiprocessing for embedded systems

InactiveUS20080046891A1Allow useDigital computer detailsMultiprogramming arrangementsOperational systemMulti processor

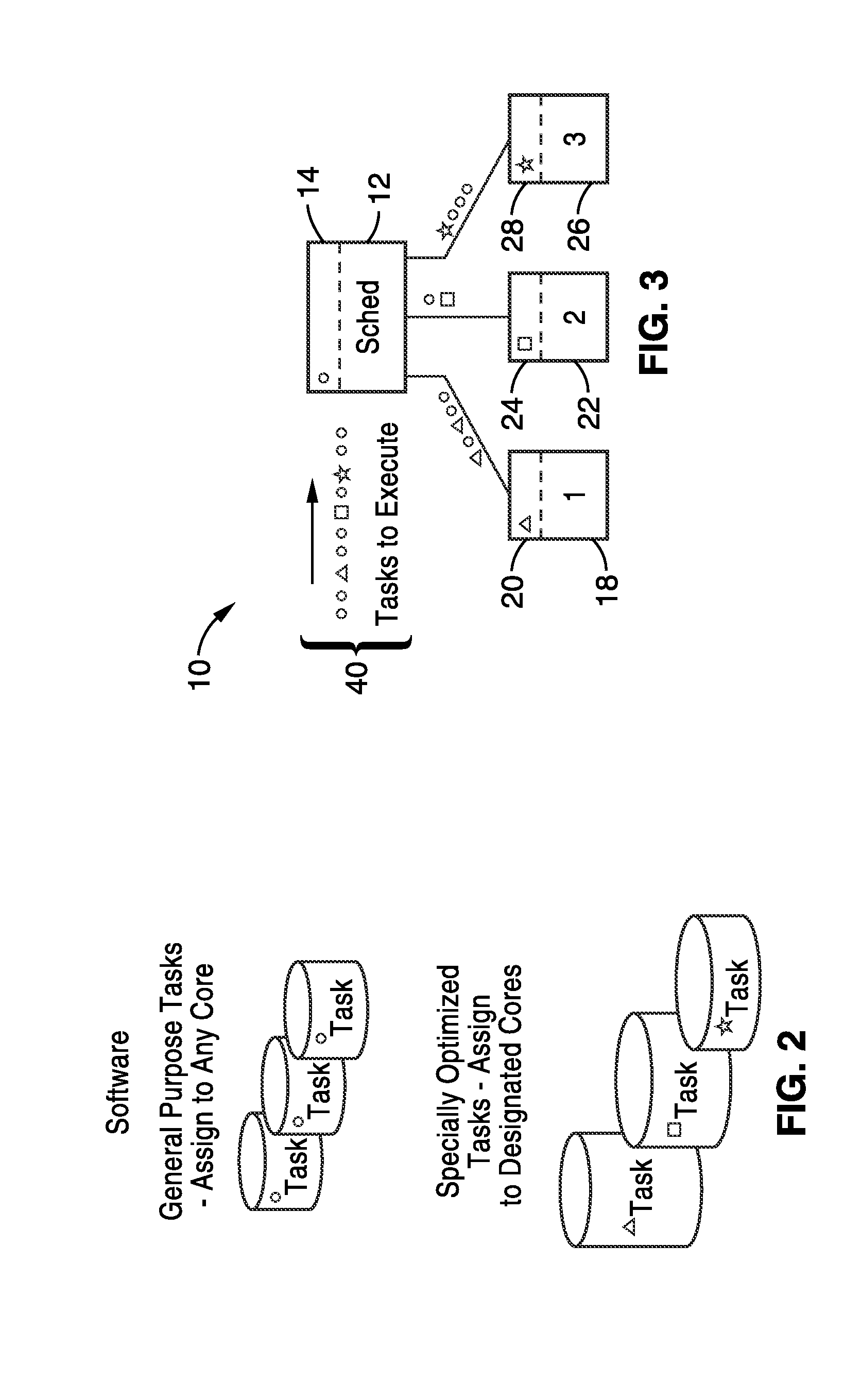

Cooperative Asymmetric Multiprocessing allows for operating systems to function independently of each other on multiple processors sharing common resources in an embedded system. However, some degree of cooperation is required because there are resources with single instances shared across both cores, such as interrupt controller, boot sequencer, DMA engines, etc. The ability to support two distinct operating systems independently gives valuable flexibility. This method allows for reduced complexity in a multi processor system and allows use of existing tools with minimal modifications.

Owner:HONEYWELL INT INC

Symmetric multi-processor operating system for asymmetric multi-processor architecture

InactiveUS20100242014A1Maximum reusabilityDevelopment effortEnergy efficient ICTProgram control using stored programsOperational systemMulti processor

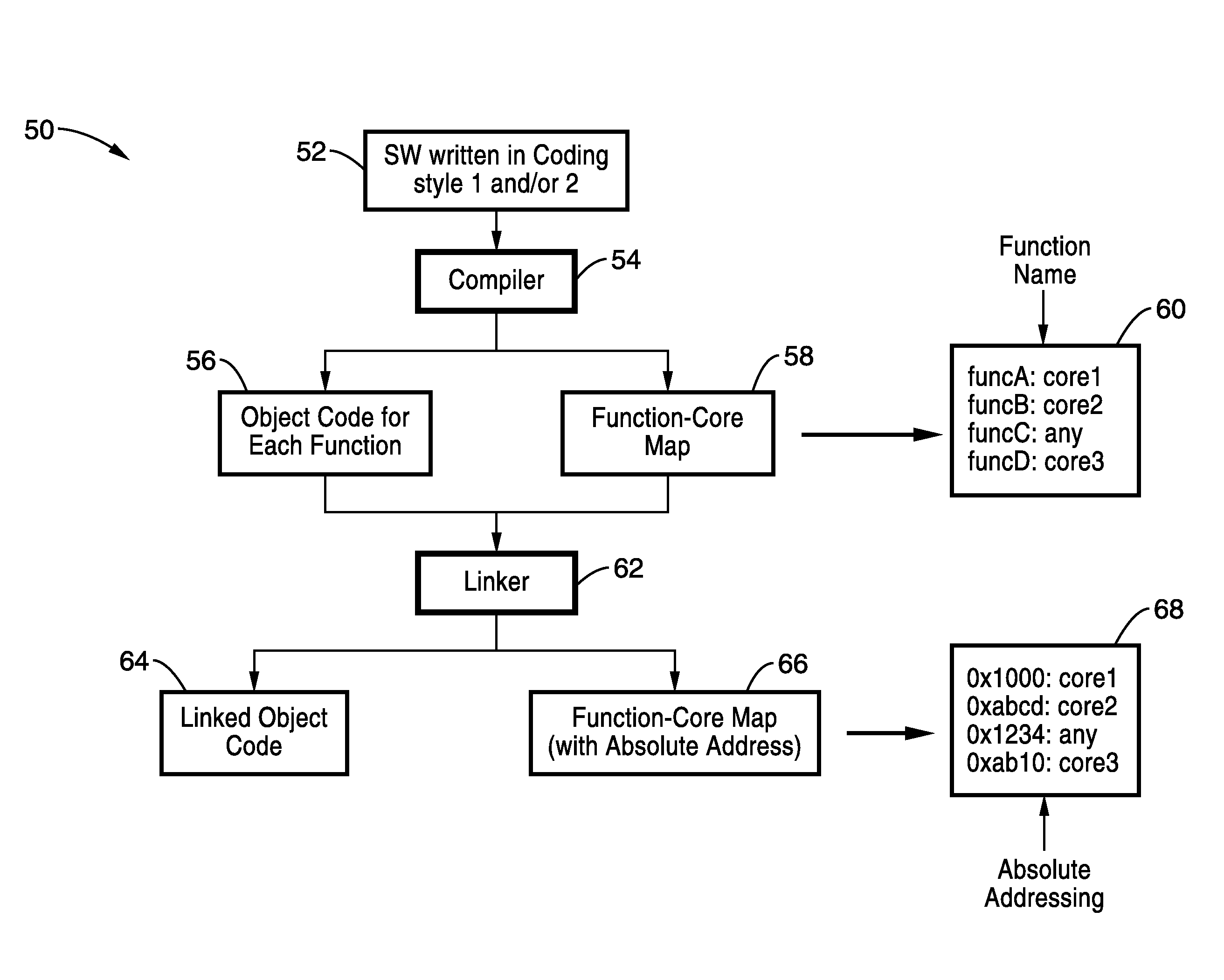

A method and system for supporting multi-processing within an asymmetric processor architecture in which processors support different processor specific functionality. Instruction sets within processors having different functionalities are modified so that a portion of the functionality of these processors overlaps within a common set of instructions. Code generation for the multi-processor system (e.g., compiler, assembler, and / or linker) is performed in a manner to allow the binary code to be generated for execution on these diverse processors, and the execution of generic tasks, using the shared instructions, on any of the processors within the multiple processors. Processor specific tasks are only executed by the processors having the associated processor specific functionality. Source code directives are exemplified for aiding the compiler or assembler in properly creating binary code for the diverse processors. The invention can reduce processor computation requirements, reduce software latency, and increase system responsiveness.

Owner:SONY CORP +1

Systems and methods for asymmetric multiprocessing

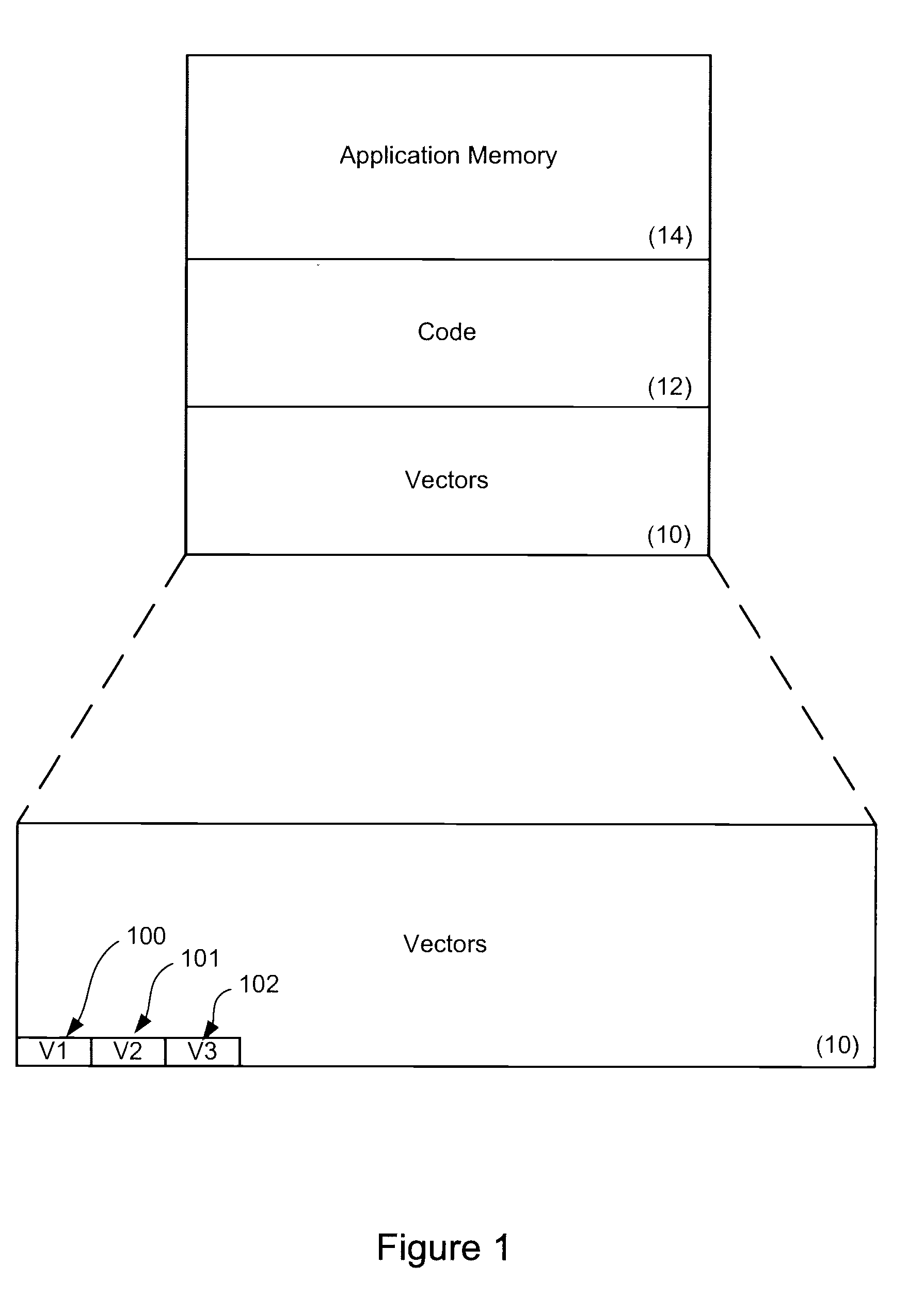

InactiveUS20090182980A1Memory adressing/allocation/relocationDigital computer detailsOperational systemDual core

Systems and methods are described for managing applications in a computer system. An operating system kernel such as Linux can be started and executed at different addresses other than the address typically used for such kernels. An operating system kernel can accommodate end of memory and size of memory that do not comply with normal system specifications. Mechanisms are described that change methods for exception vector handling using a software fix. Dual and / or multi-core systems can run applications in both SMP and ASMP modes without needing any hardware changes. Separate instances or similar copies of an OS such as Linux can be executed on multiple cores in ASMP mode. In SMP mode, Linux or another OS can run as a single instance of the OS.

Owner:BIVIO NETWORKS

Asymmetric multiprocessor

InactiveUS7814252B2Increase freedomLoad minimizationEnergy efficient ICTGeneral purpose stored program computerClock phaseComputer science

An asymmetric multiprocessor capable of increasing a degree of freedom of distributed processing, minimizing a processing load on each processor (CPU), and achieving a large reduction in power consumption by reducing an operating frequency or lowering the power supply voltage. An asymmetric multiprocessor includes a hardware resource mediator that mediates request signals requesting permission to use arbitrary hardware accelerators from CPU cores. A signal processing content selector selects signal processing content of a dynamically reconfigurable signal processor that is connected as a slave A clock skew mediator arbitrarily shifts a clock phase relationship among groups, while clock delay generators delay a clock signal based on a clock skew selection enable signal.

Owner:SOCIONEXT INC

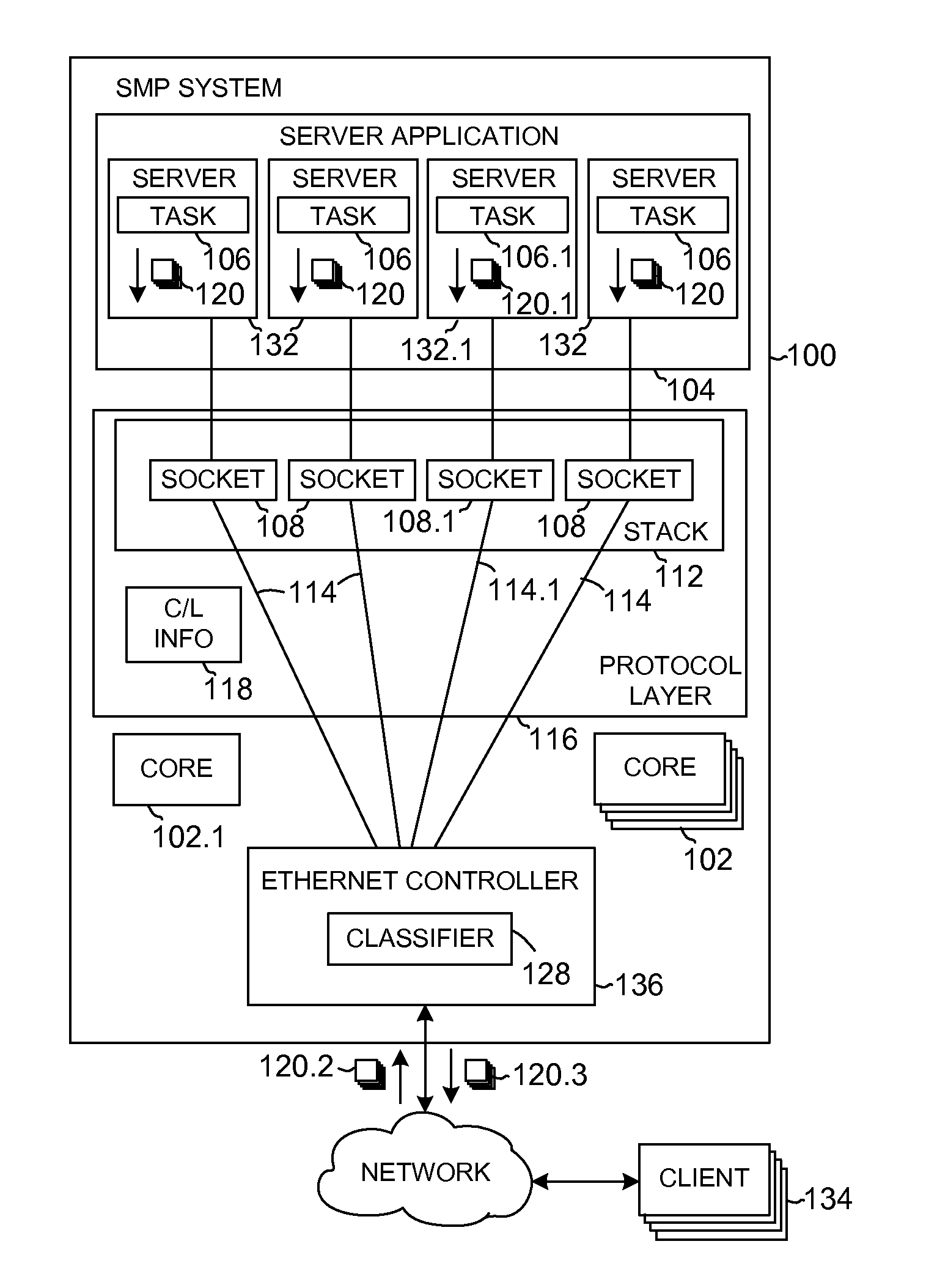

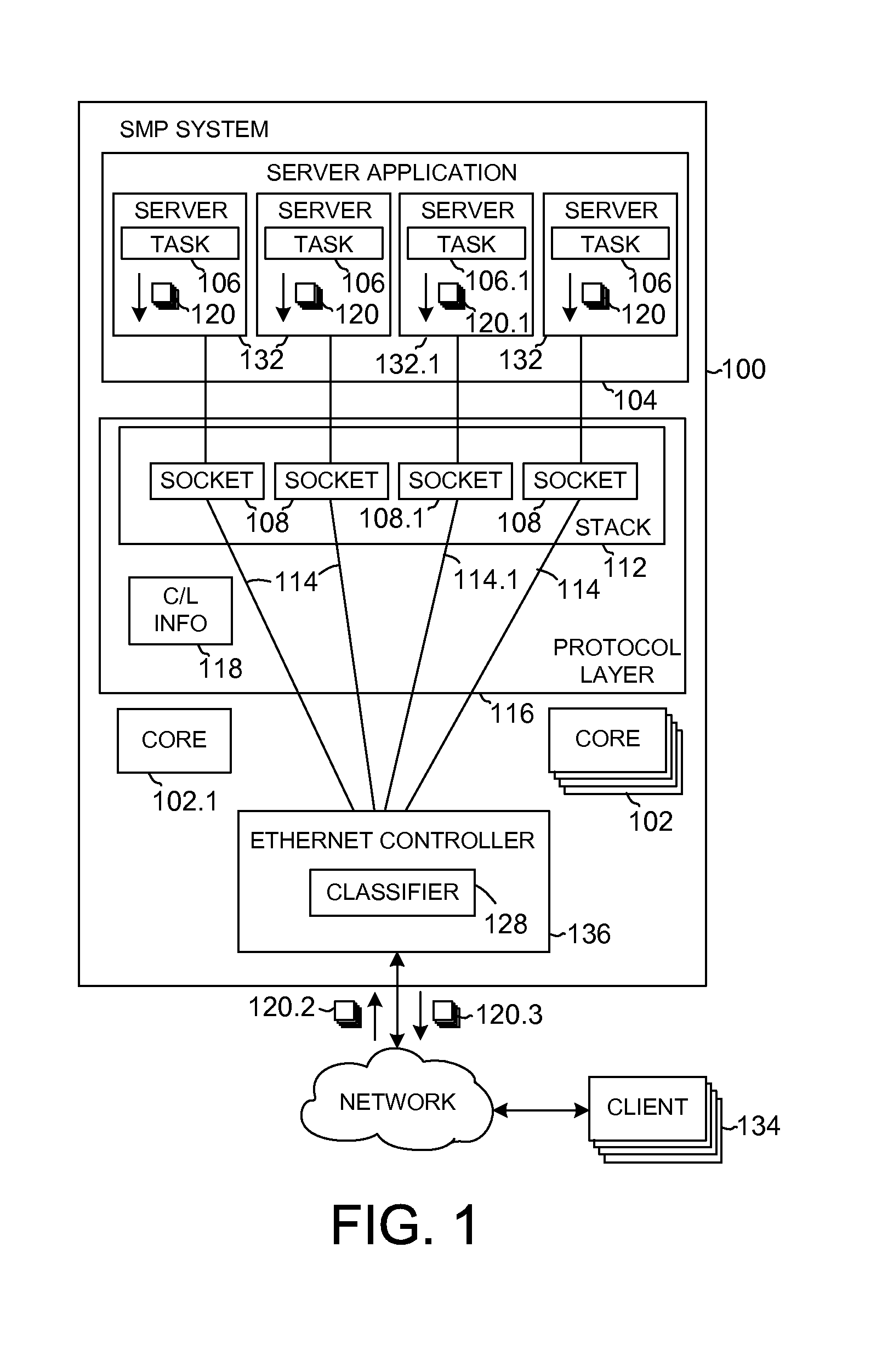

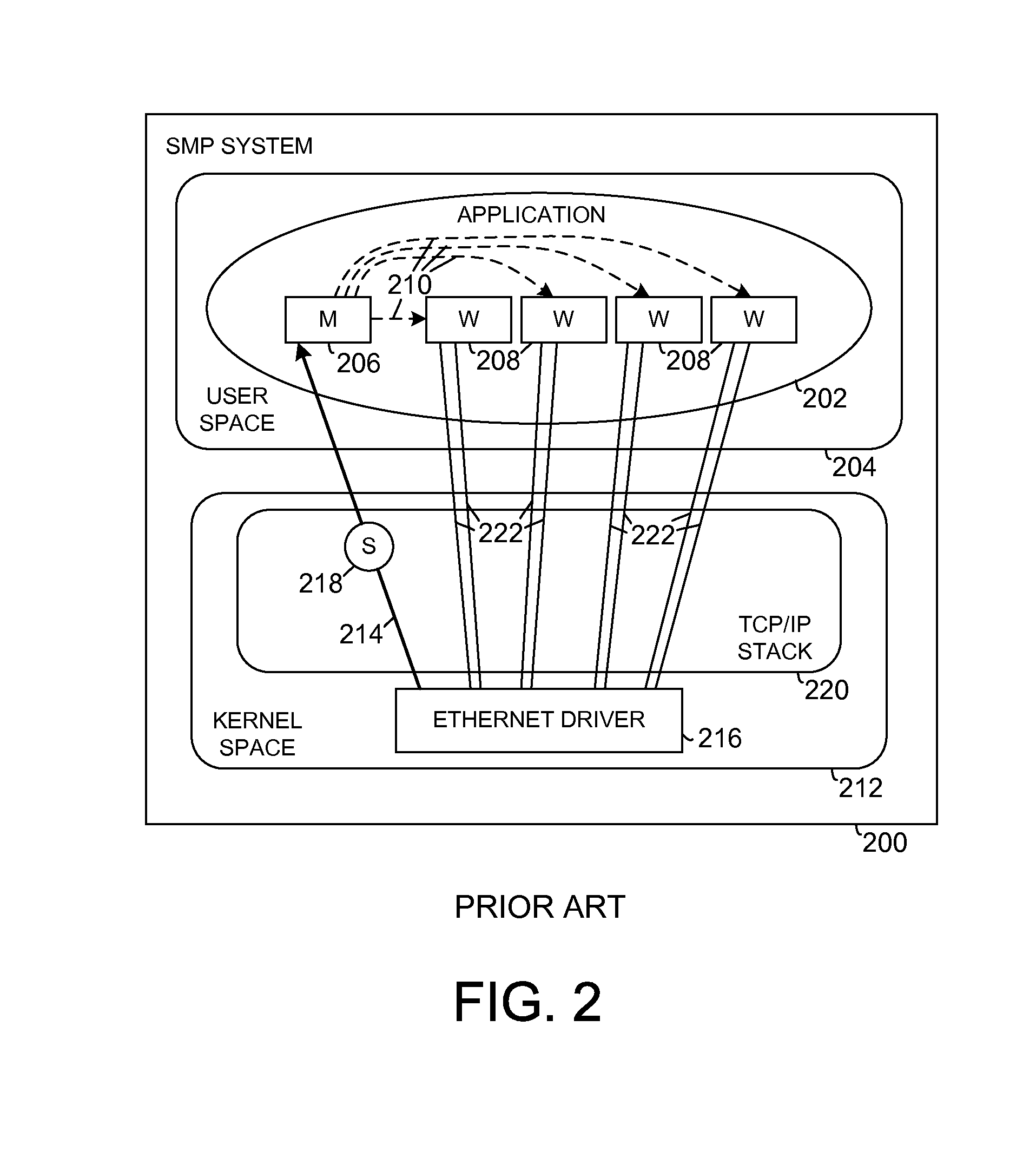

Core-affine processing on symmetric multiprocessing systems

ActiveUS20140019982A1Interprogram communicationMemory systemsProtocol processingSymmetric multiprocessing

Embodiments of a symmetric multi-processing (SMP) system can provide full affinity of a connection to a core processor when desired, even when ingress packet distribution, protocol processing layer and applications may autonomously process packets on different cores of the SMP system. In an illustrative embodiment, the SMP system can include a server application that is configured to create a plurality of tasks and bind the plurality of tasks to a plurality of core processors. One or more of the plurality of tasks are configured to create a corresponding listening endpoint socket, bind and listen on a protocol address that is common to the plurality of tasks.

Owner:NXP USA INC

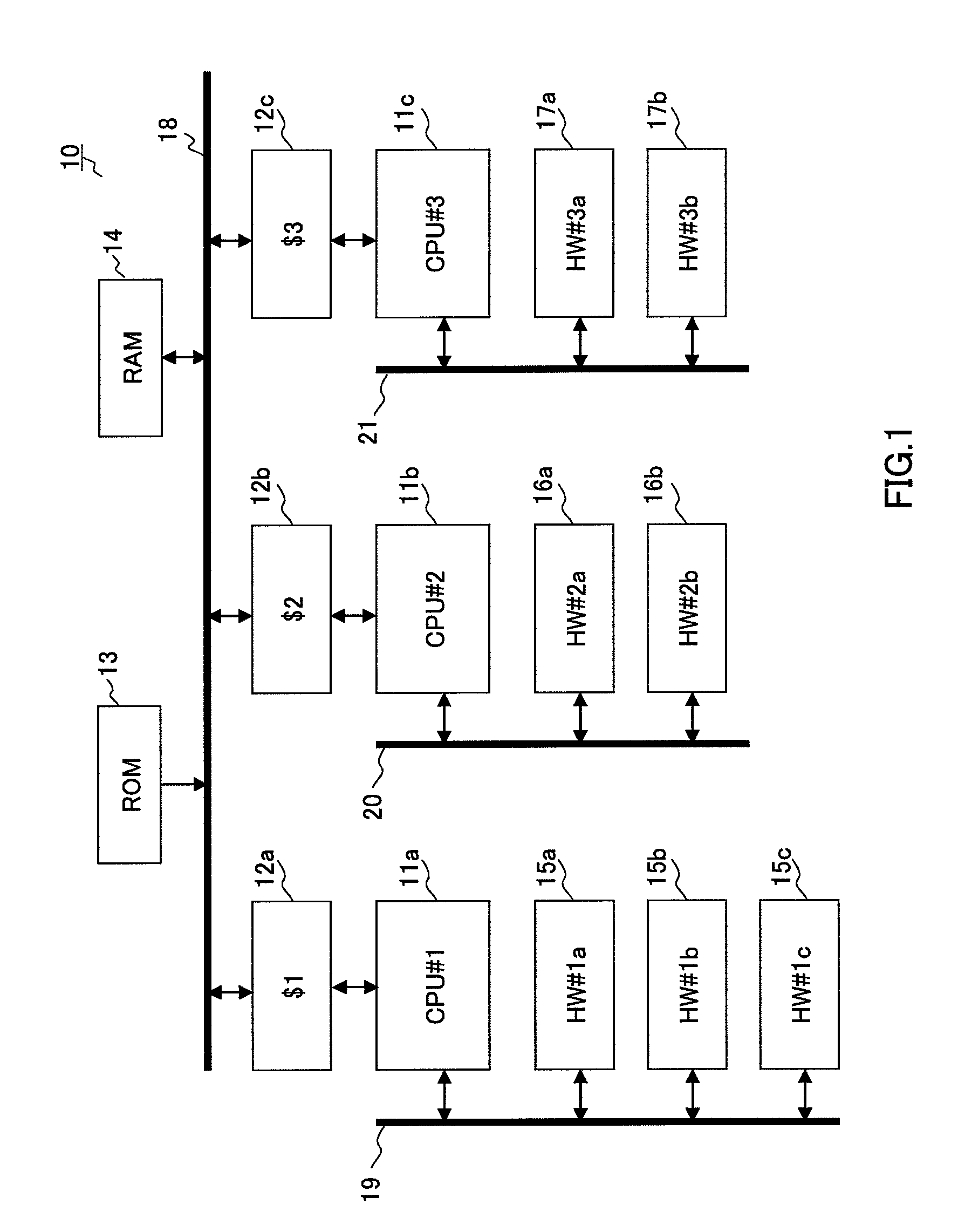

System And Method for Enhanced Updating Layer-2 Bridge Address Table on Asymmetric Multiprocessing Systems

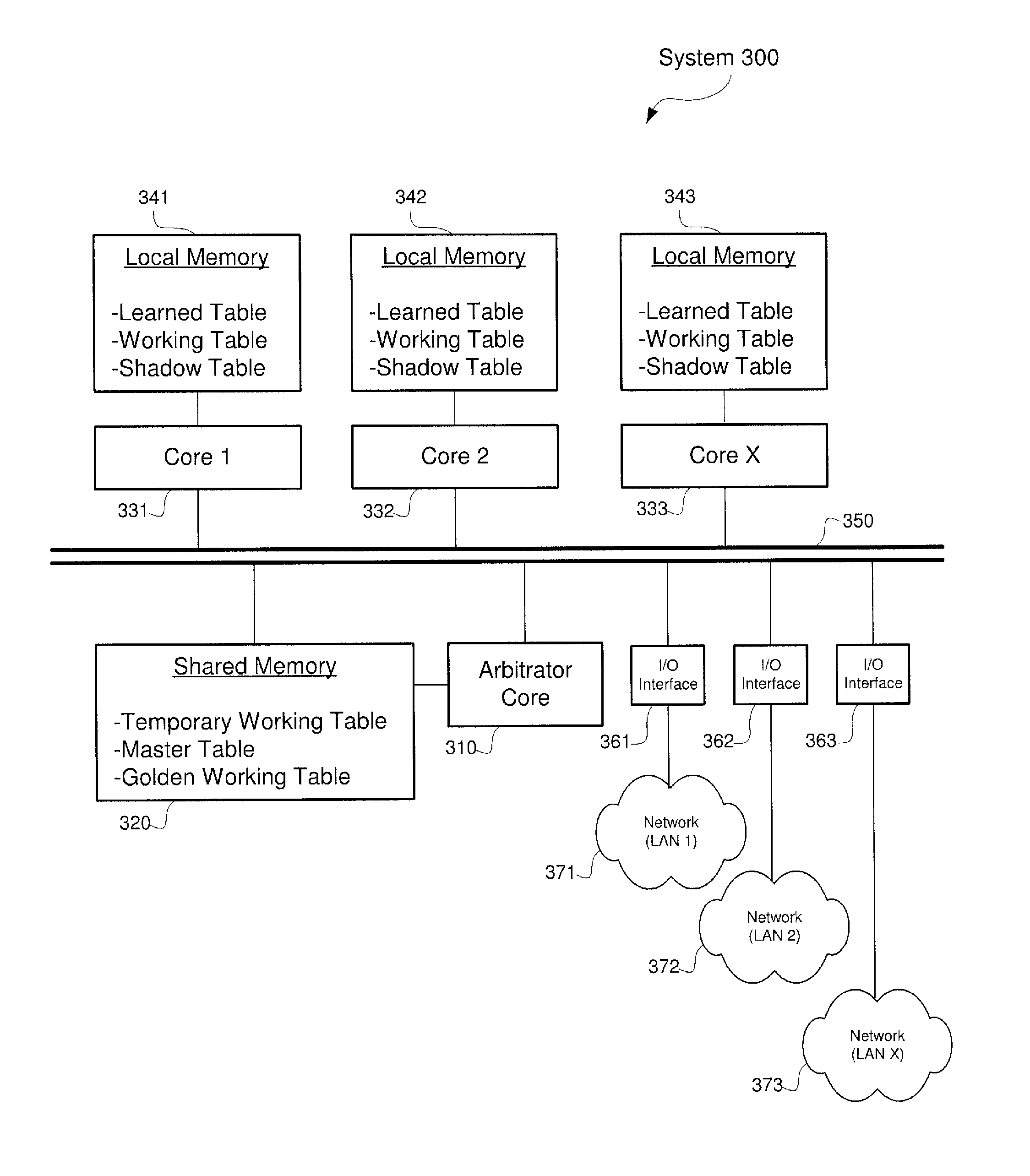

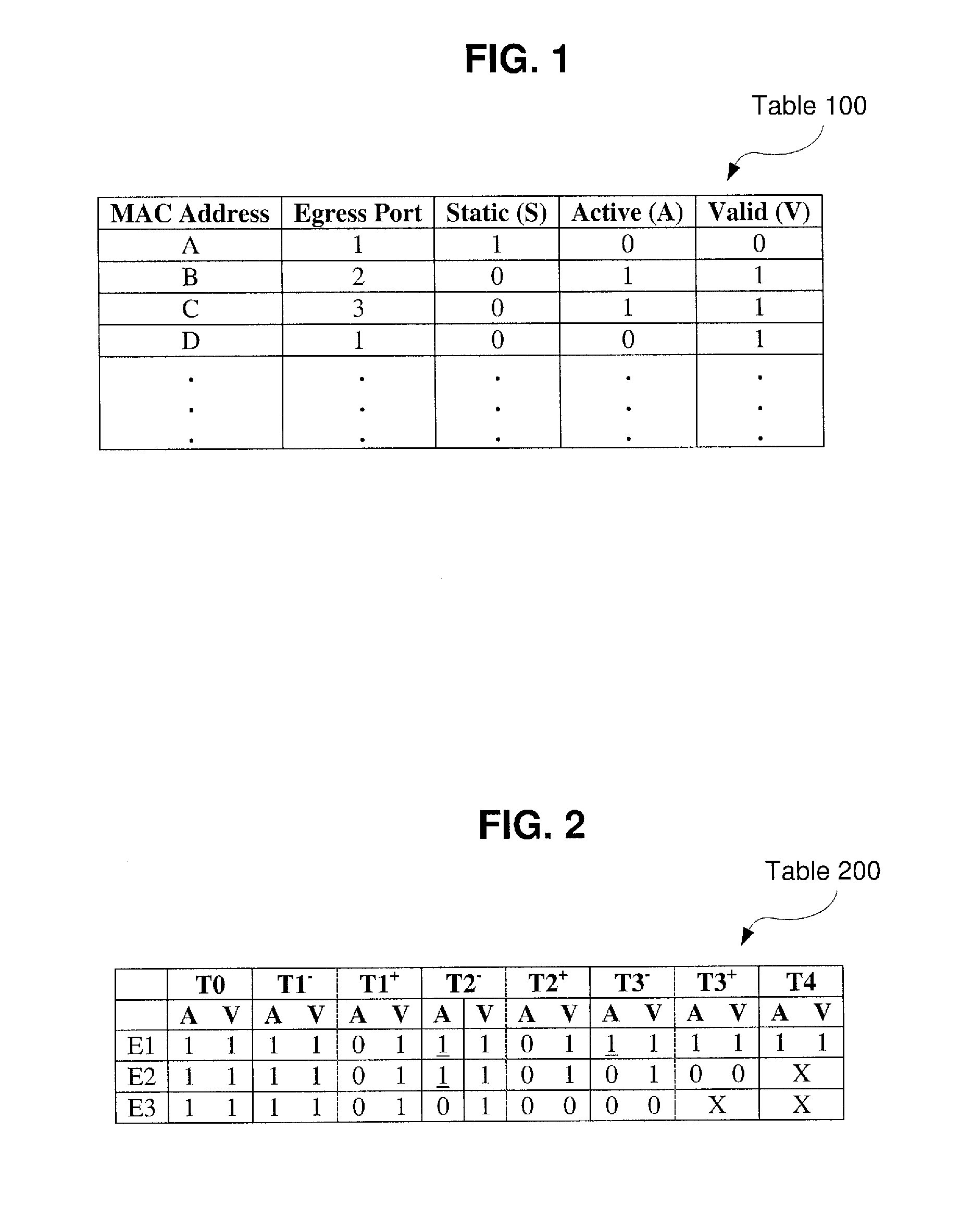

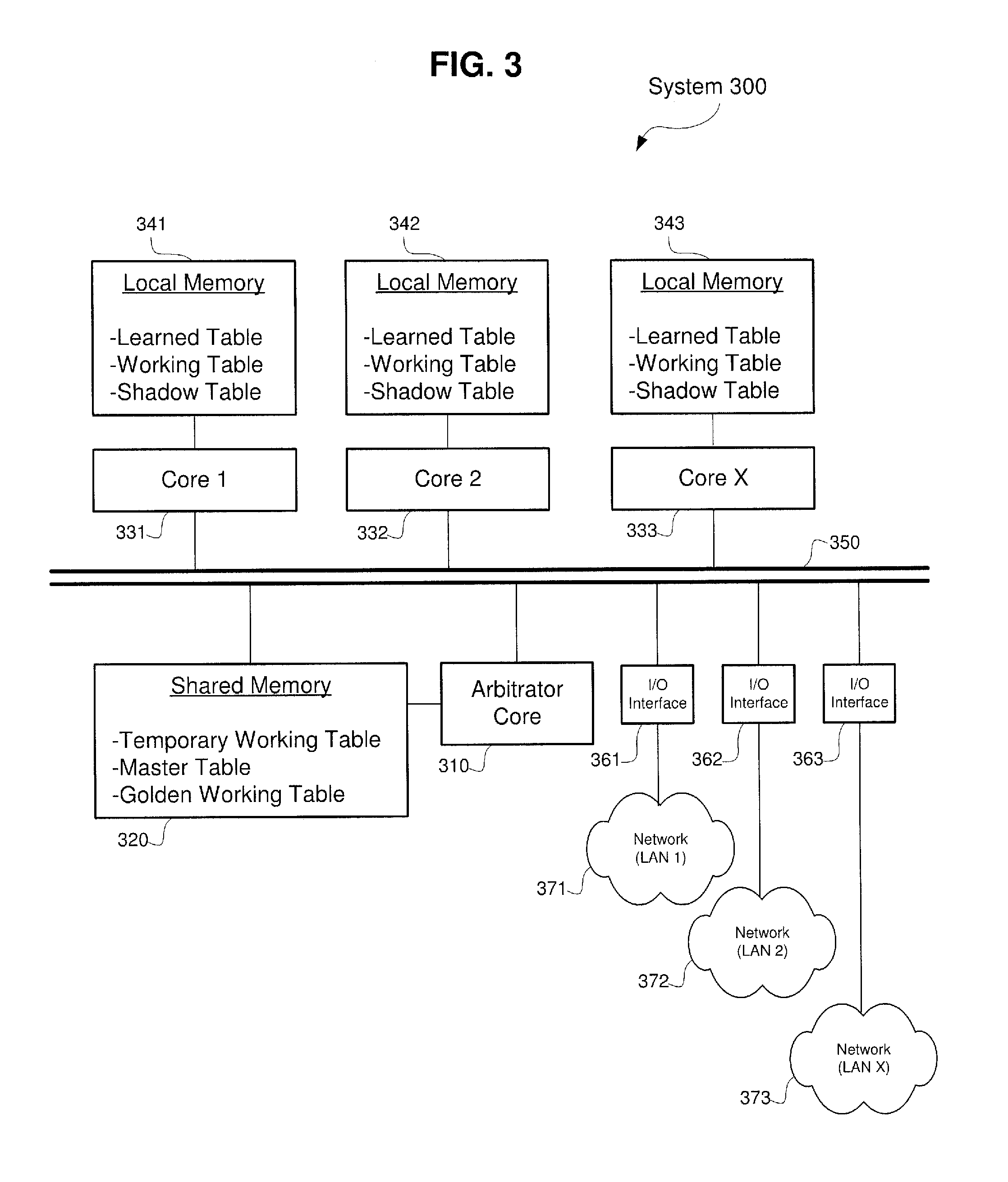

InactiveUS20130250965A1Improve bridgingSimple processData switching by path configurationOperating systemLocal memories

The exemplary embodiments described herein relate to systems and methods for optimizing the aging and learning processes. One embodiment relates to a system comprising a shared memory, a plurality of forwarding cores in communication with the shared memory, wherein each forwarding core includes a local memory, and an arbitrator core in communication with the forwarding cores and the shared memory, wherein the arbitrator core receives forwarding information from a plurality of forwarding cores, wherein each of the forwarding cores includes a local memory storing local forwarding tables, synchronizes the forwarding information from each of the local forwarding tables to generate a temporary working table, sorts the temporary working table into a predetermined array, generates a master forwarding table from the temporary working table, and distributes the master forwarding table to each of the forwarding cores.

Owner:WIND RIVER SYSTEMS

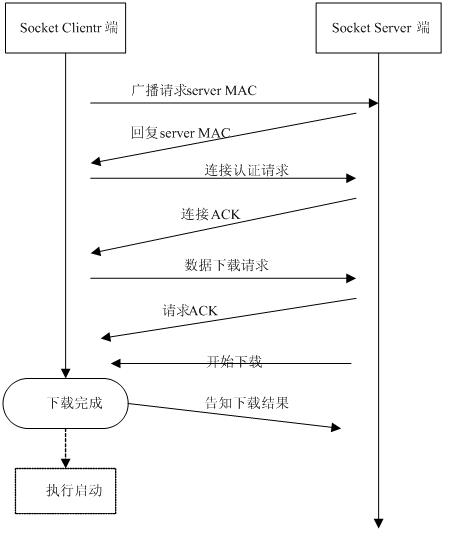

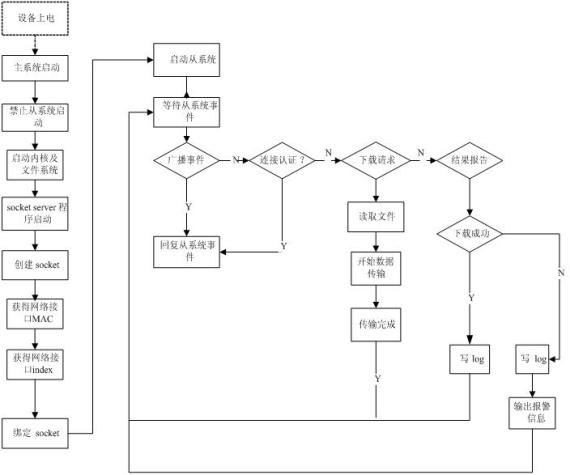

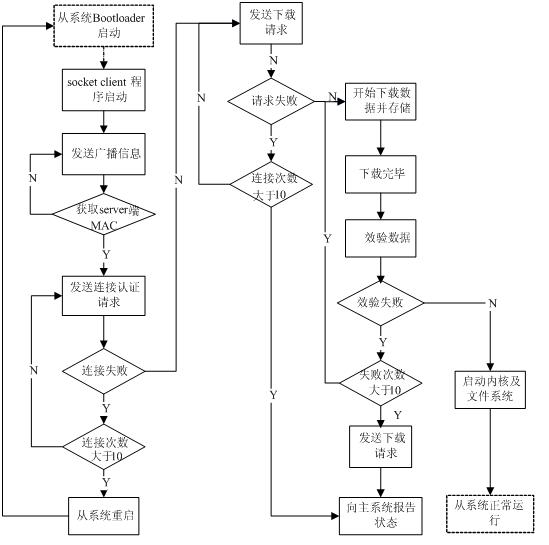

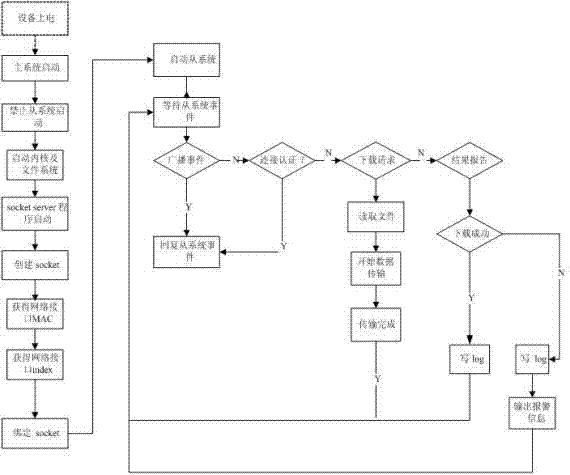

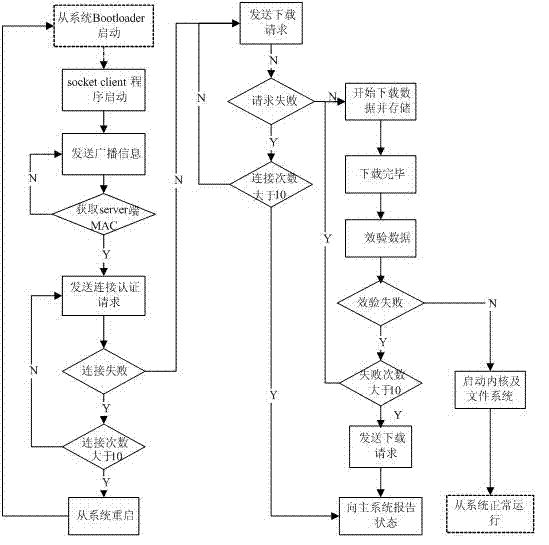

Software loading and storing method under embedded asymmetric multiprocessing architecture

ActiveCN102637134AReduce hardware costsIncrease flexibilityFault responseProgram loading/initiatingFile systemAsymmetric multiprocessing

The invention relates to a software loading and storing method under an embedded asymmetric multiprocessing architecture. In an asymmetric multiprocessing system, one system is used as a main system, and other systems are used as slave systems; the main system and the slave systems respectively use distributed and centralized storage modes, and the slave systems are used as a start storage region for storing a Bootloader; a system kernel and a file system both are stored in the main system; the main system uses a NANDflash as a memory, the system software is loaded in a master-slave mode, and the software loading of the slave systems is controlled by the main system; and the slave systems download the kernel and the file system dynamically from the main system, and automatically load the downloaded kernel and file system after downloading. By virtue of the method for software storage and loading of the main system and the slave systems, the flexibility, stability and reliability of the system are enhanced, and the hardware cost of the complete machine is also saved.

Owner:网经科技(苏州)有限公司

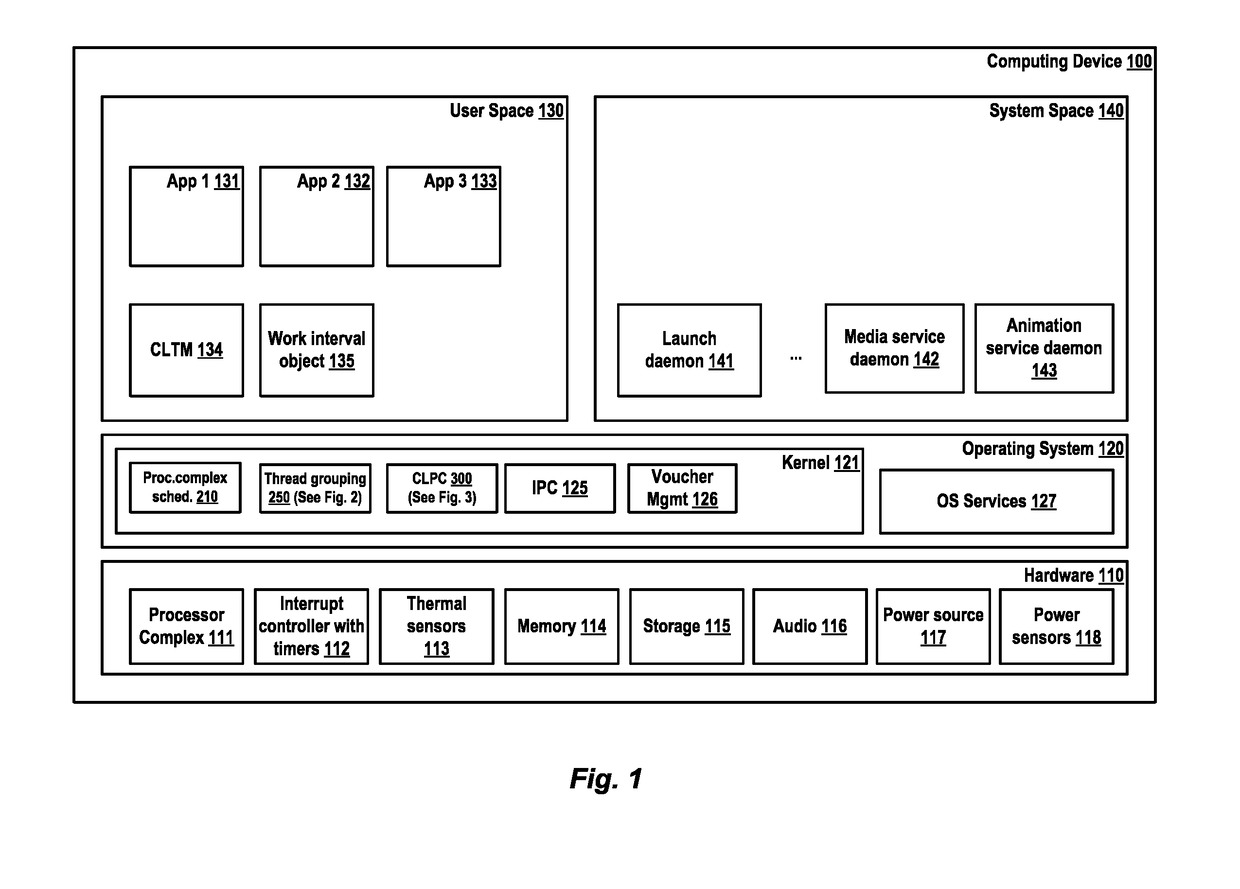

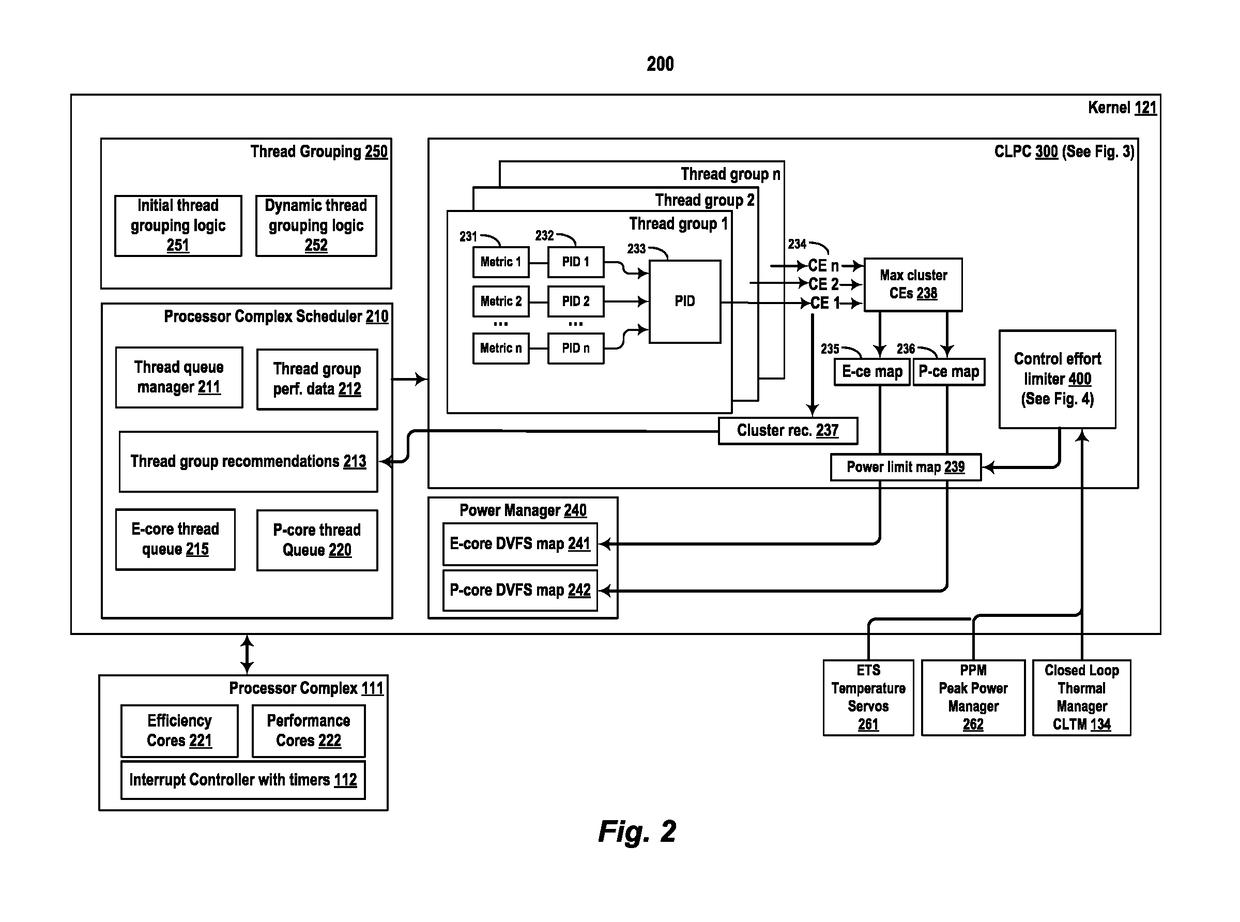

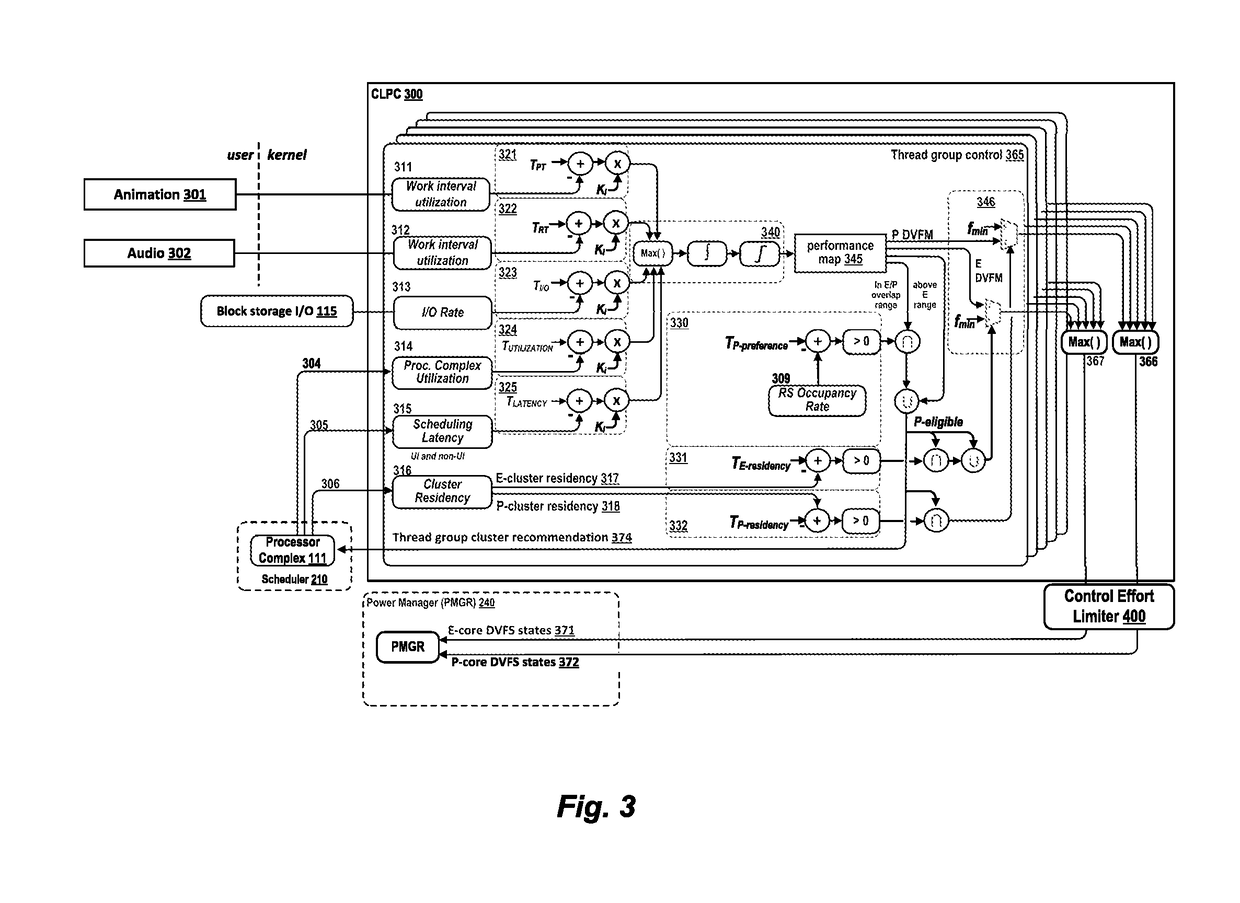

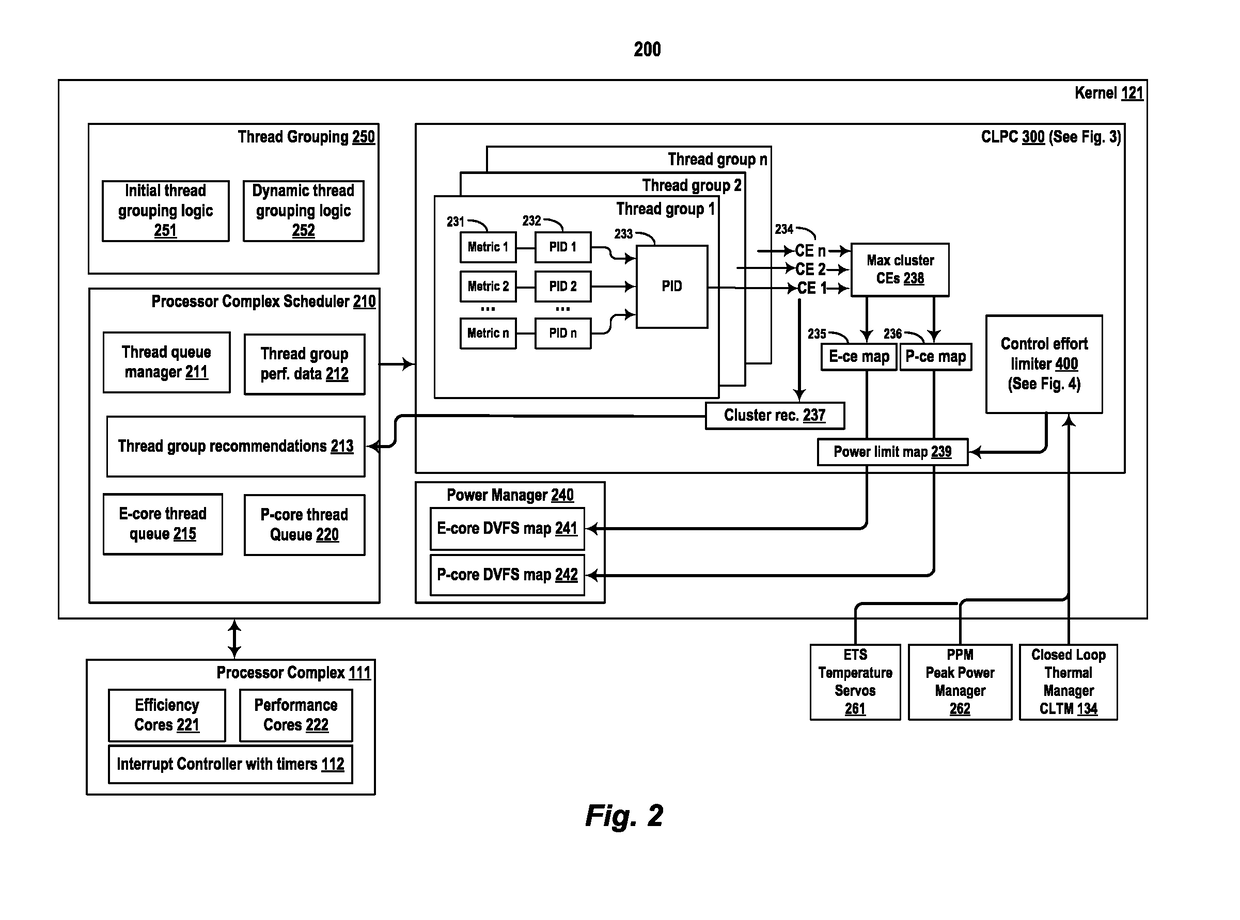

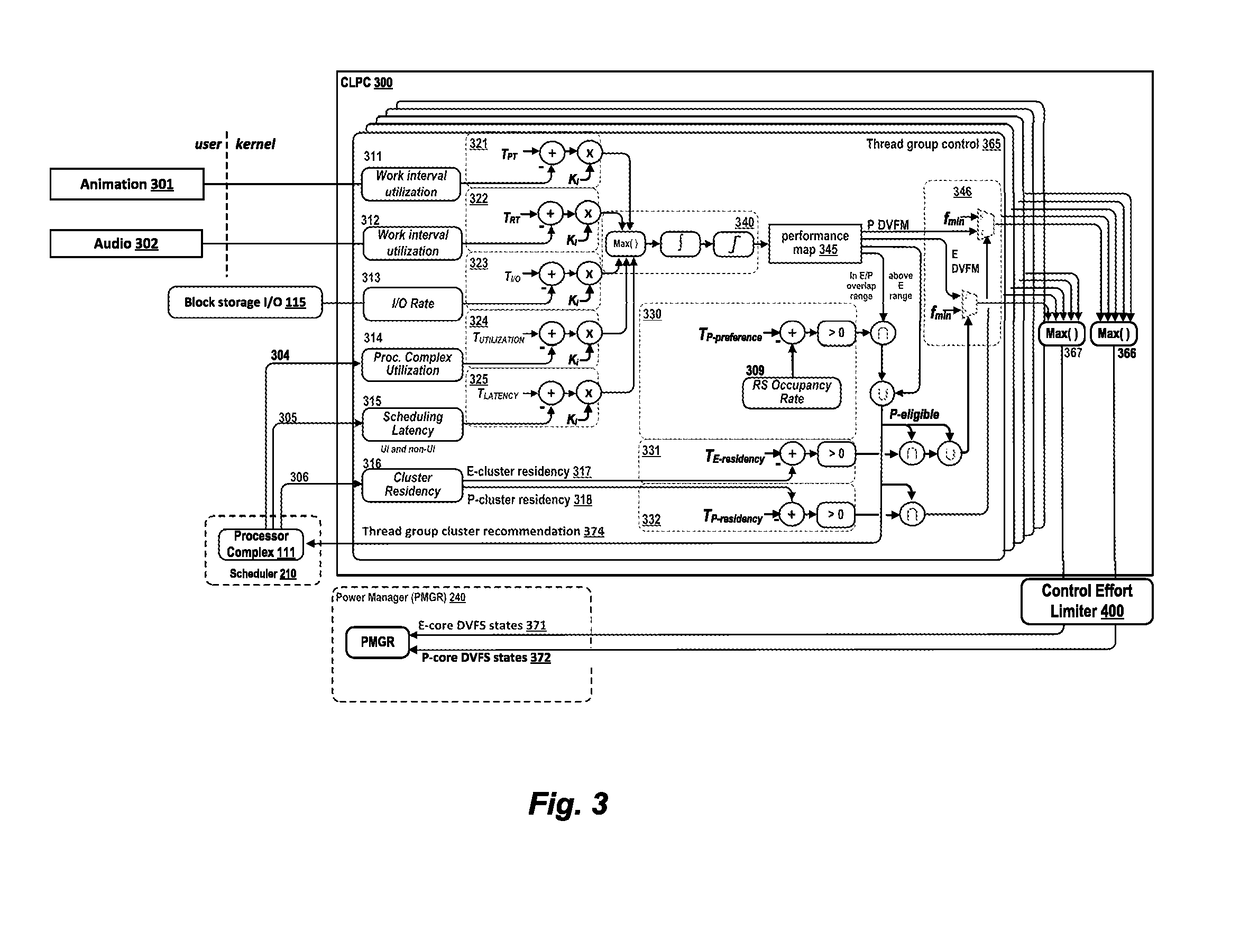

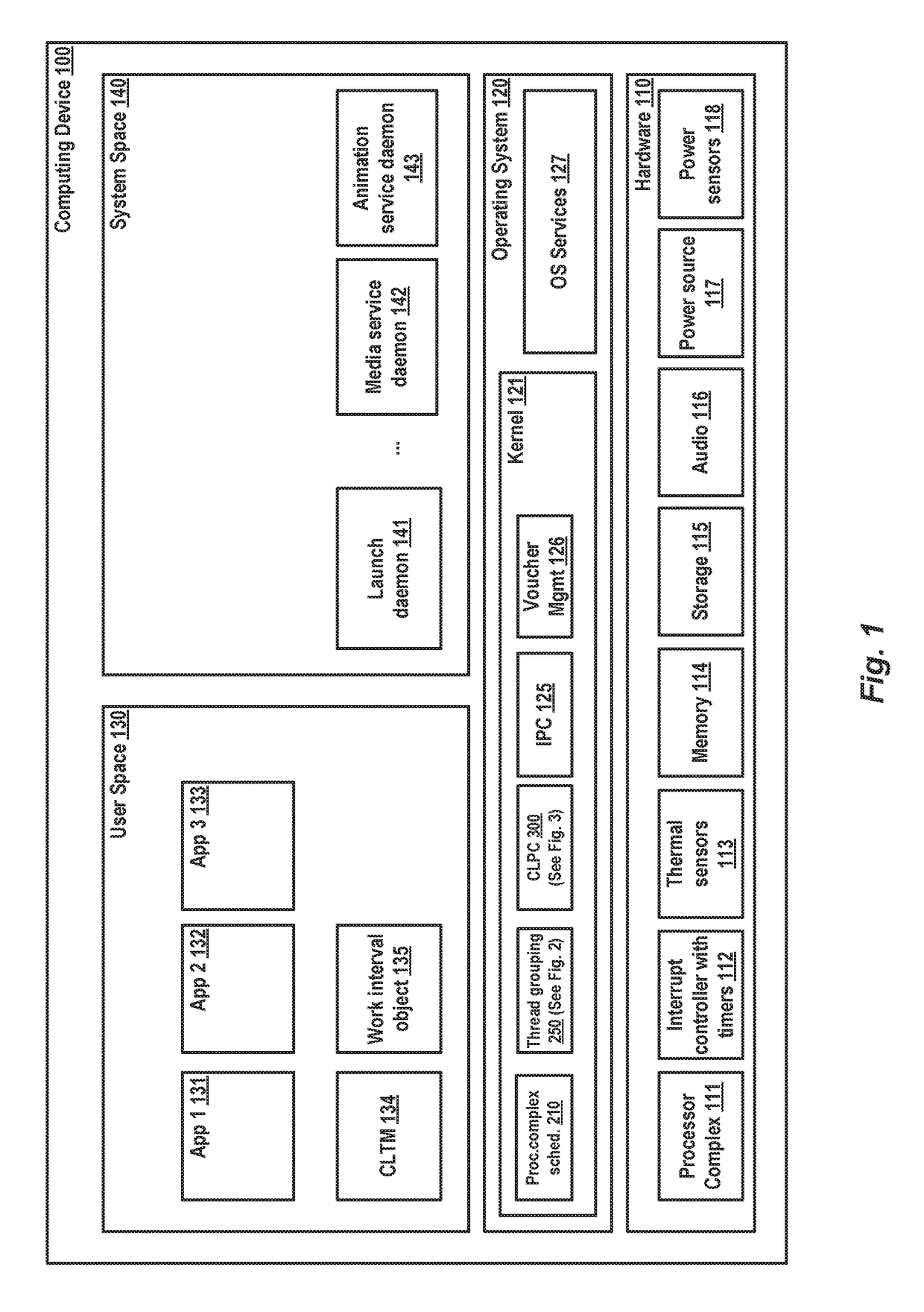

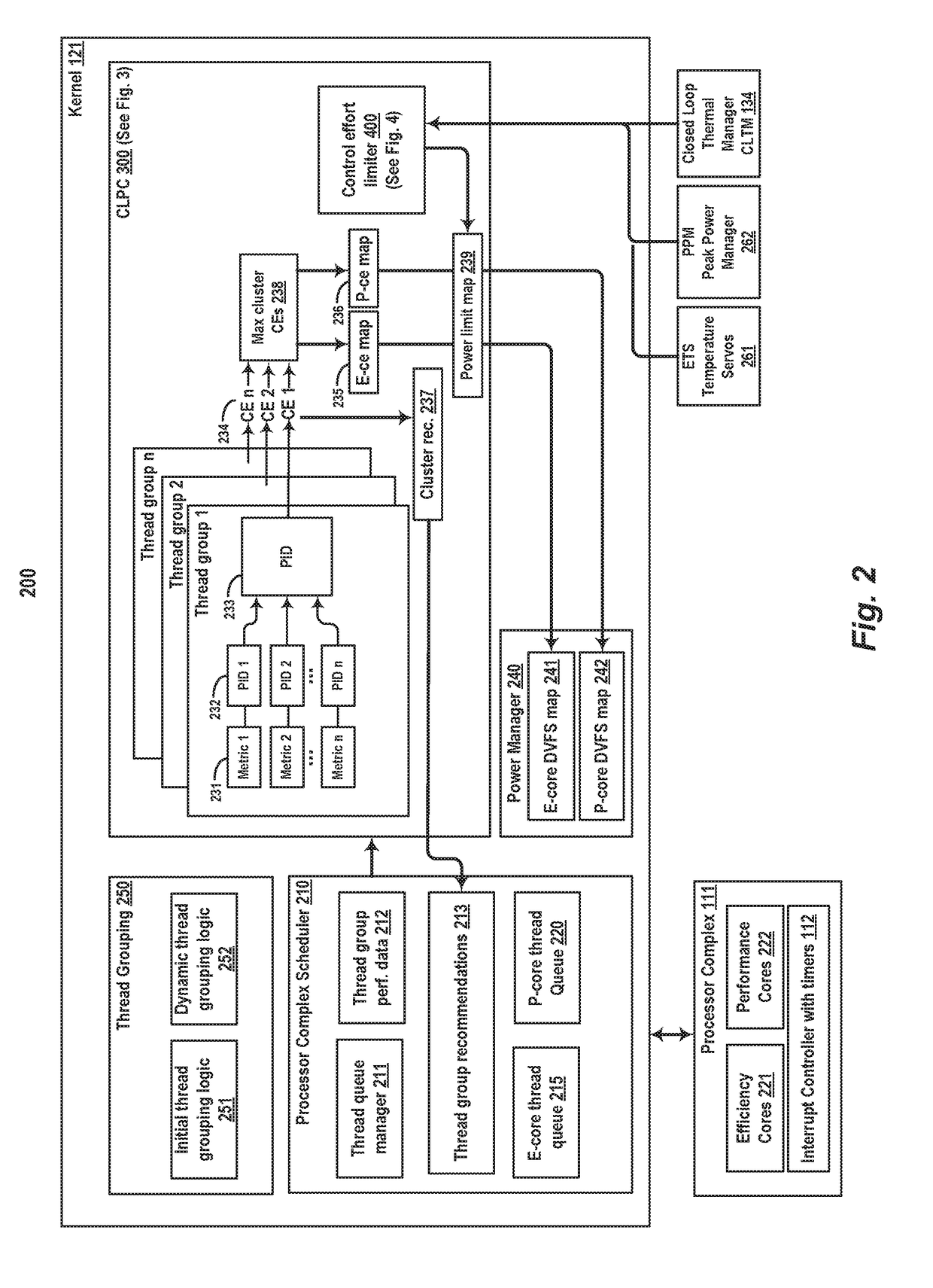

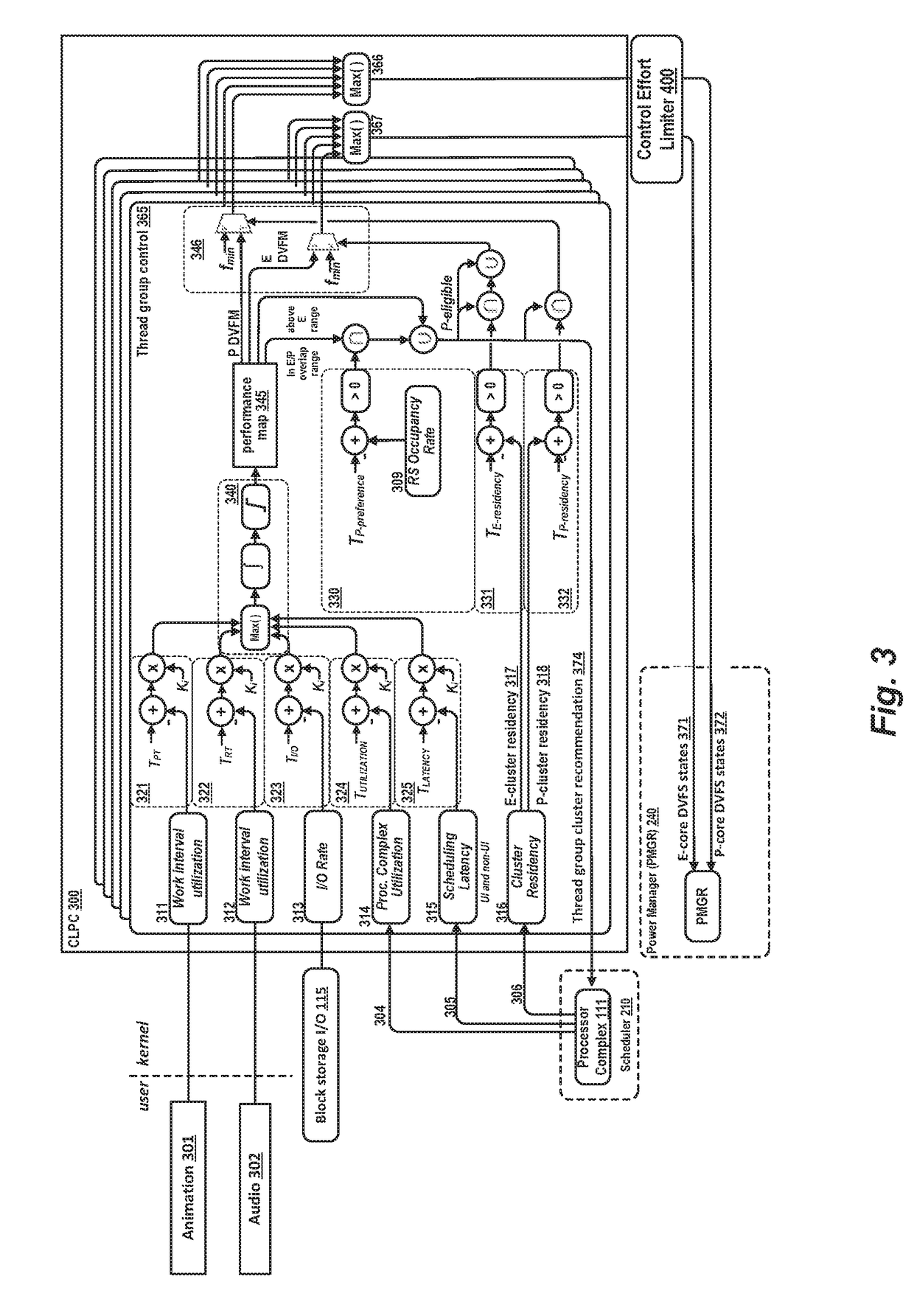

Scheduler for amp architecture using a closed loop performance and thermal controller

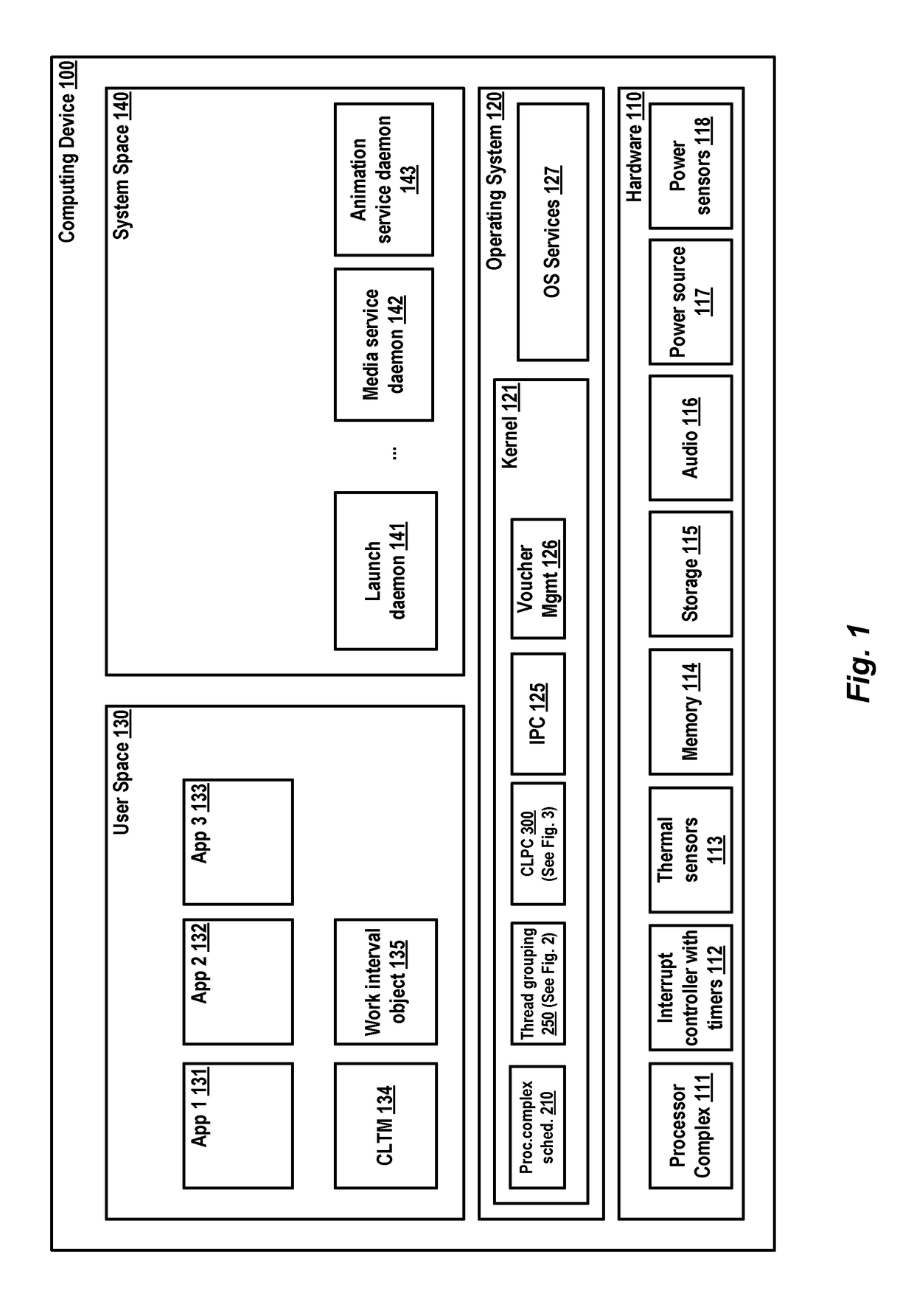

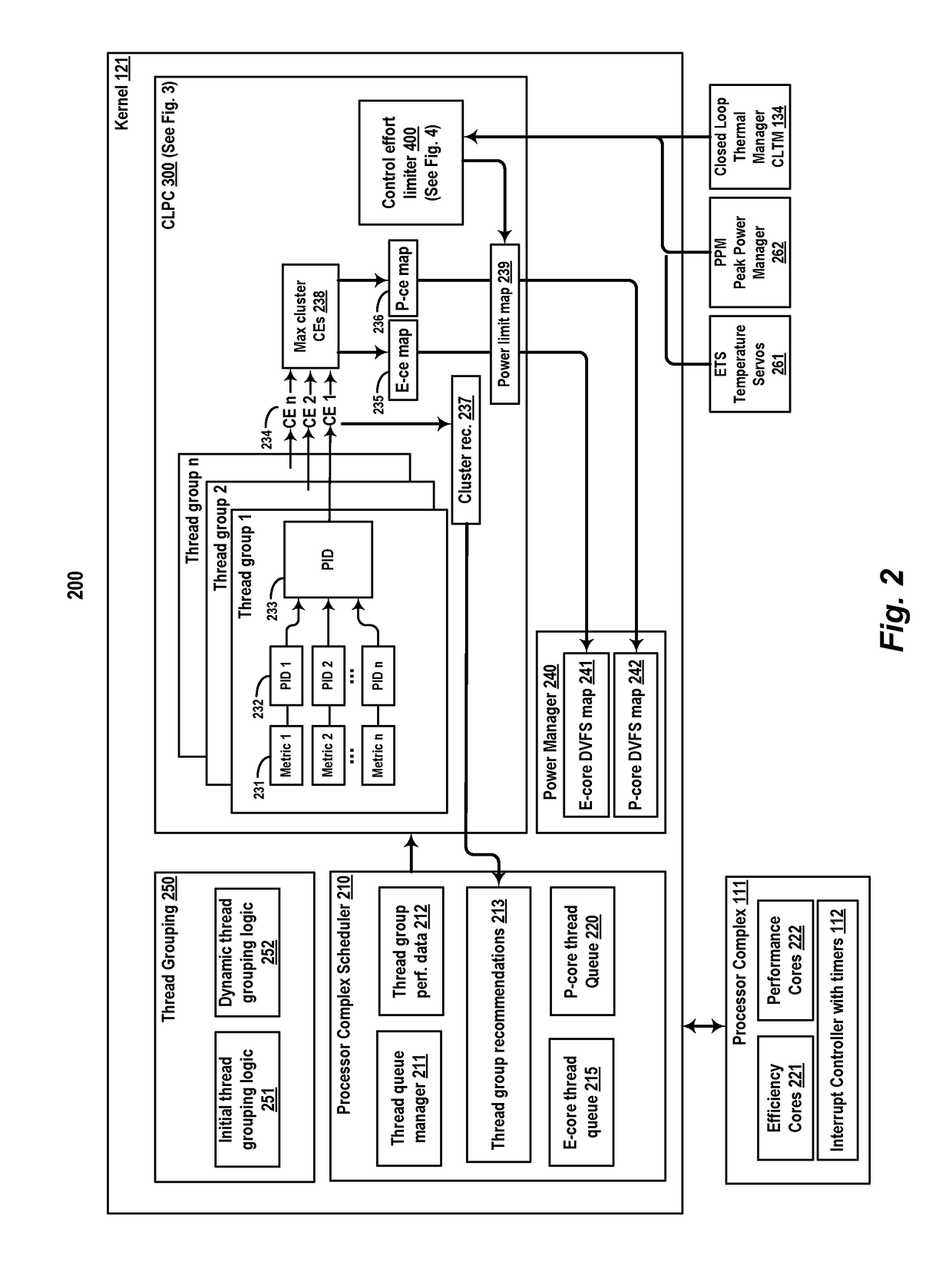

ActiveUS20180349175A1Minimizing thread scheduling latencyMaximize throughputProgram initiation/switchingResource allocationAudio power amplifierClosed loop

Systems and methods are disclosed for scheduling threads on a processor that has at least two different core types, such as an asymmetric multiprocessing system. Each core type can run at a plurality of selectable voltage and frequency scaling (DVFS) states. Threads from a plurality of processes can be grouped into thread groups. Execution metrics are accumulated for threads of a thread group and fed into a plurality of tunable controllers for the thread group. A closed loop performance control (CLPC) system determines a control effort for the thread group and maps the control effort to a recommended core type and DVFS state. A closed loop thermal and power management system can limit the control effort determined by the CLPC for a thread group, and limit the power, core type, and DVFS states for the system. Deferred interrupts can be used to increase performance.

Owner:APPLE INC

Scheduler for AMP Architecture with Closed Loop Performance Controller Using Static and Dynamic Thread Grouping

ActiveUS20180349186A1Minimizing thread scheduling latencyMaximize throughputProgram initiation/switchingResource allocationClosed loopParallel computing

Owner:APPLE INC

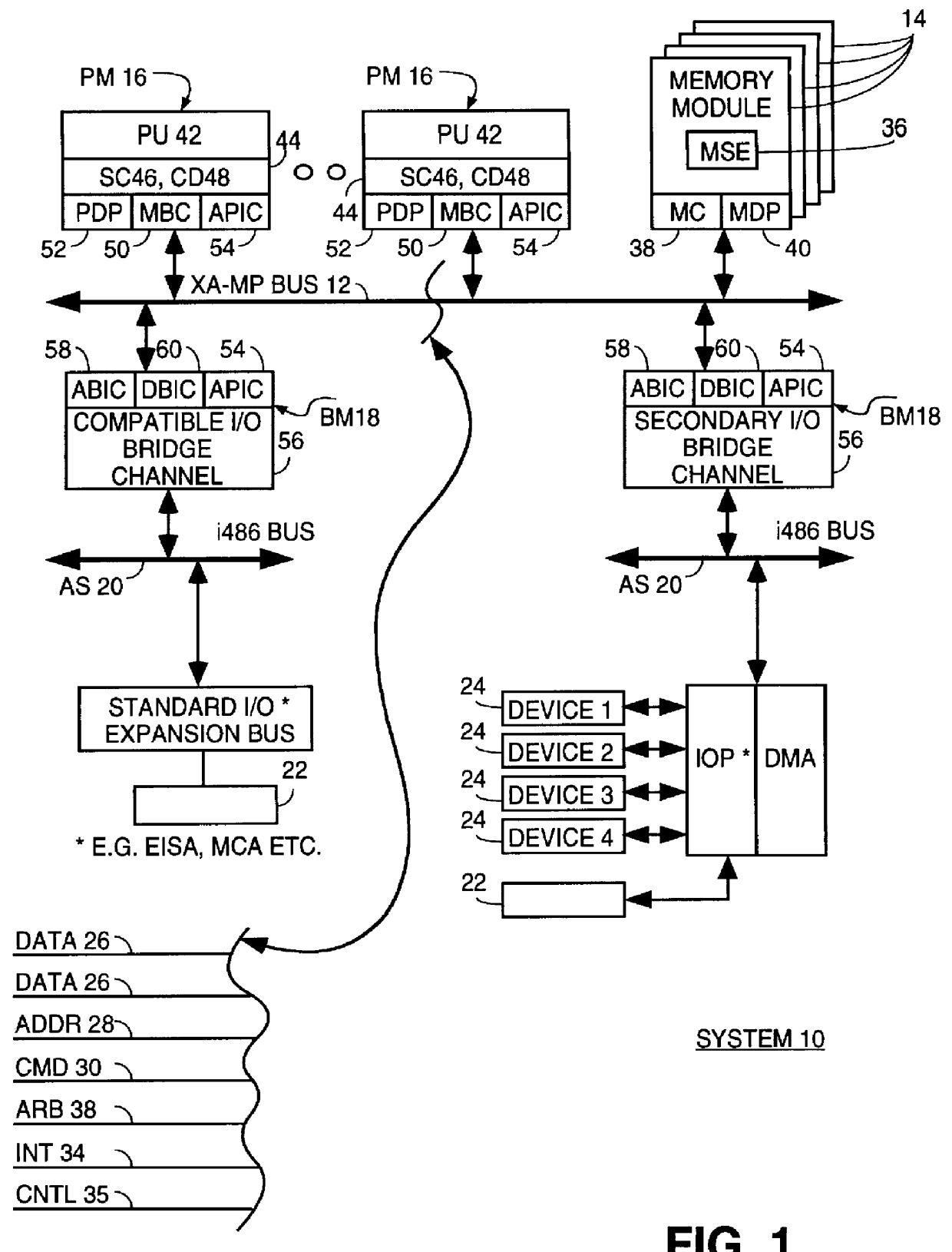

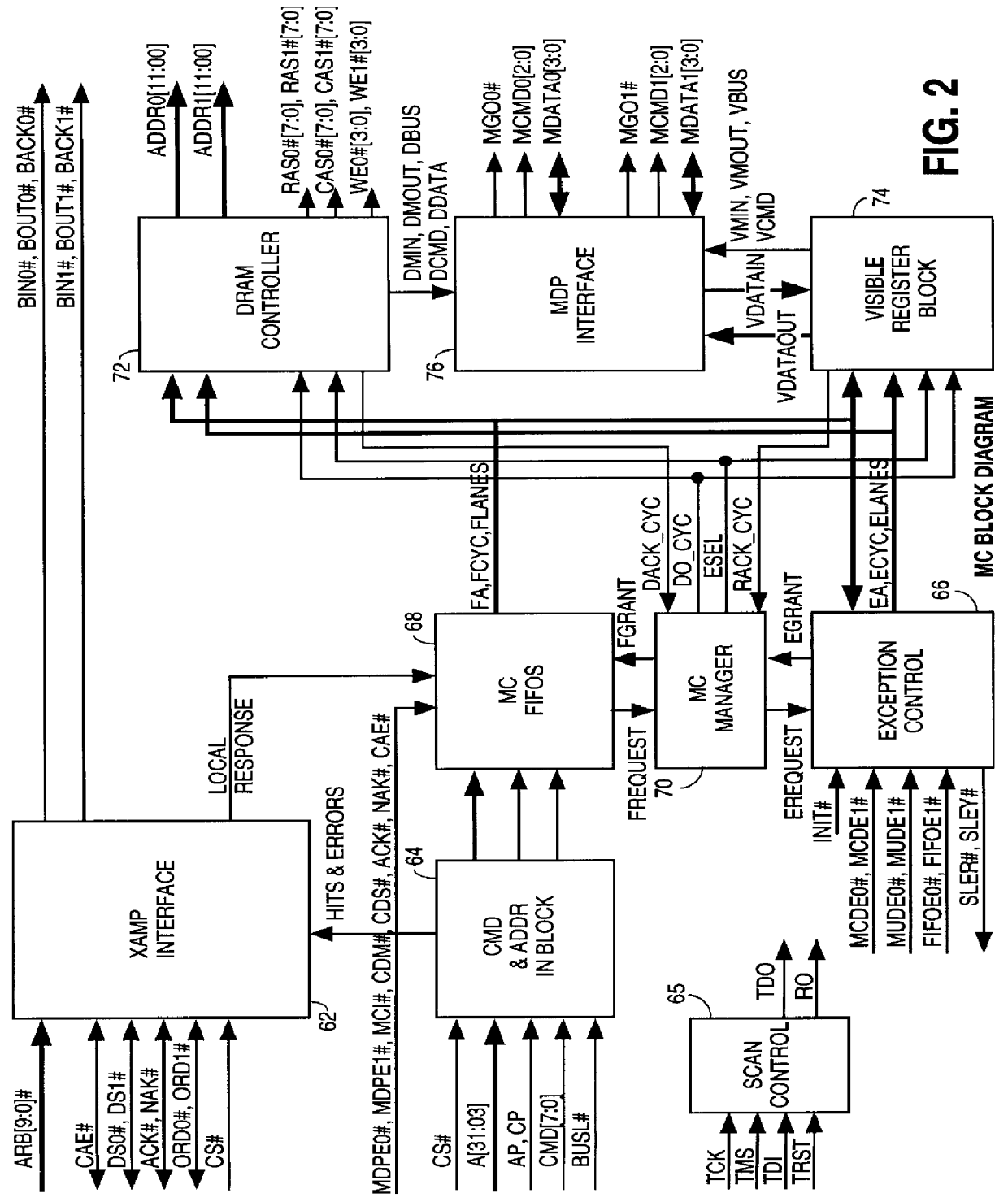

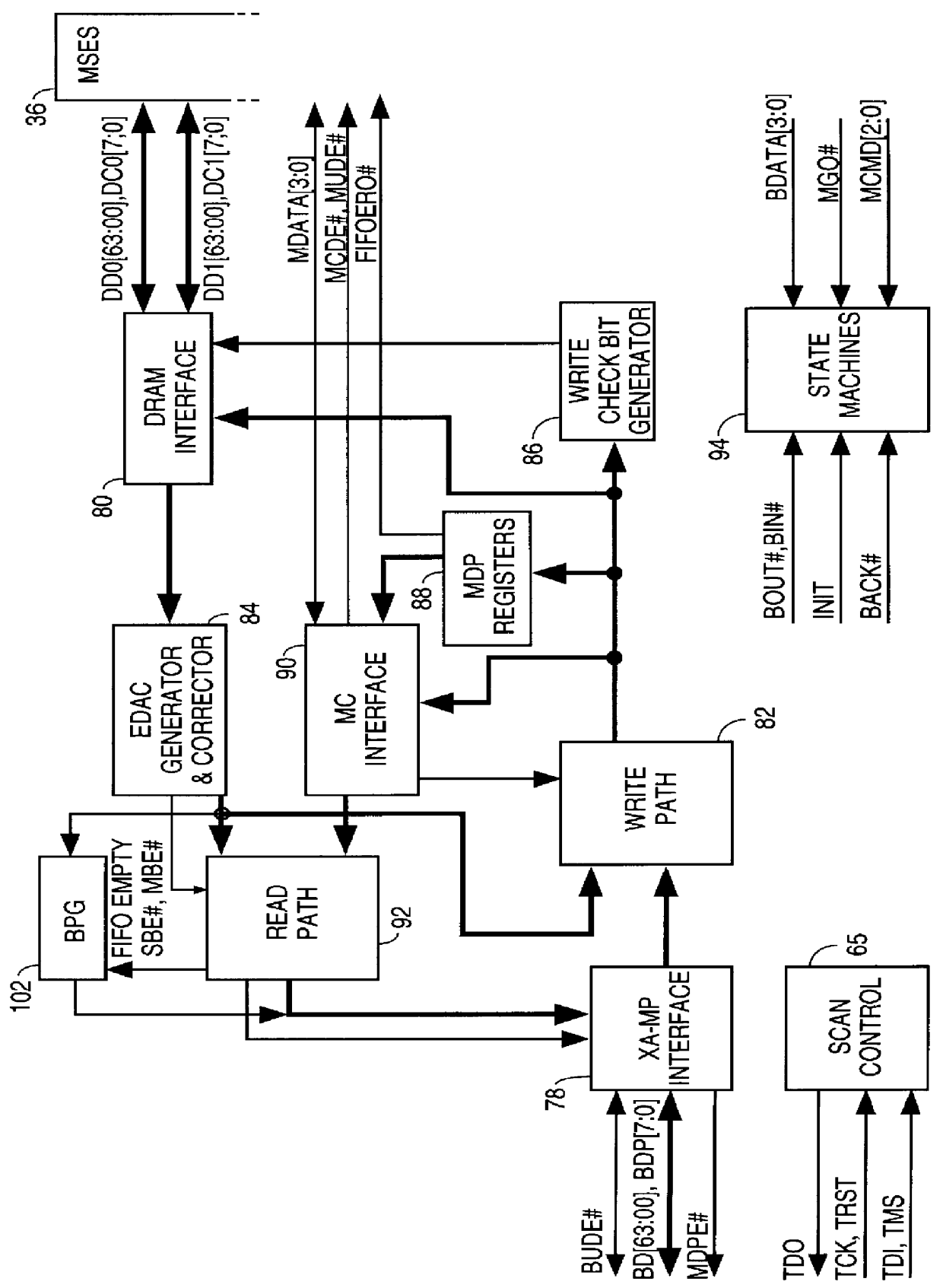

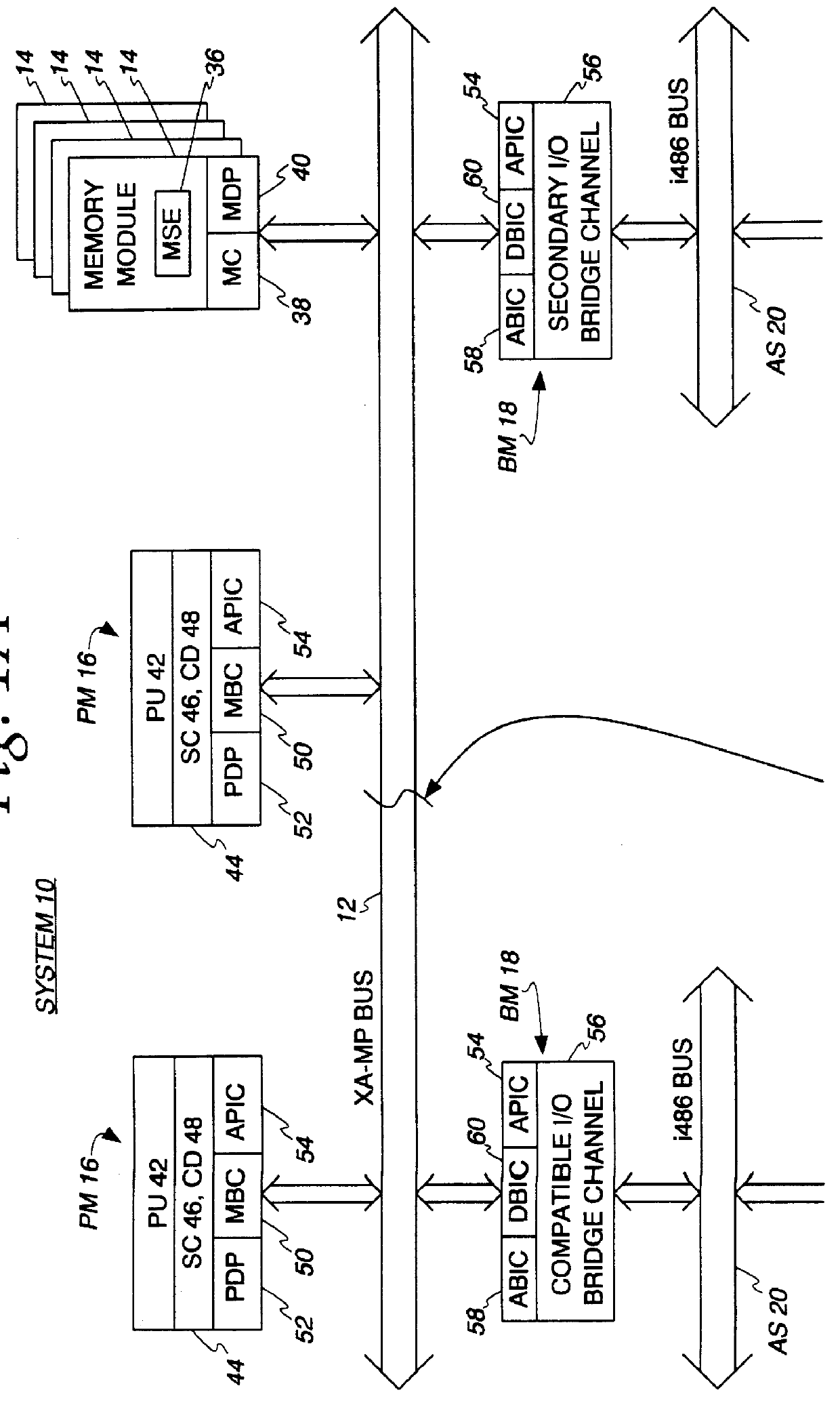

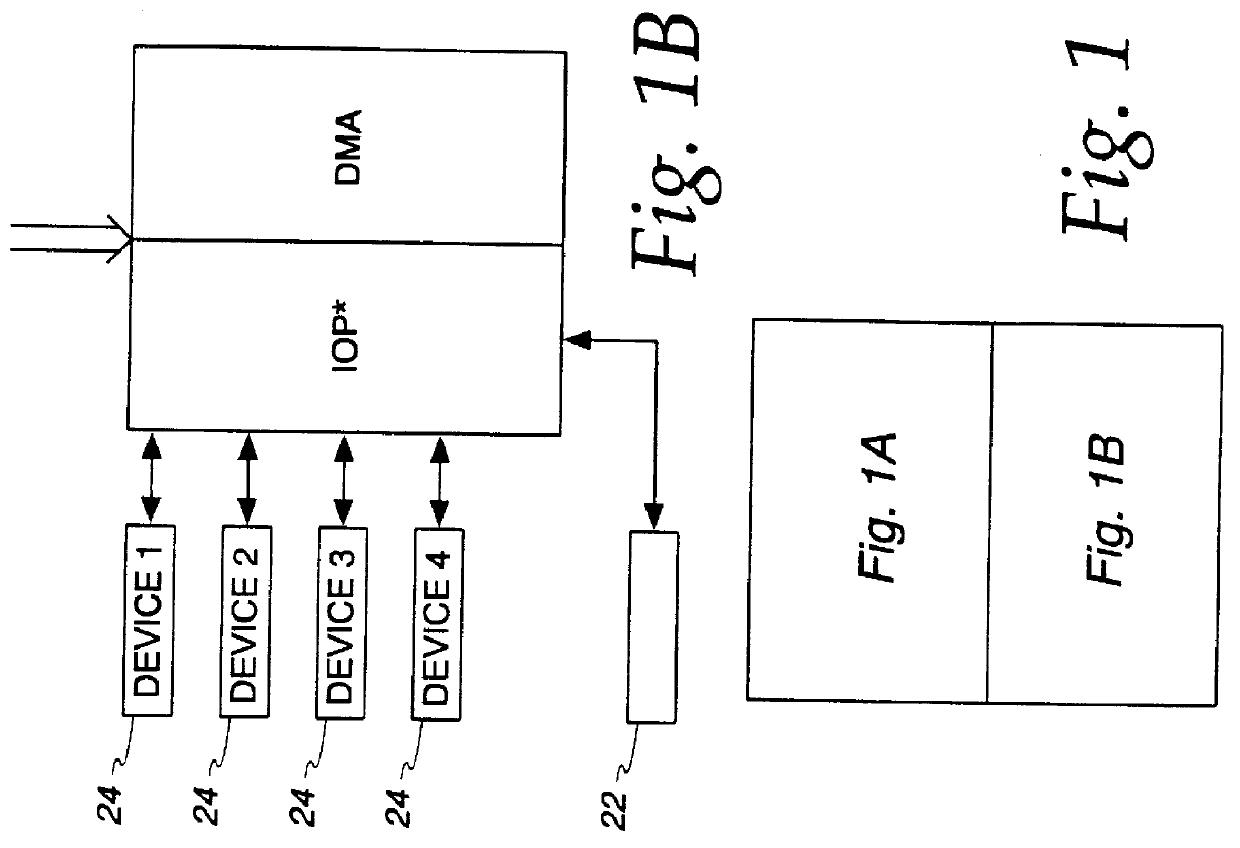

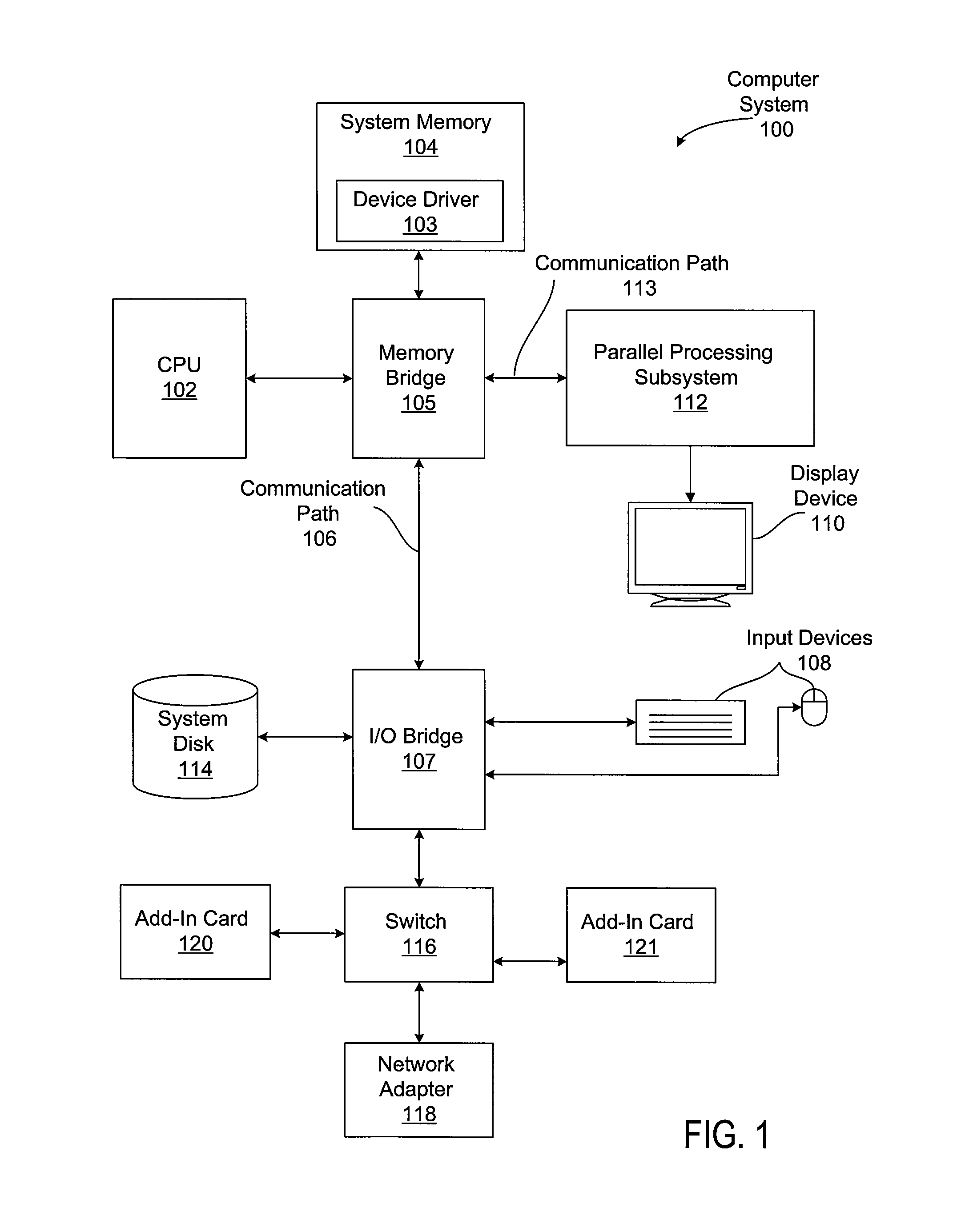

Symmetric multiprocessing system with unified environment and distributed system functions

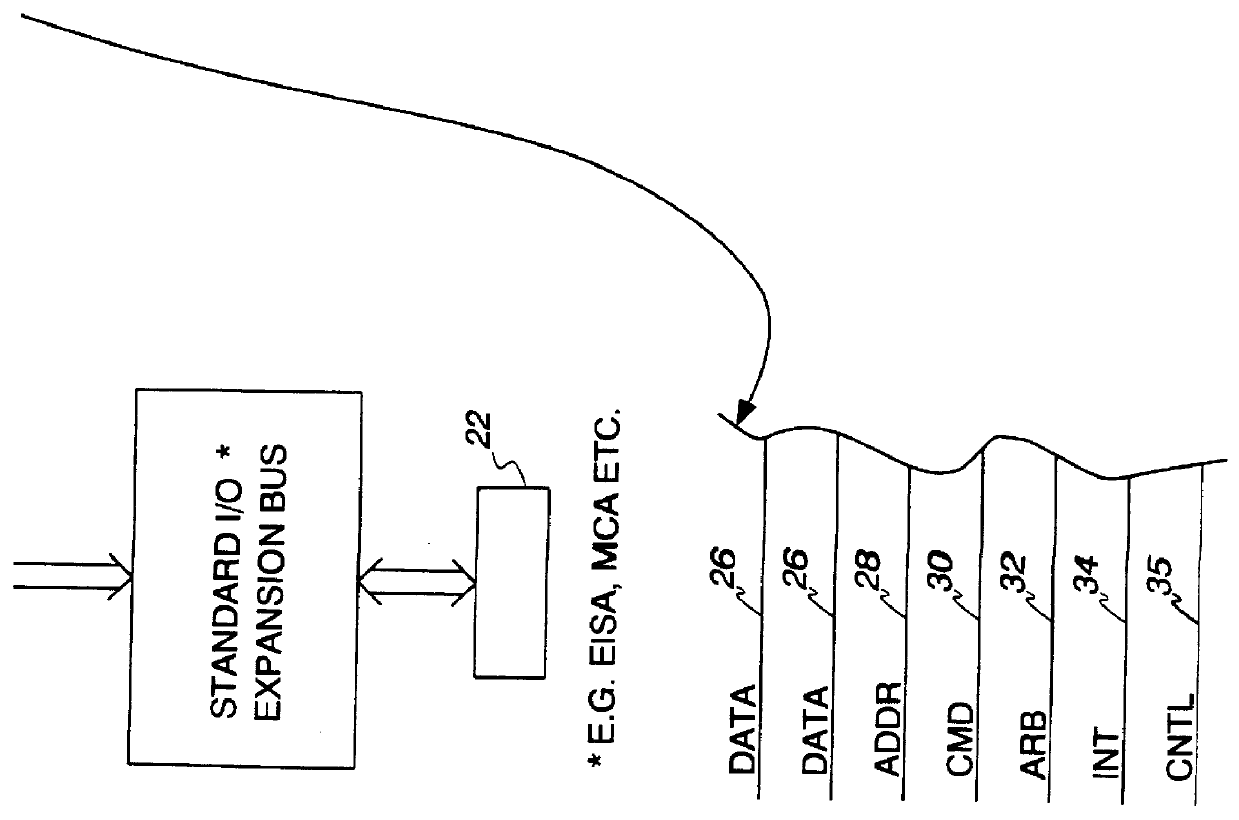

A symmetric multiprocessing system with a unified environment and distributed system functions provides unified address space for all functional units in the system while distributing the execution of various system functions over the functional units of the system whereby each functional unit assumes responsibility for its own aspects of these operations. In addition, the system provides improved system bus operation for transfer of data from memory.

Owner:INTEL CORP

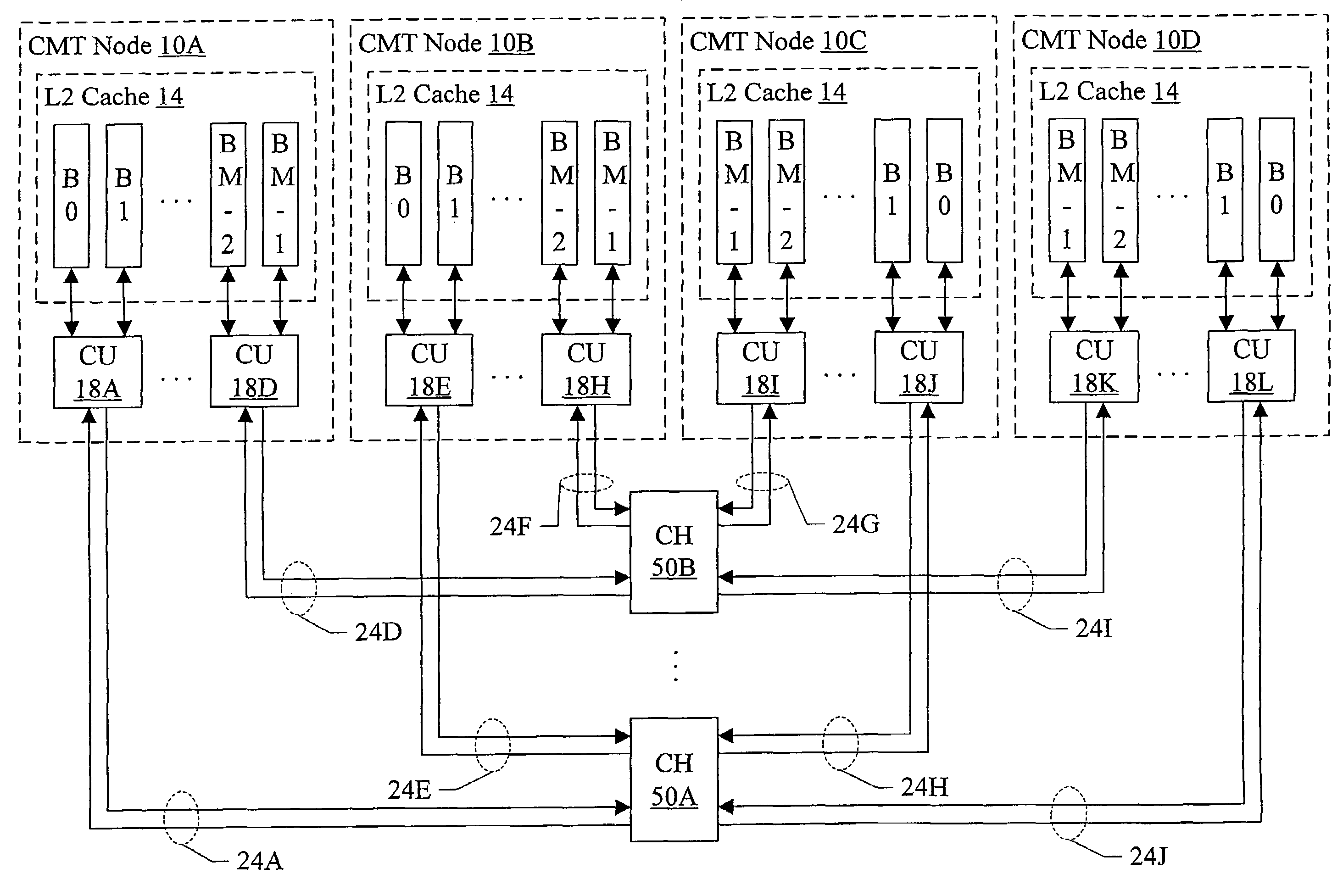

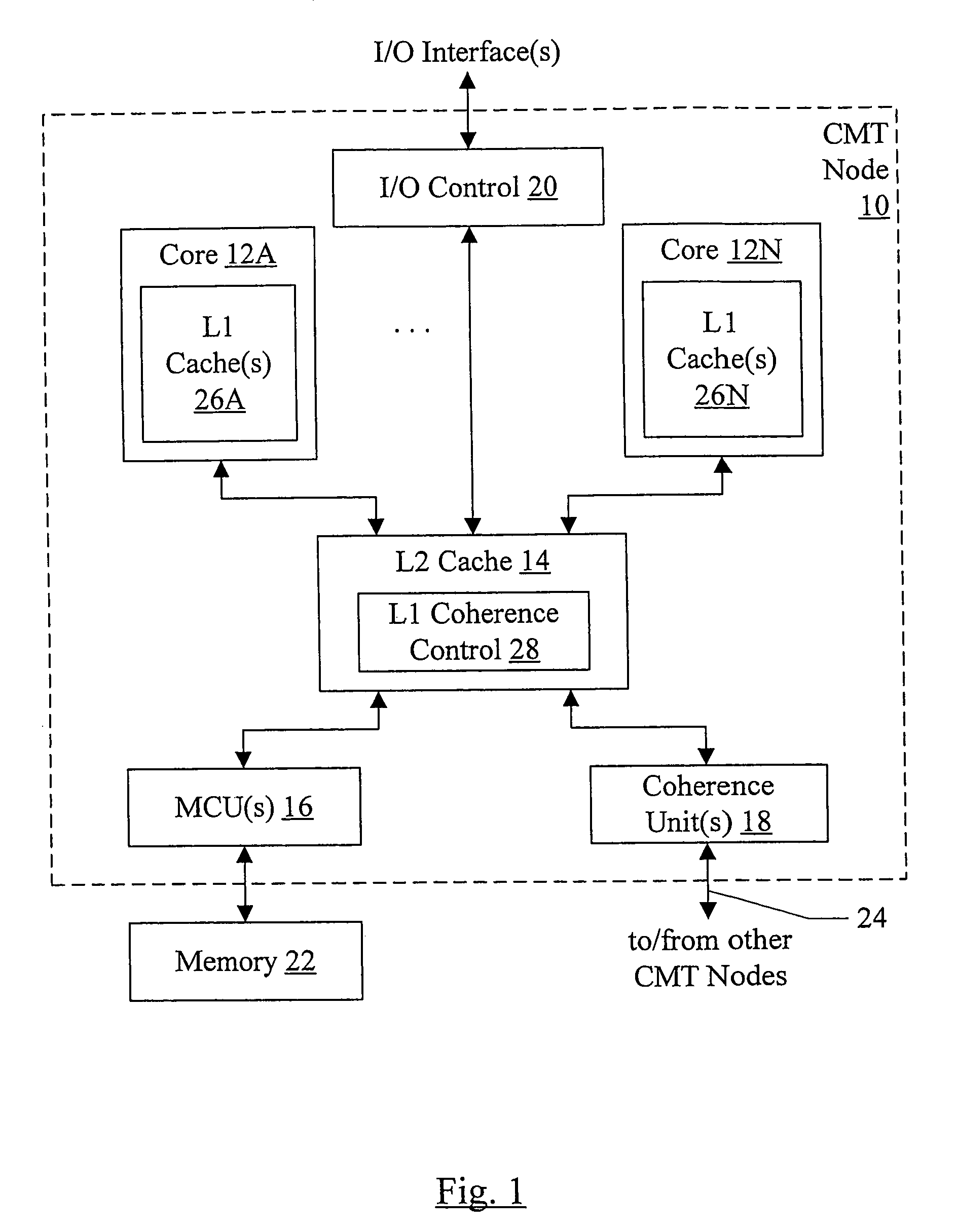

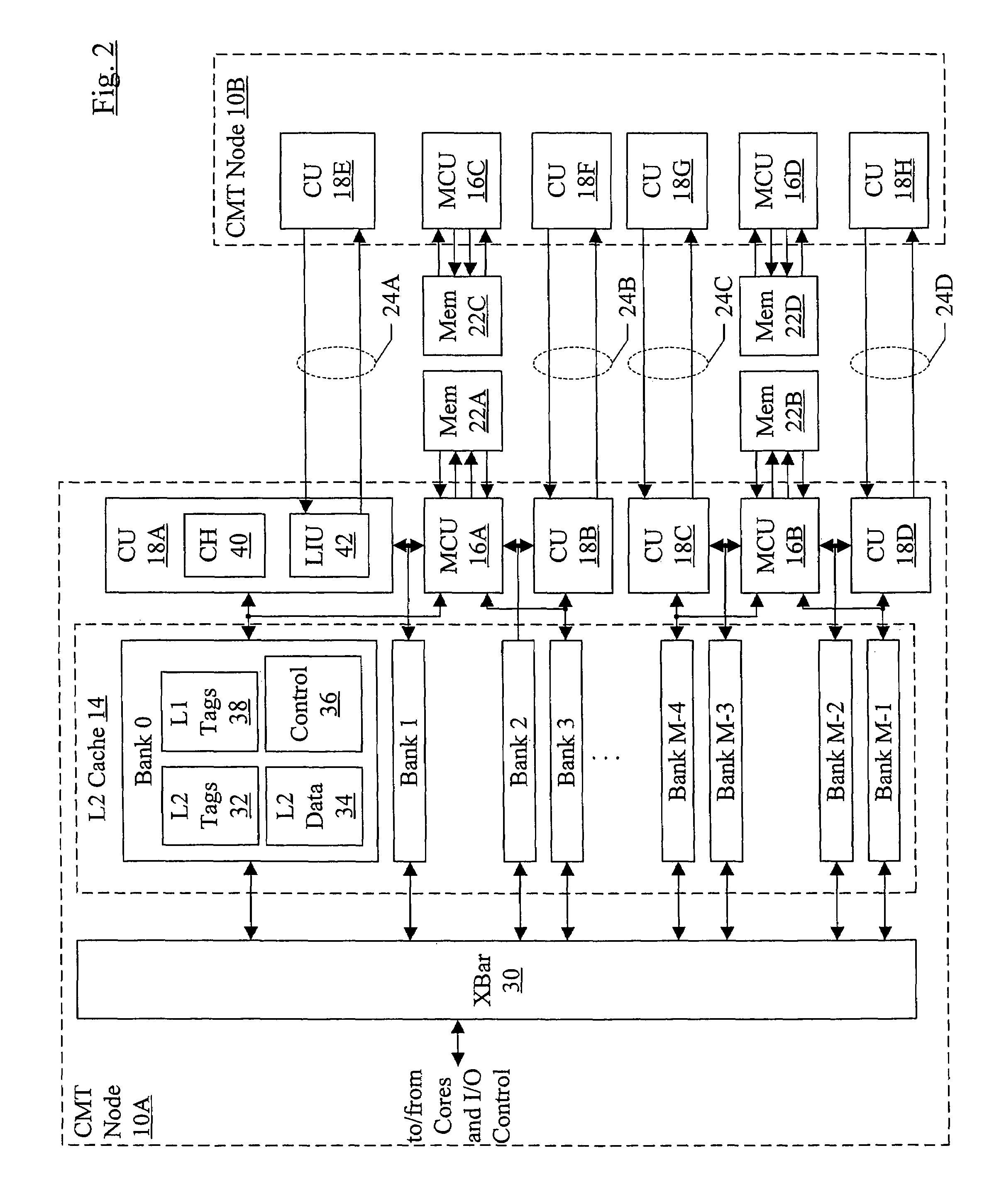

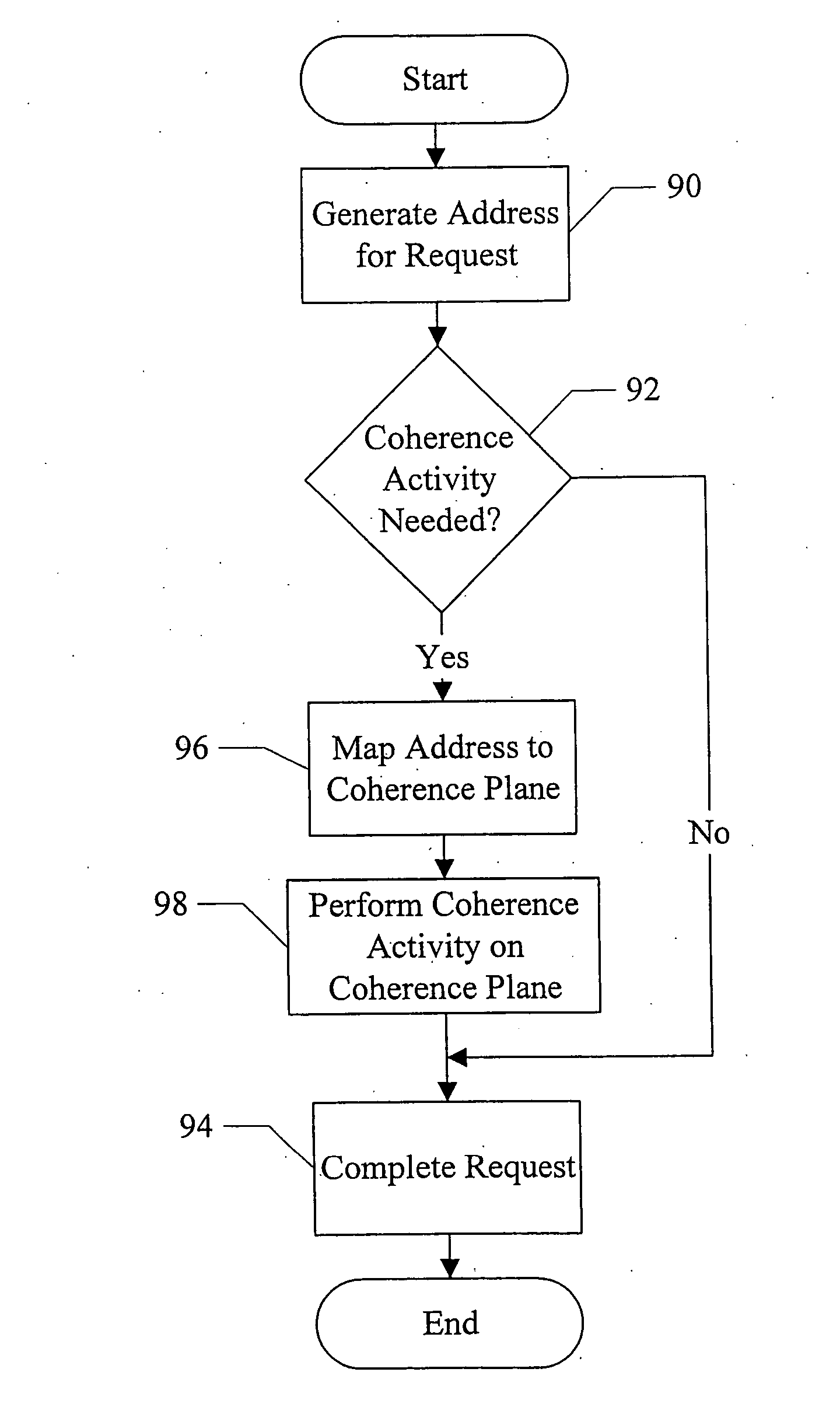

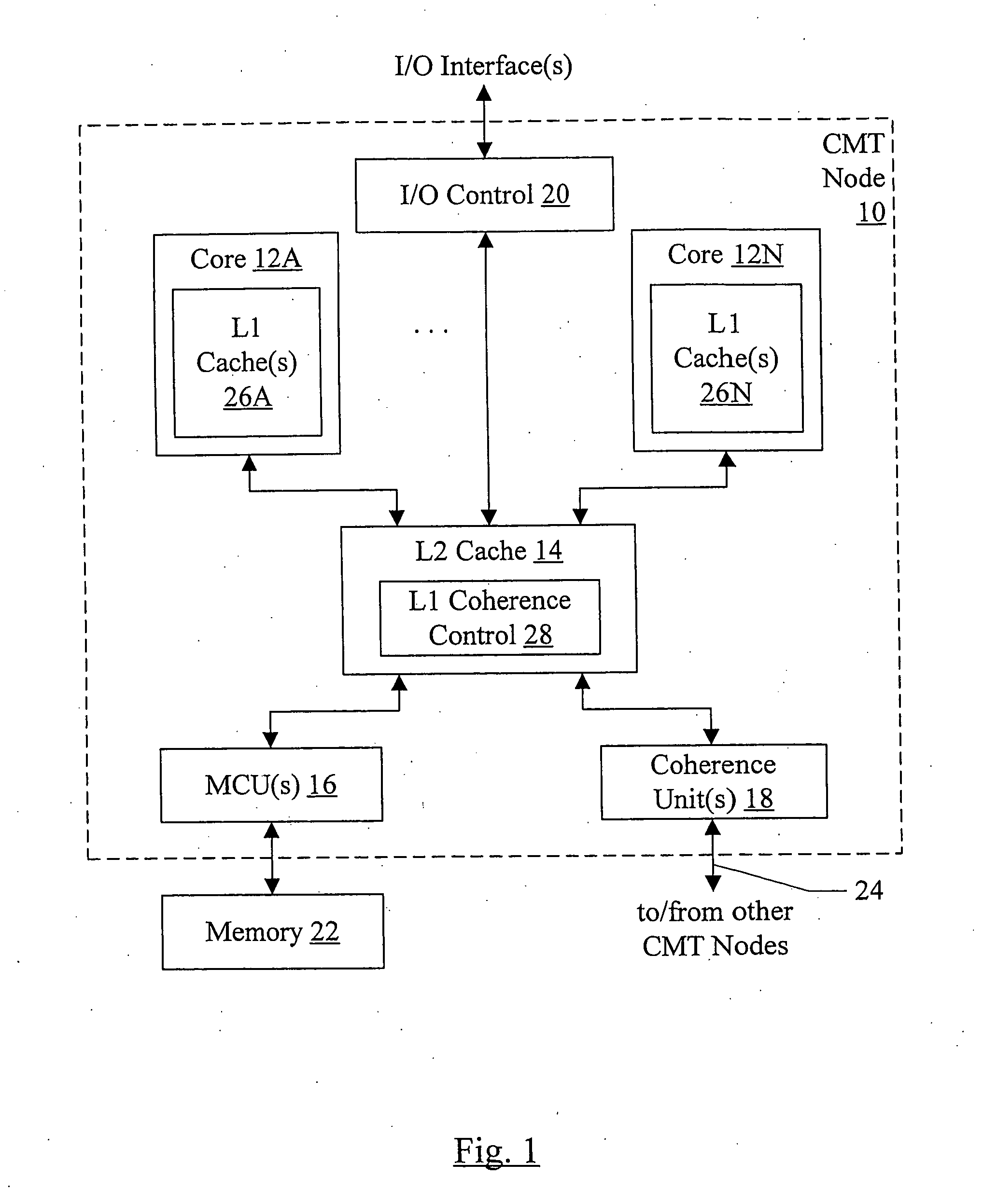

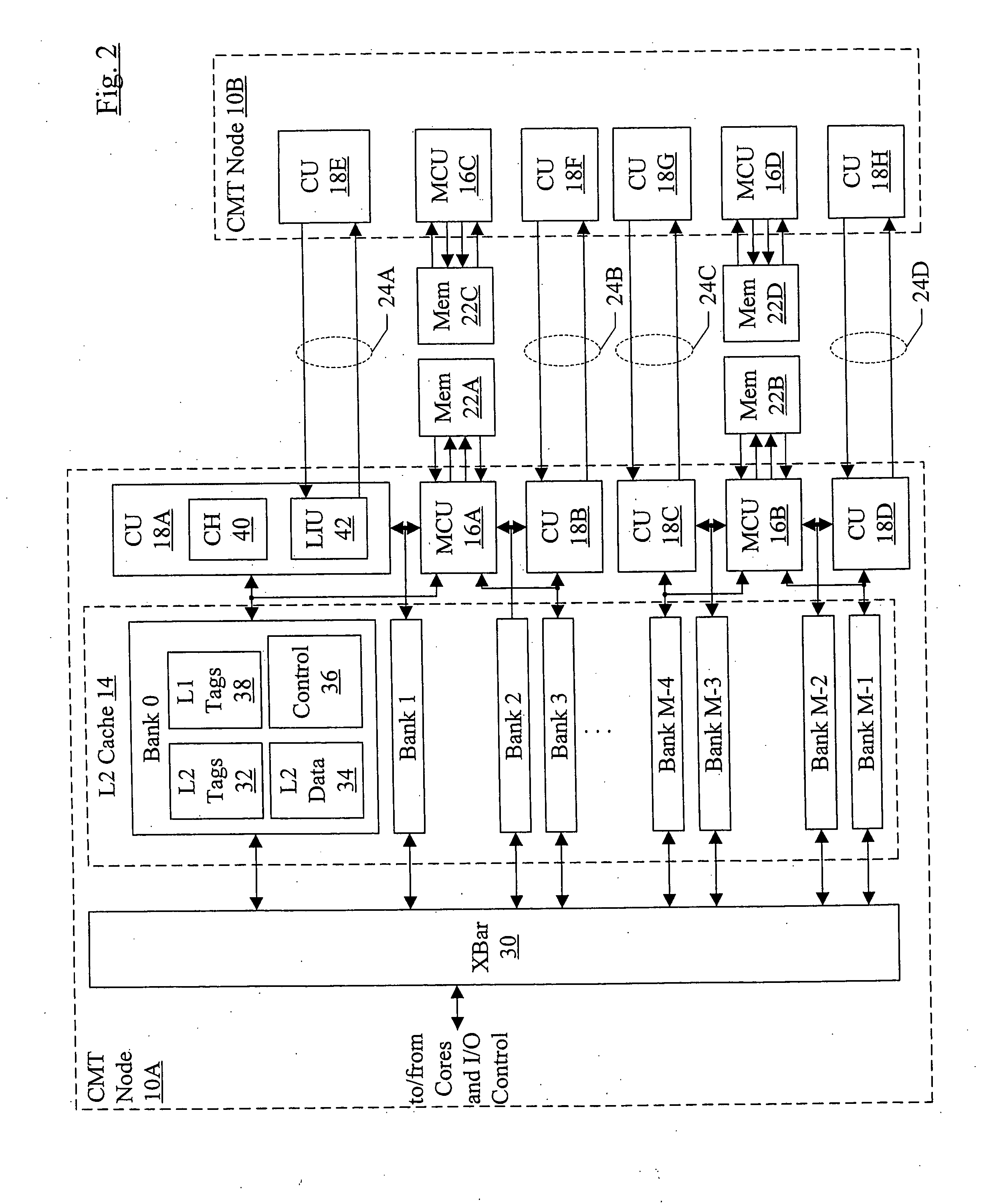

Multi-socket symmetric multiprocessing (SMP) system for chip multi-threaded (CMT) processors

In one embodiment, a node comprises a plurality of processor cores, coherency control circuitry coupled to the plurality of processor cores, and at least one coherence unit coupled to the coherency control circuitry. Each processor core is configured to have a plurality of threads active and each processor core includes at least one first level cache. The coherency control circuitry is configured to manage intranode coherency among the plurality of processor cores. The coherency unit is configured to couple to an external interface of the node, and is configured to transmit and receive coherence messages on the external interface to maintain coherency with at least one other node having one or processor cores and a coherence unit. In another embodiment, a system comprises an interconnect and a plurality of nodes coupled to the interconnect.

Owner:SUN MICROSYSTEMS INC

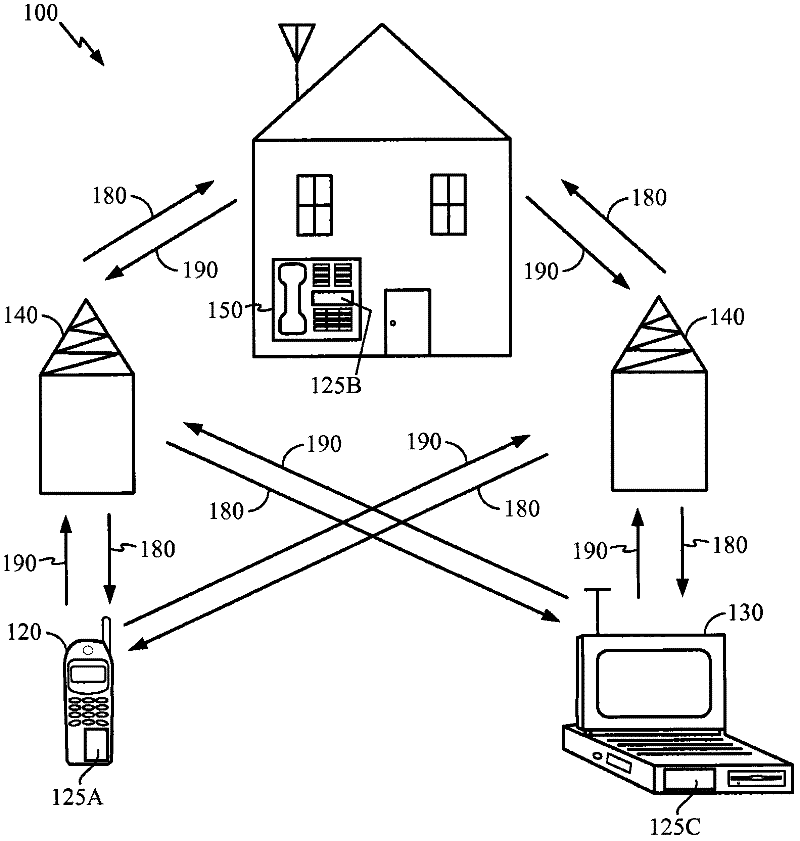

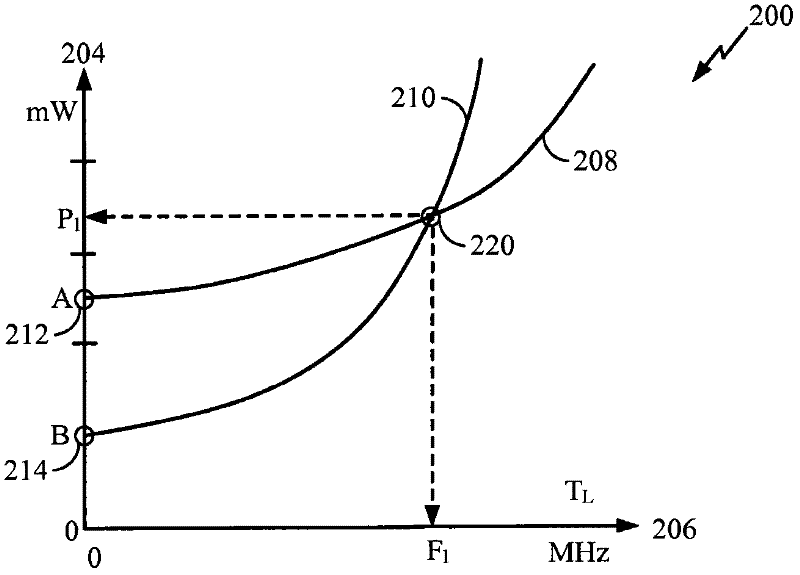

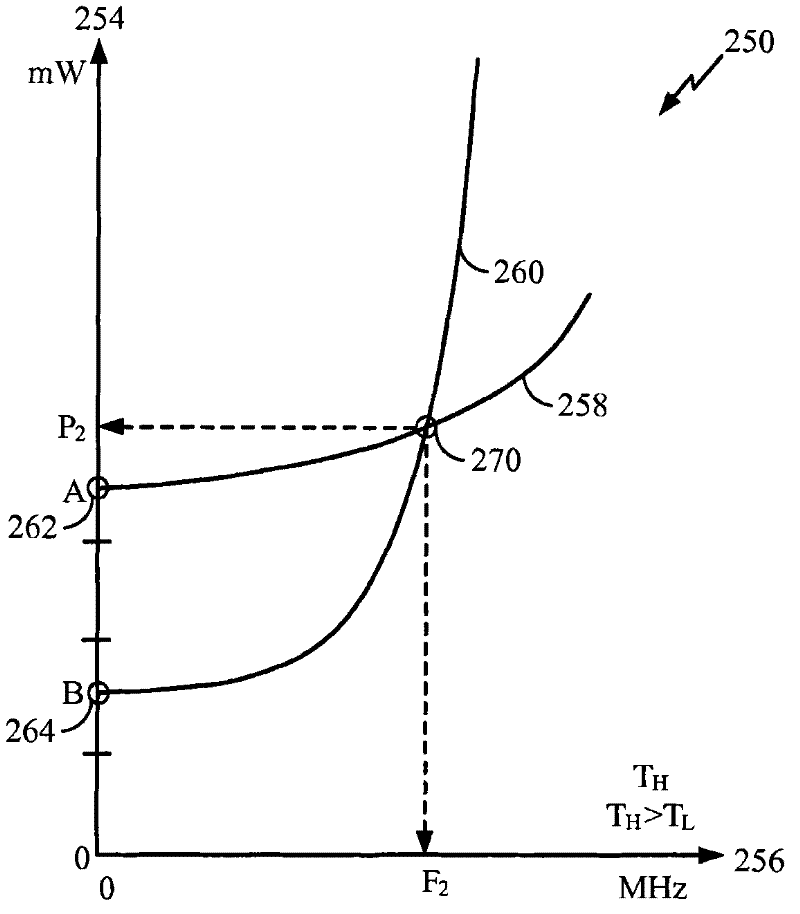

Apparatus and methods for adaptive thread scheduling on asymmetric multiprocessor

Techniques for adaptive thread scheduling on a plurality of cores for reducing system energy are described. In one embodiment, a thread scheduler receives leakage current information associated with the plurality of cores. The leakage current information is employed to schedule a thread on one of the plurality of cores to reduce system energy usage. On chip calibration of the sensors is also described.

Owner:QUALCOMM INC

Closed loop performance controller work interval instance propagation

ActiveUS20190034238A1Maximize throughputDelay minimizationResource allocationInstruction analysisParallel computingClosed loop

Systems and methods are disclosed for scheduling threads on an asymmetric multiprocessing system having multiple core types. Each core type can run at a plurality of selectable voltage and frequency scaling (DVFS) states. Threads from a plurality of processes can be grouped into thread groups. Execution metrics are accumulated for threads of a thread group and fed into a plurality of tunable controllers. A closed loop performance control (CLPC) system determines a control effort for the thread group and maps the control effort to a recommended core type and DVFS state. A closed loop thermal and power management system can limit the control effort determined by the CLPC for a thread group, and limit the power, core type, and DVFS states for the system. Metrics for workloads offloaded to co-processors can be tracked and integrated into metrics for the offloading thread group.

Owner:APPLE INC

Multi-socked symmetric multiprocessing (SMP) system for chip multi-threaded (CMT) processors

In one embodiment, a node comprises a plurality of processor cores, coherency control circuitry coupled to the plurality of processor cores, and at least one coherence unit coupled to the coherency control circuitry. Each processor core is configured to have a plurality of threads active and each processor core includes at least one first level cache. The coherency control circuitry is configured to manage intranode coherency among the plurality of processor cores. The coherency unit is configured to couple to an external interface of the node, and is configured to transmit and receive coherence messages on the external interface to maintain coherency with at least one other node having one or processor cores and a coherence unit. In another embodiment, a system comprises an interconnect and a plurality of nodes coupled to the interconnect.

Owner:SUN MICROSYSTEMS INC

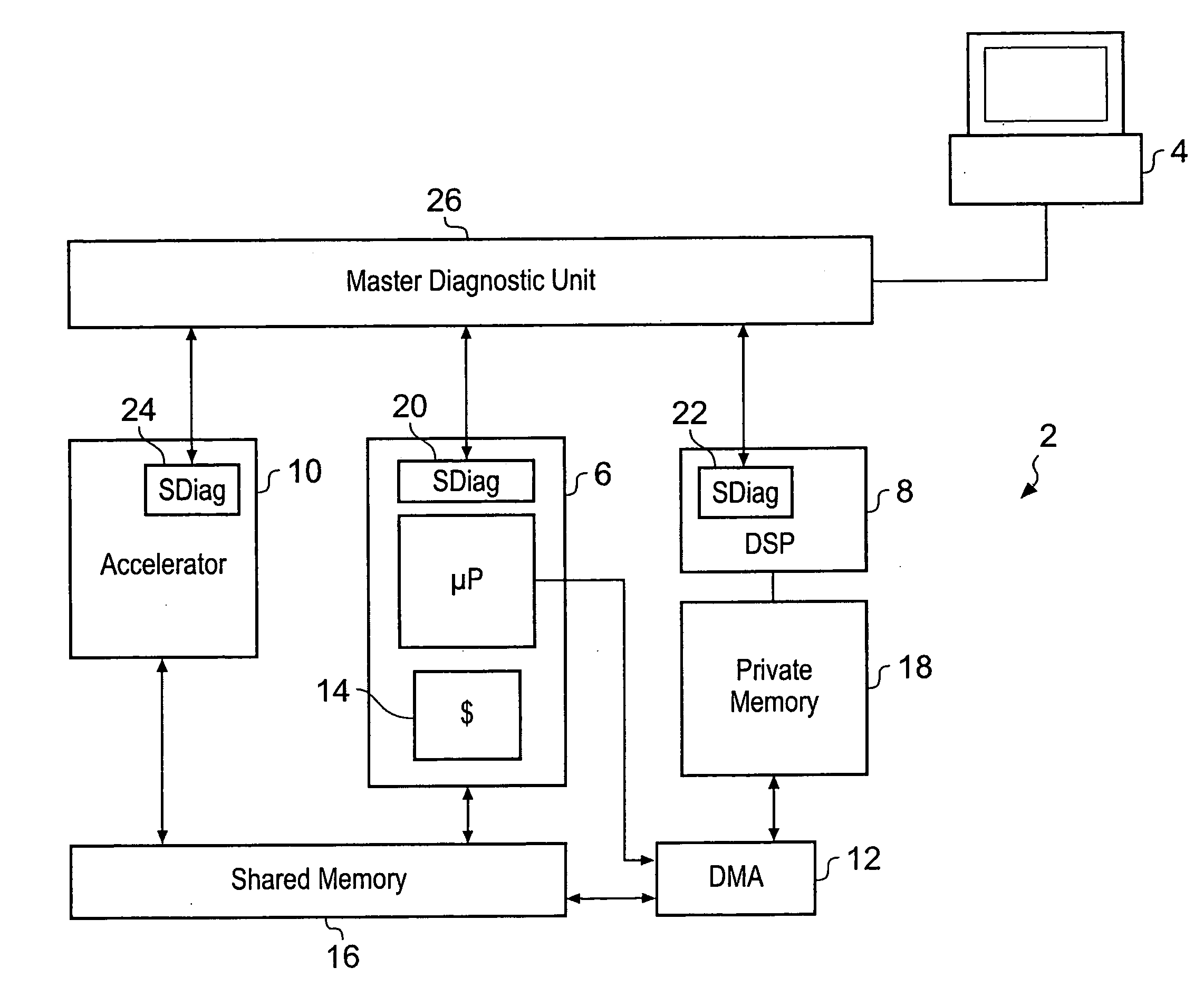

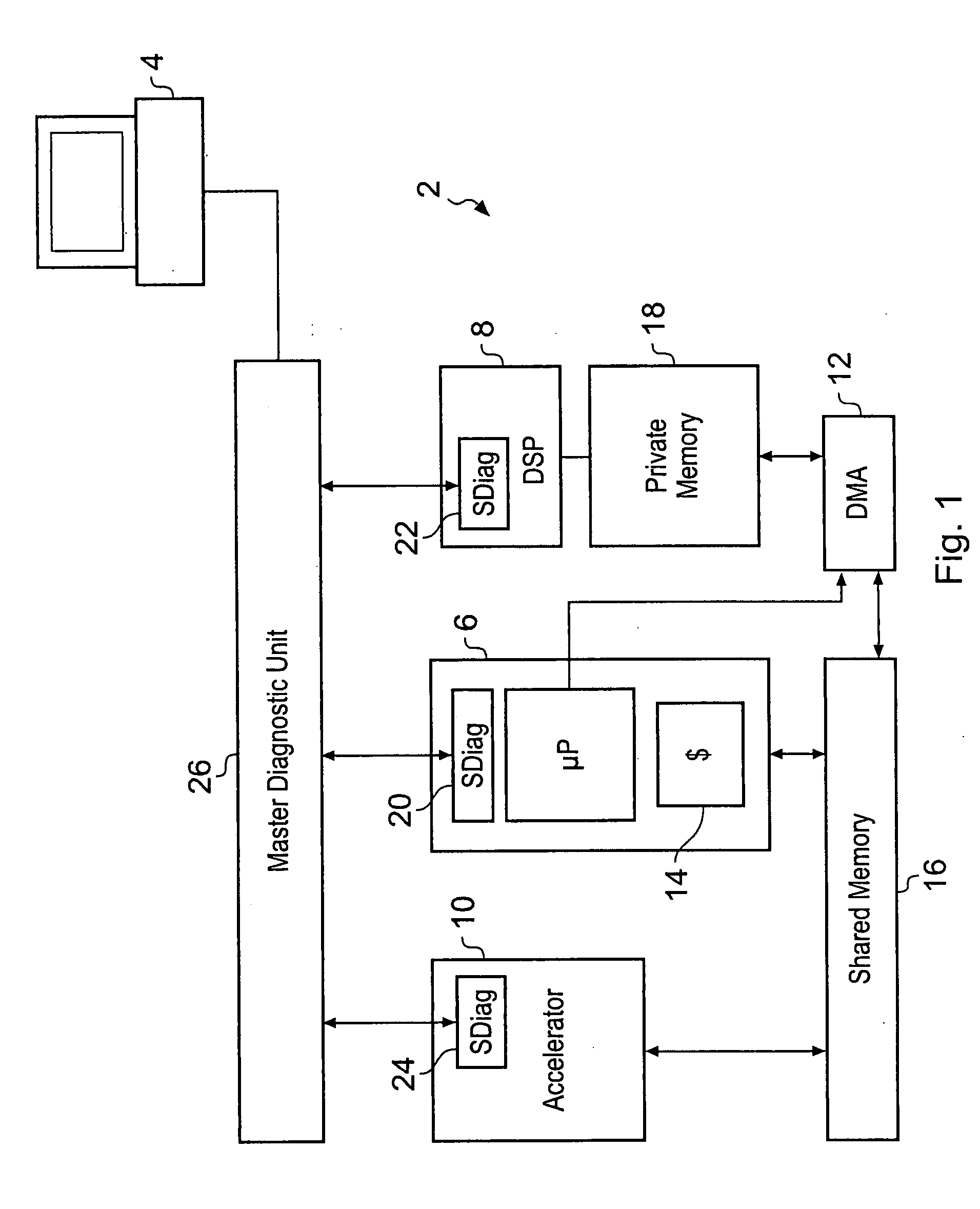

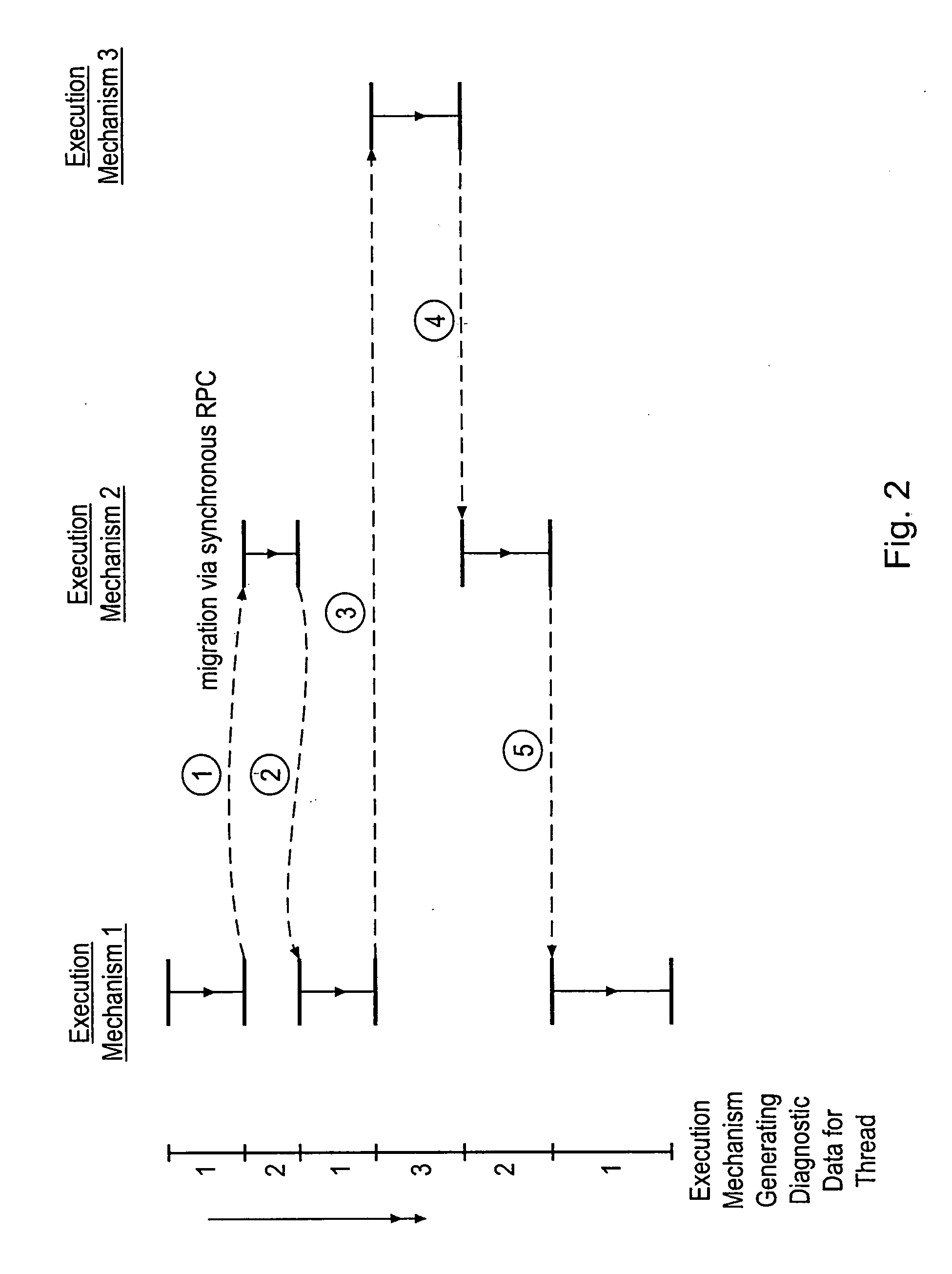

Performing diagnostic operations upon an asymmetric multiprocessor apparatus

ActiveUS20080098262A1Lighten the taskPresent techniqueDetecting faulty computer hardwareSoftware testing/debuggingMemory hierarchyDigital signal processing

An asymmetric multiprocessor apparatus 2 is provided in which respective slave diagnostic units 20, 22, 24 are associated with corresponding execution mechanisms 6, 8, 10. A master diagnostic unit 26 tracks the migration of thread execution between the different execution mechanisms 6, 8, 10 so that the execution of a given thread can be followed by the diagnostic mechanisms 20, 22, 24, 26 and this information provided to the programmer. The execution mechanisms 6, 8, 10 can be diverse such as a general purpose processor 6, a DMA unit 12, a coprocessor, an VLIW processor, a digital signal processor 8 and a hardware accelerator 10. The asymmetric multiprocessor apparatus 2 will also typically include an asymmetric memory hierarchy such as including two or more of a global memory, a shared memory 16, a private memory 18 and a cache memory 14.

Owner:ARM LTD

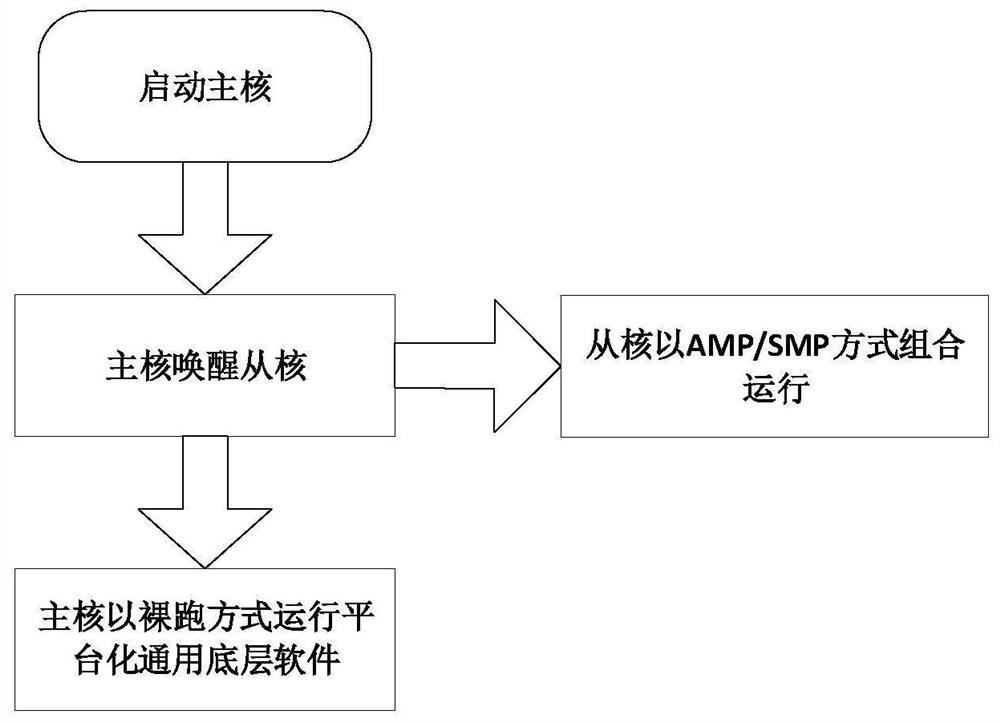

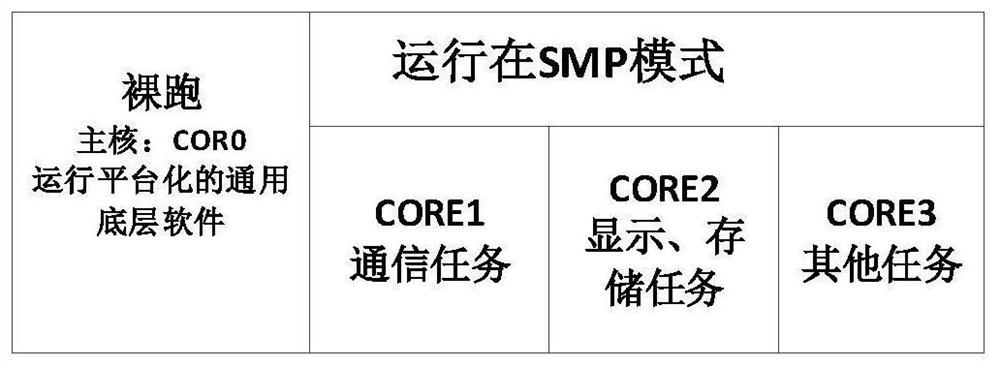

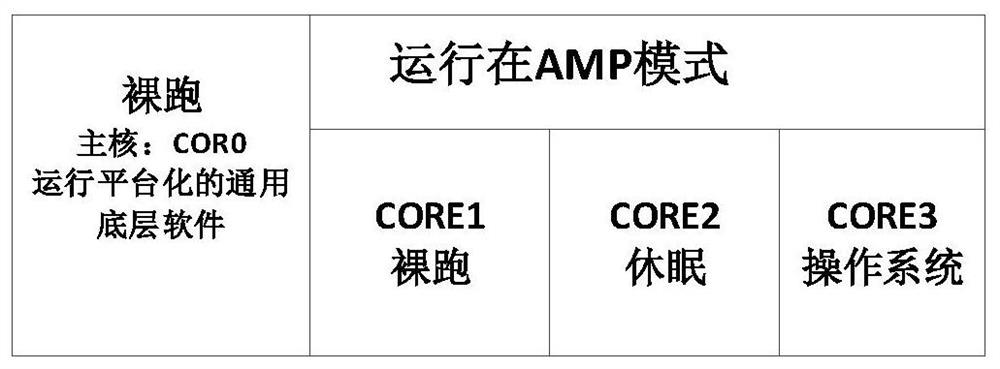

Platform architecture design method of multi-core CPU operation mode

PendingCN112463342AGood real-time performanceGood scalabilityProgram initiation/switchingResource allocationComputer architectureTime function

The invention discloses a platform architecture design method of a multi-core CPU operation mode, and the method comprises the following steps that an isomorphic multi-core CPU firstly starts a main core, and the main core is core 0 of the isomorphic multi-core CPU; the master core awakens the slave core in the initialization stage; after the slave cores are started, the slave cores operate in anAMP / SMP mode in a combined mode; the main core runs platformized universal underlying software, the CPU is a central processing unit, the AMP is asymmetric multi-processing, and the SMP is symmetric multi-processing. The EHMP operation mode provided by the invention integrates the advantages of the traditional AMP and SMP modes, follows the principles that a naked running mode realizes a high-reliability and high-real-time function and an operating system mode realizes a non-strong real-time function, gives consideration to the reliability, real-time performance and CPU processing capability of a product, and ensures the safety of multi-core operation and the reliability of the system.

Owner:BEIJING SIFANG JIBAO ENG TECH +1

Scheduling of work interval objects in an amp architecture using a closed loop performance controller

ActiveUS20180349182A1Minimizing thread scheduling latencyMaximize throughputProgram initiation/switchingResource allocationAudio power amplifierClosed loop

Systems and methods are disclosed for scheduling threads on a processor that has at least two different core types, such as an asymmetric multiprocessing system. Each core type can run at a plurality of selectable voltage and frequency scaling (DVFS) states. Threads from a plurality of processes can be grouped into thread groups. Execution metrics are accumulated for threads of a thread group and fed into a plurality of tunable controllers for the thread group. A closed loop performance control (CLPC) system determines a control effort for the thread group and maps the control effort to a recommended core type and DVFS state. A closed loop thermal and power management system can limit the control effort determined by the CLPC for a thread group, and limit the power, core type, and DVFS states for the system. Deferred interrupts can be used to increase performance.

Owner:APPLE INC

Symmetric multiprocessing system with unified environment and distributed system functions wherein bus operations related storage spaces are mapped into a single system address space

InactiveUS6125436AMemory adressing/allocation/relocationMicro-instruction address formationEmbedded systemSymmetric multiprocessing

Owner:RPX CORP

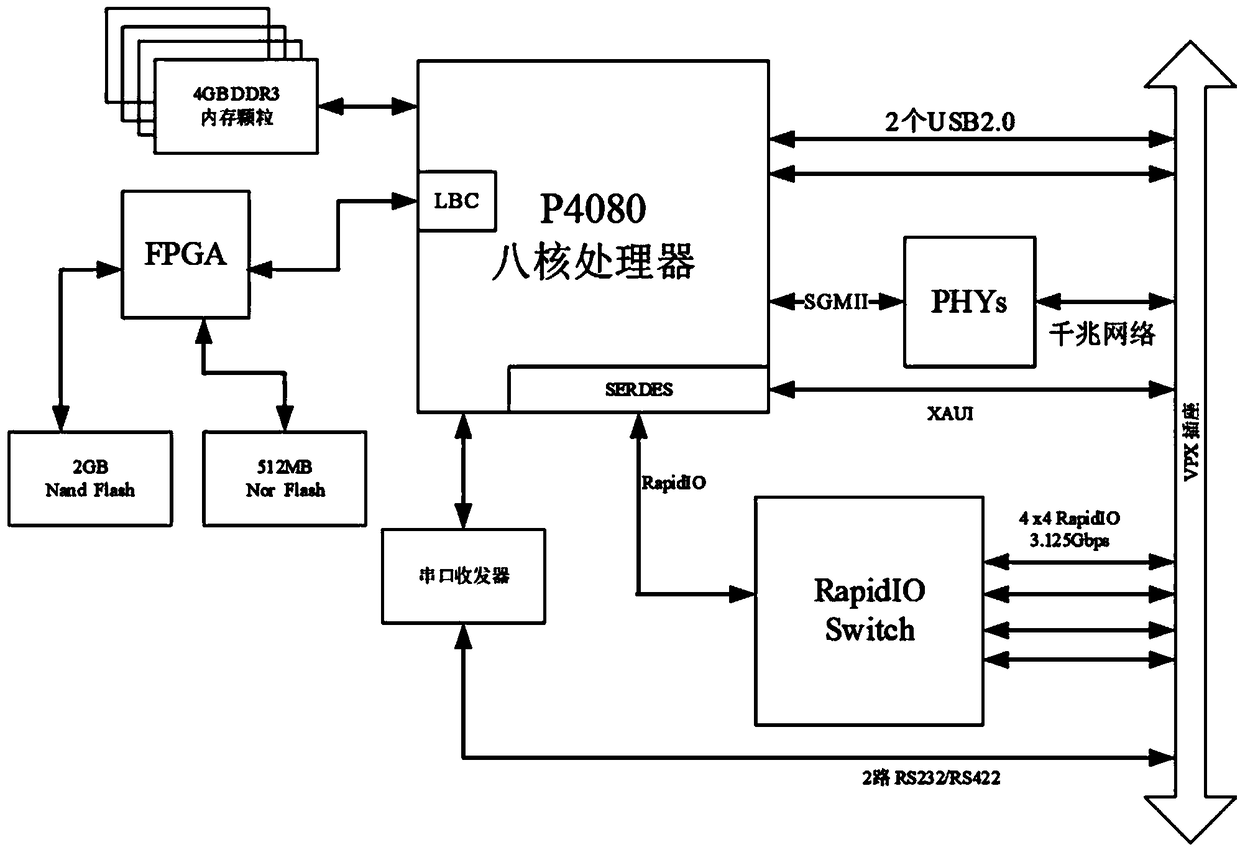

Embedded processing module based on P4080 processor

InactiveCN108845520AImprove performanceMeet application needsProgramme controlComputer controlDatapathMilitary computers

An embedded processing module based on a P4080 processor comprises a P4080 processor minimum system and a power module. The P4080 processor minimum system extends an external function through a VPX connector, the P4080 processor minimum system exchanges data with an external device through a high-speed I / O port, the power module includes an input power supply and a processor core secondary power supply adopting a PWM switching power supply, and supply voltage and output current are adjusted dynamically with a processor load. The embedded processing module based on a P4080 processor adopts a standardized VPX structure, can realize the extension of a storage device through an eLBC bus, has a relatively good environment adaptation capability, can combine a symmetrical multiprocessor and an asymmetrical multiprocessor to realize different levels of operation, thus flexibly distinguishes control, data path and application processing, meets the application requirement of an open type military computer, and has very high universality.

Owner:XIAN MICROELECTRONICS TECH INST

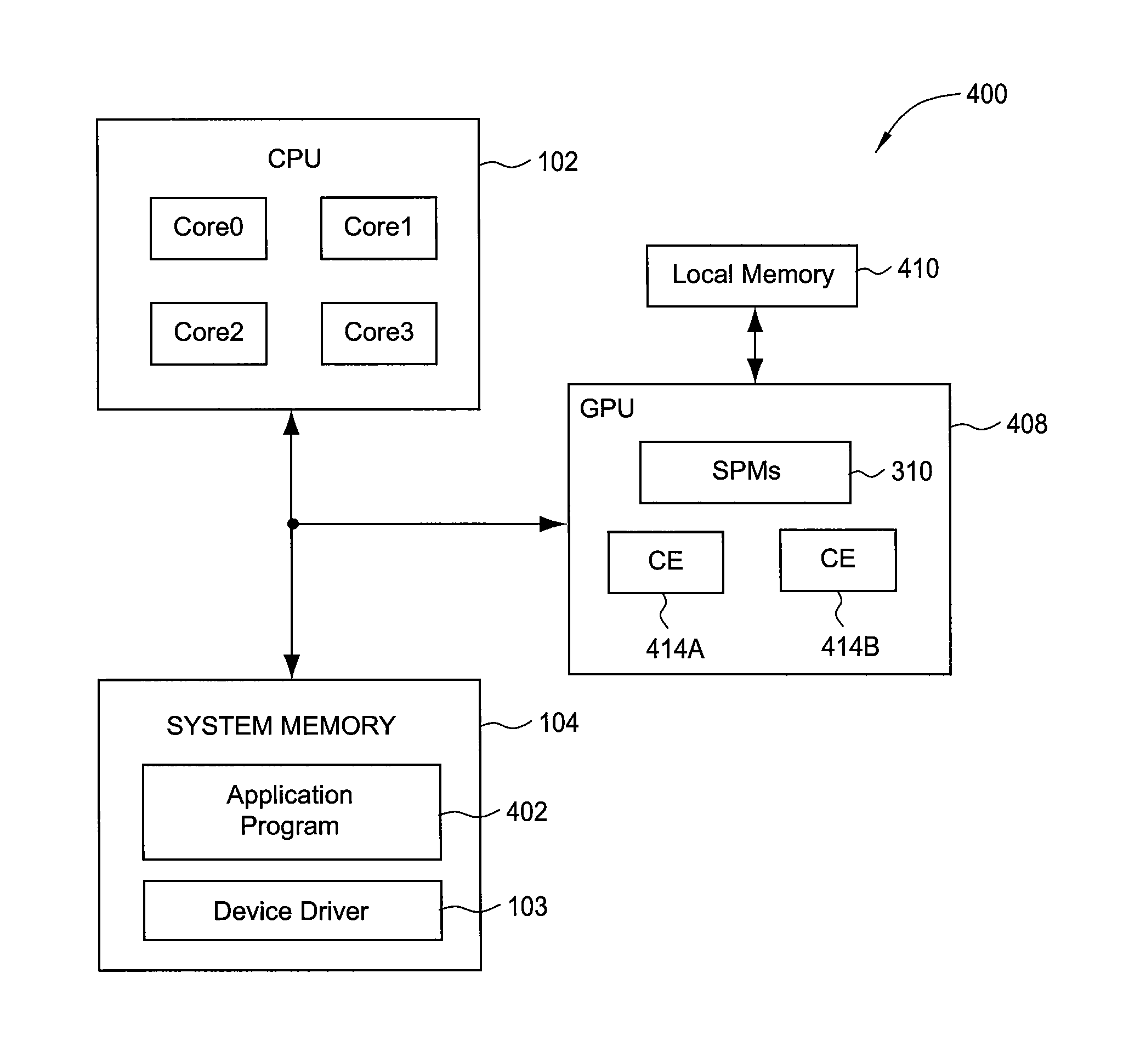

Tokenized streams for concurrent execution between asymmetric multiprocessors

ActiveUS9542192B1Improve processing efficiencyImprove efficiencyProgram synchronisationConcurrent instruction executionParallel computingAsymmetric multiprocessing

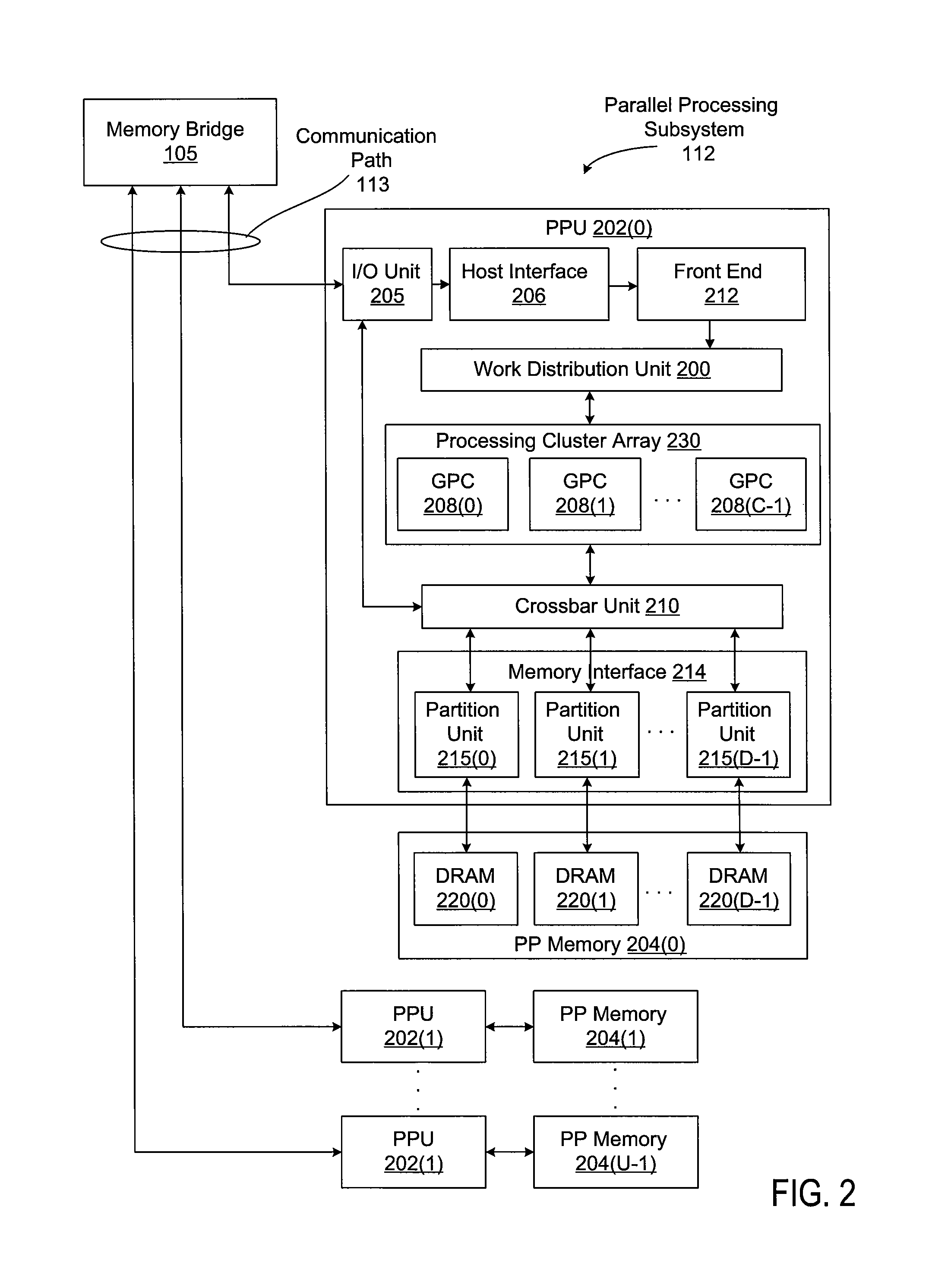

Owner:NVIDIA CORP

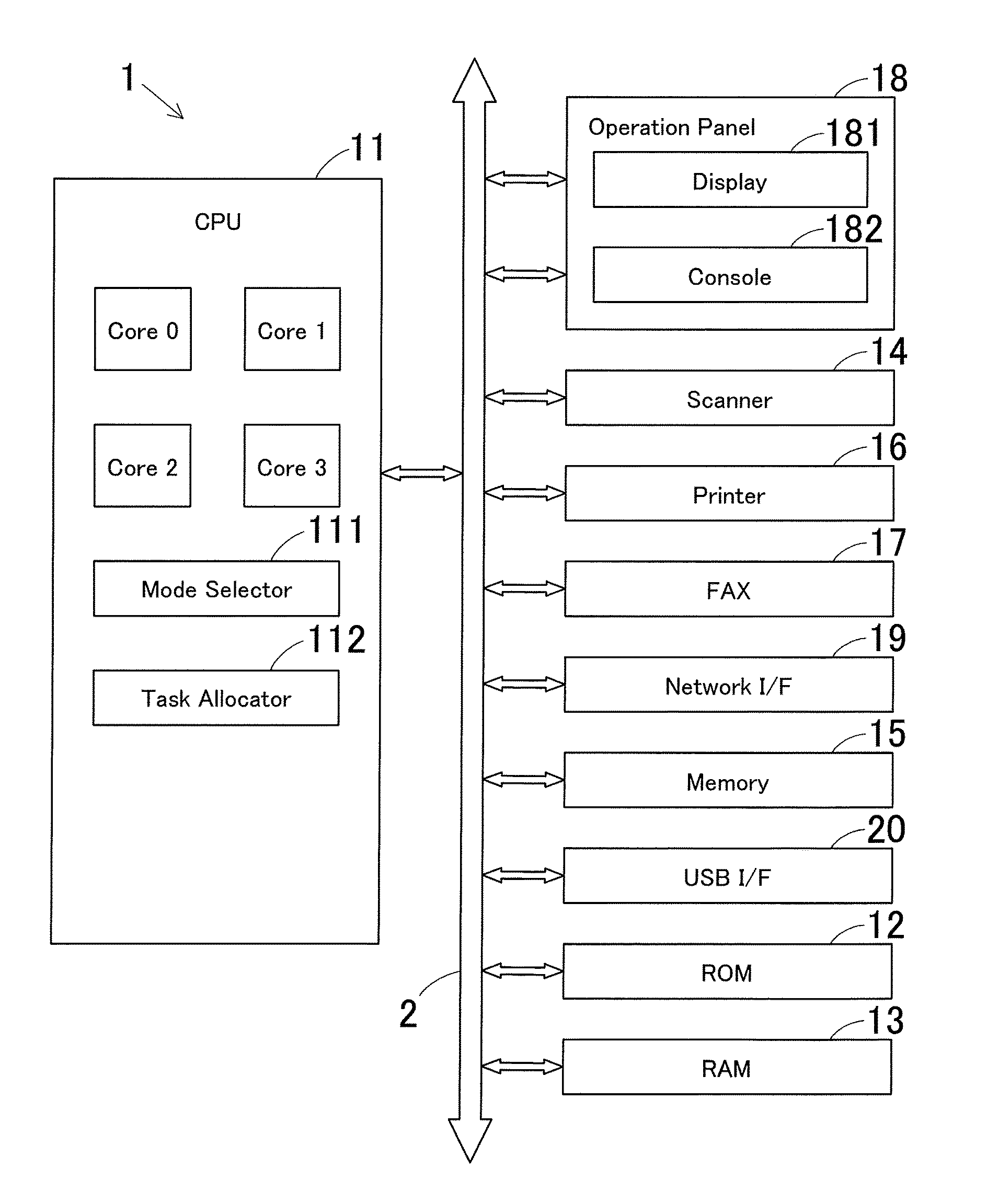

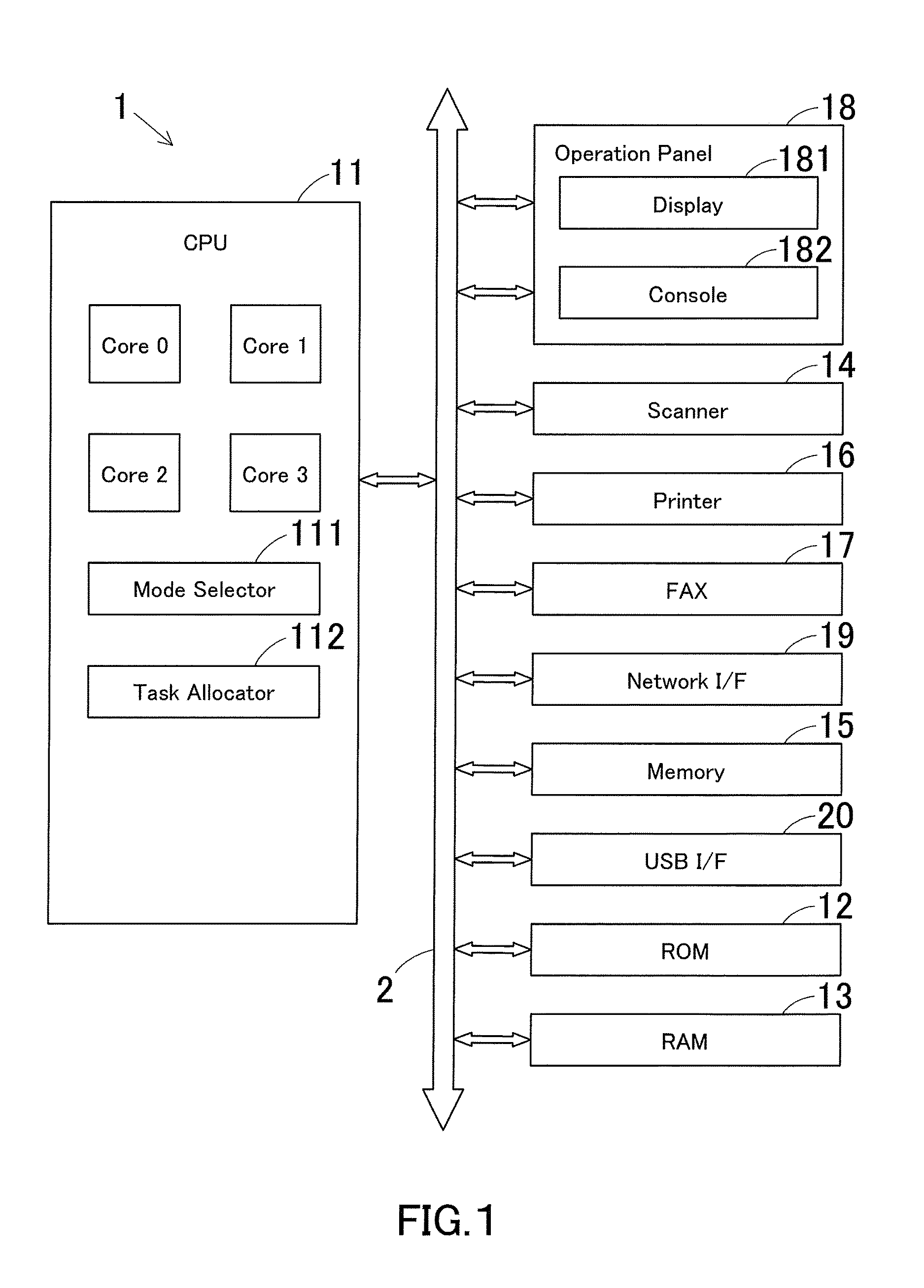

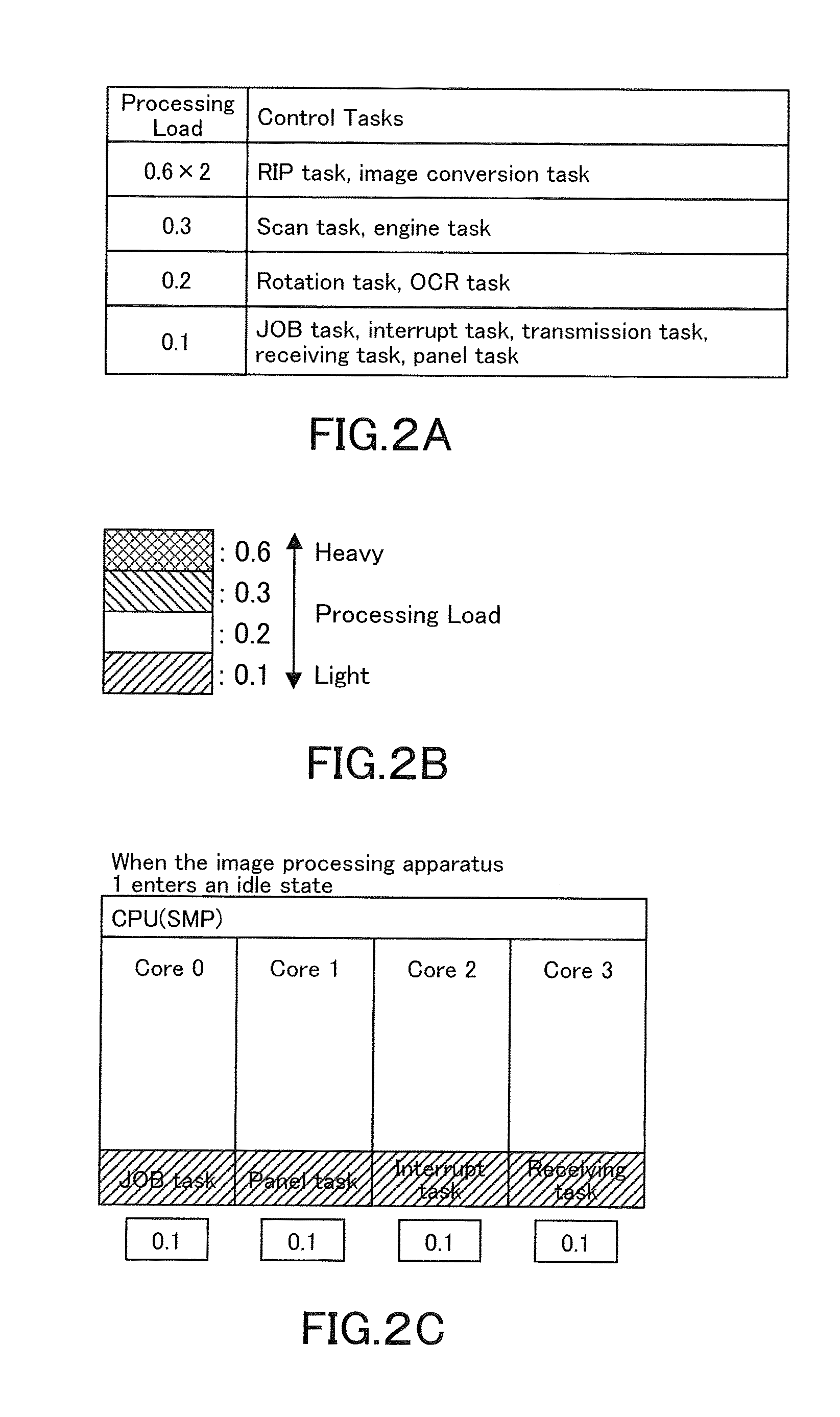

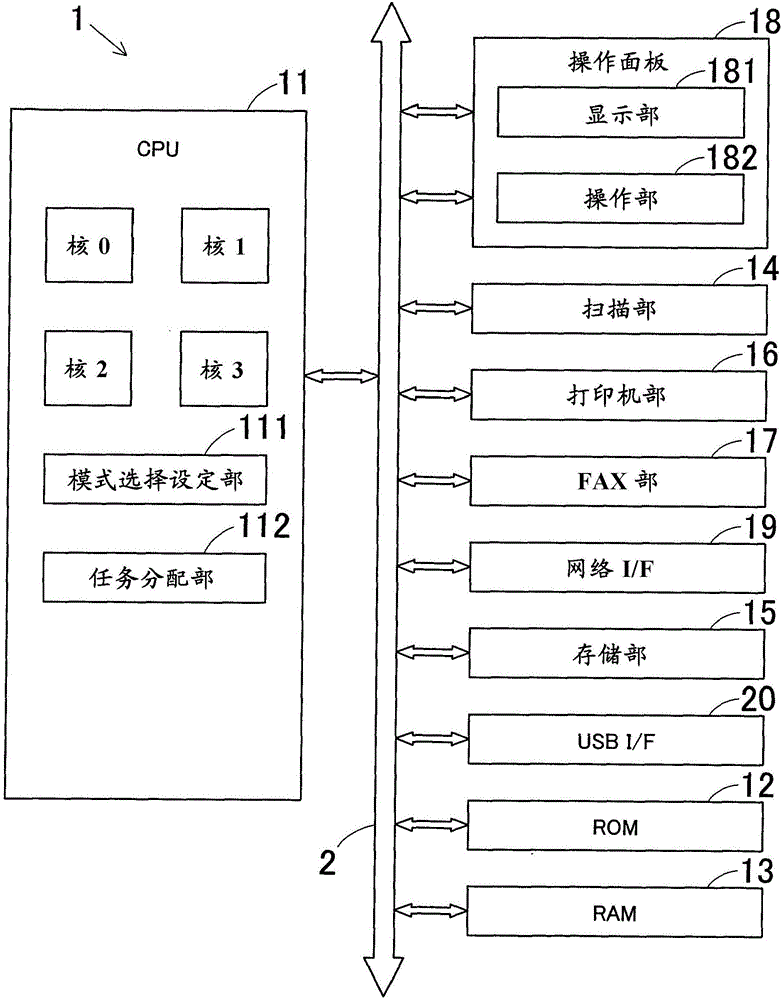

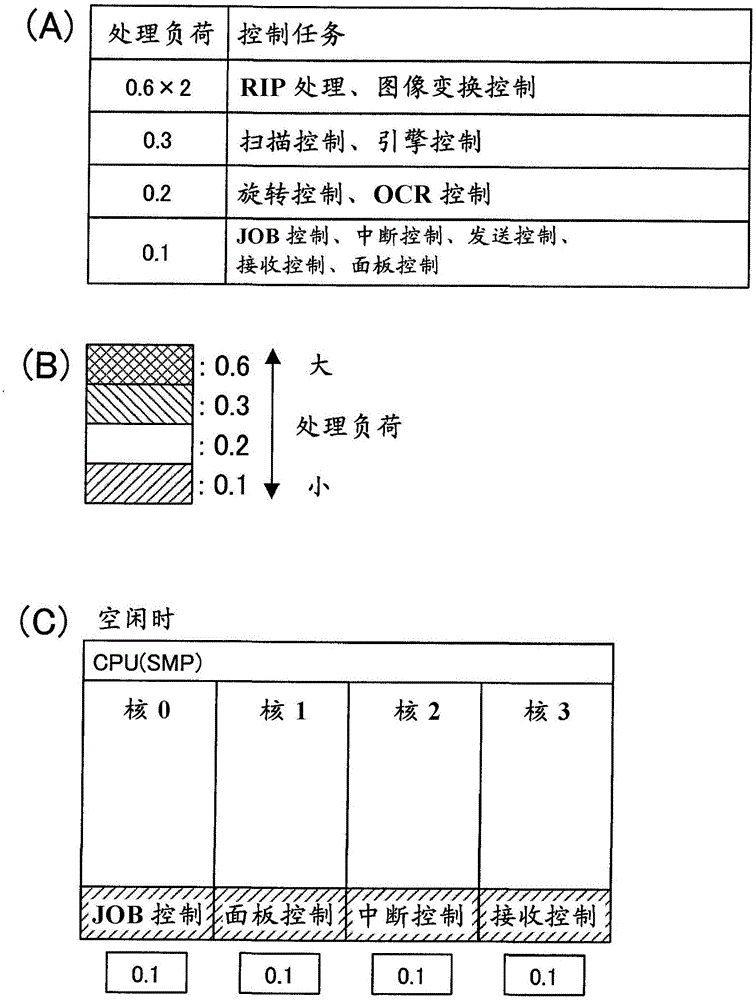

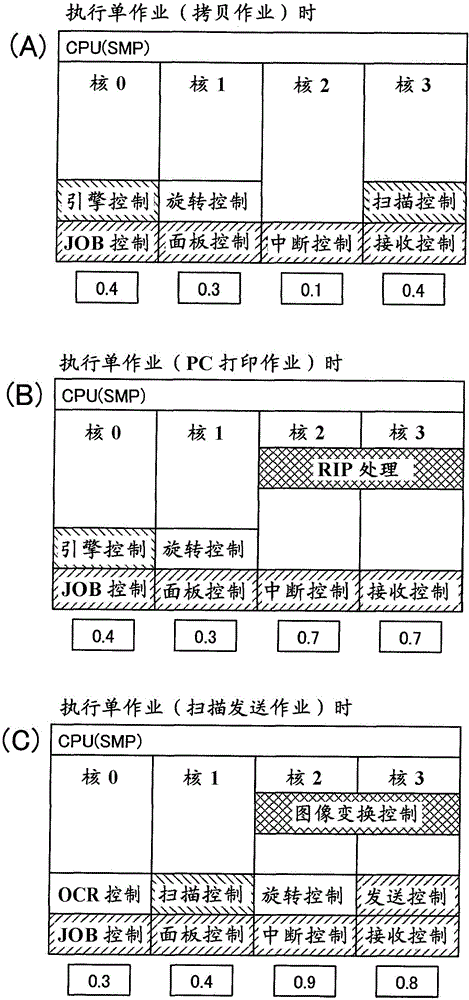

Image processing apparatus, control task allocation method, and recording medium

InactiveUS20170060644A1Resource allocationDigital data processing detailsImaging processingDistribution control

An image processing apparatus includes: a multi-core CPU having multiple cores; a selector that selects either a first mode or a second mode with respect to allocation of control tasks to the cores of the multi-core CPU; and an allocator that allocates control tasks to the cores of the multi-core CPU by the symmetric multiprocessing technology when the first mode is selected by the selector, and that allocates control tasks to the cores of the multi-core CPU by the asymmetric multiprocessing technology when the second mode is selected by the selector.

Owner:KONICA MINOLTA INC

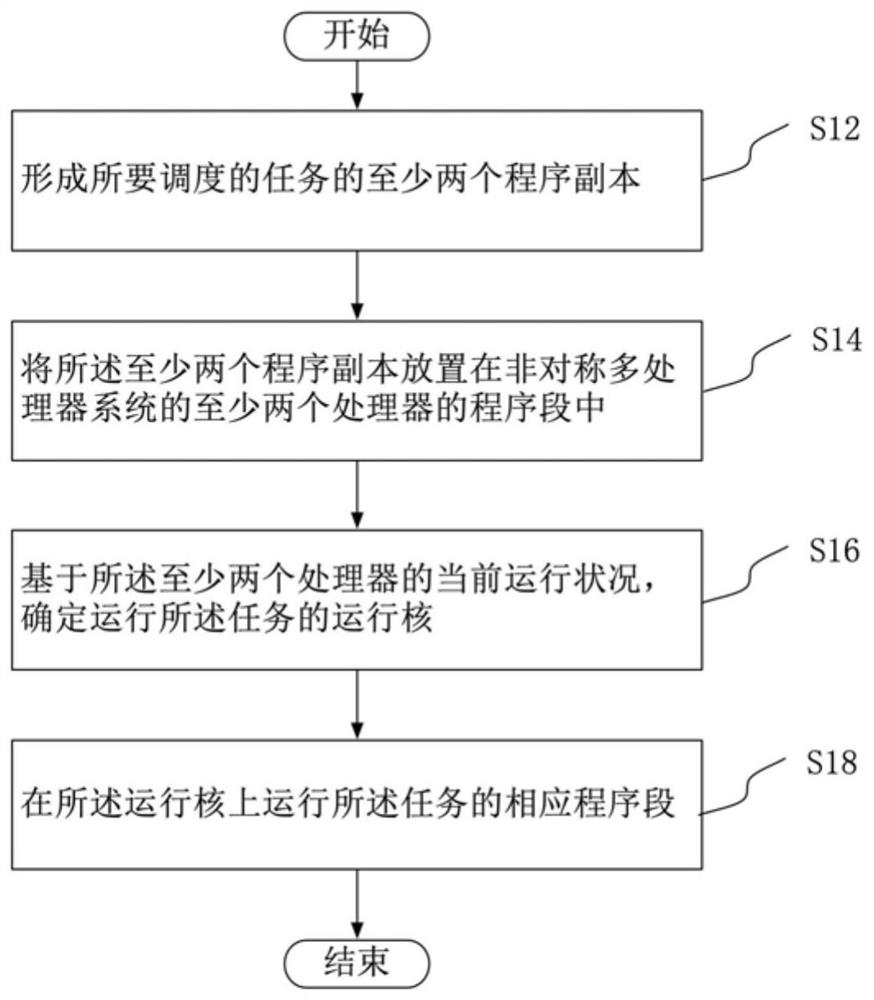

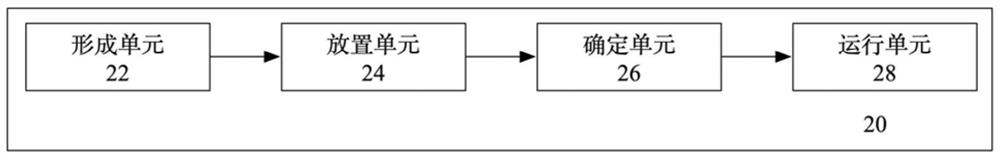

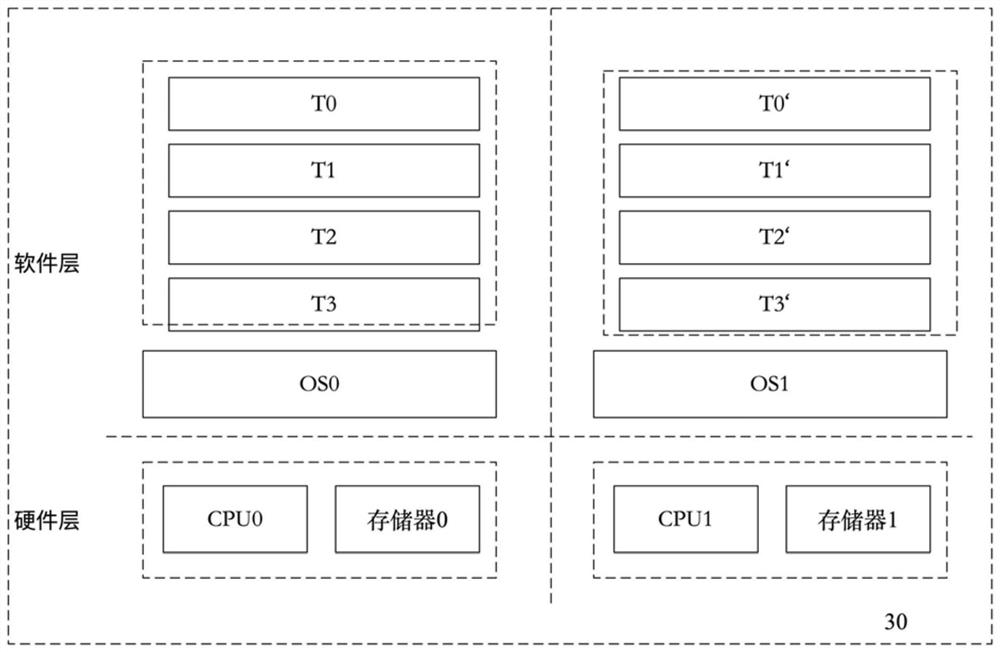

Task scheduling method, device and system and computer readable medium

PendingCN113722082ABalance loadExamples cannot be limitedResource allocationProgram segmentParallel computing

Embodiments of the invention provide a task scheduling method, device and system and a computer readable medium. The method comprises the following steps: forming at least two program copies of a task to be scheduled; placing the at least two program copies in program segments of at least two processors of an asymmetric multi-processing system; determining a running processor for running the task based on the current running conditions of the at least two processors; and running the corresponding program segment of the task on the running processor.

Owner:ALIBABA GRP HLDG LTD

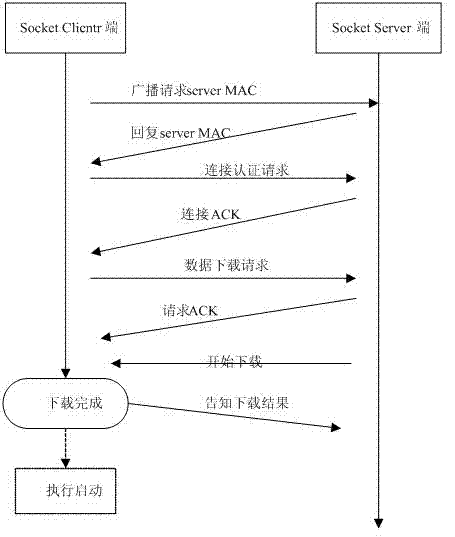

Software loading and storing method under embedded asymmetric multiprocessing architecture

ActiveCN102637134BReduce hardware costsIncrease flexibilityFault responseProgram loading/initiatingFile systemAsymmetric multiprocessing

The invention relates to a software loading and storing method under an embedded asymmetric multiprocessing architecture. In an asymmetric multiprocessing system, one system is used as a main system, and other systems are used as slave systems; the main system and the slave systems respectively use distributed and centralized storage modes, and the slave systems are used as a start storage region for storing a Bootloader; a system kernel and a file system both are stored in the main system; the main system uses a NANDflash as a memory, the system software is loaded in a master-slave mode, and the software loading of the slave systems is controlled by the main system; and the slave systems download the kernel and the file system dynamically from the main system, and automatically load the downloaded kernel and file system after downloading. By virtue of the method for software storage and loading of the main system and the slave systems, the flexibility, stability and reliability of the system are enhanced, and the hardware cost of the complete machine is also saved.

Owner:网经科技(苏州)有限公司

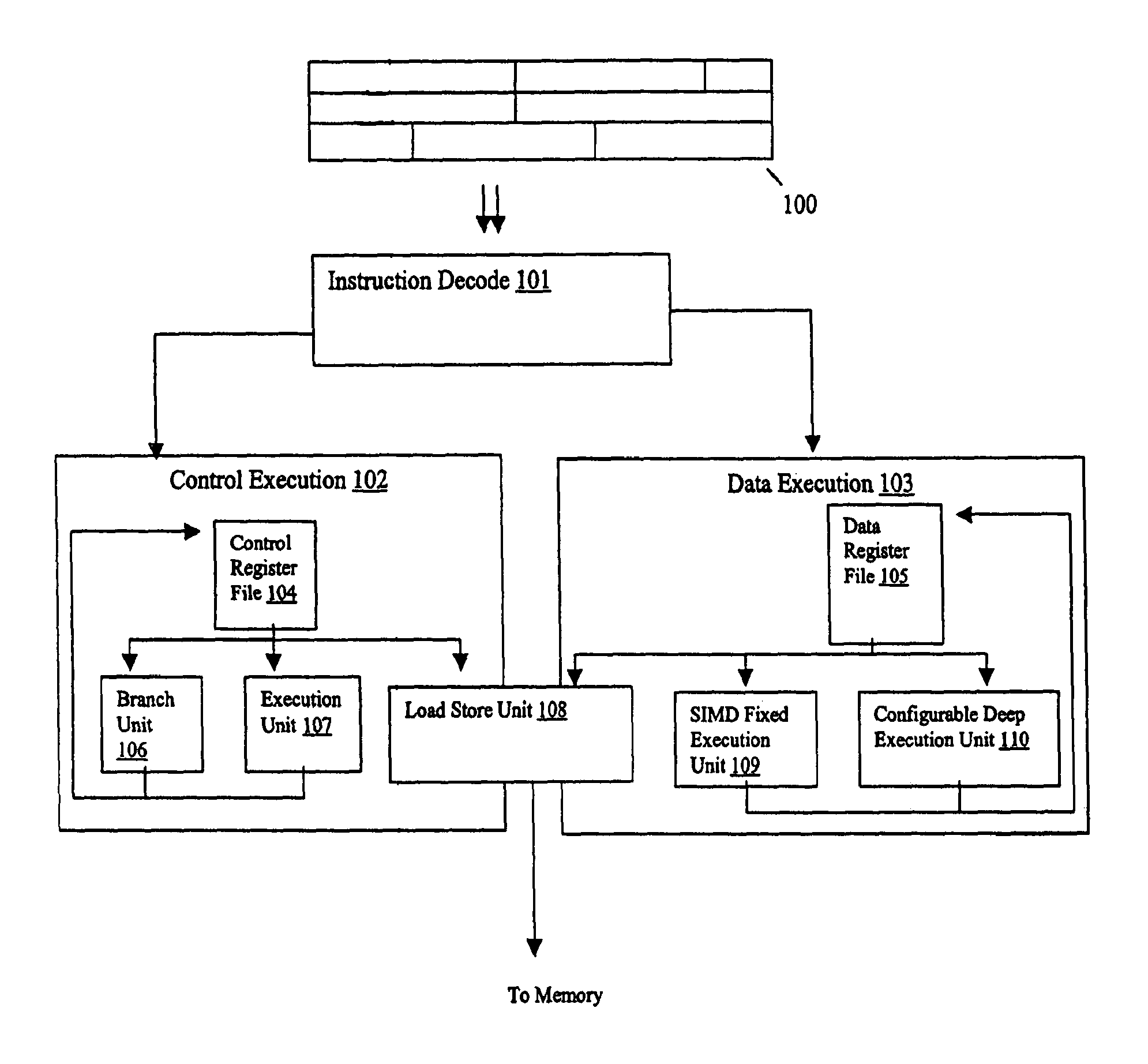

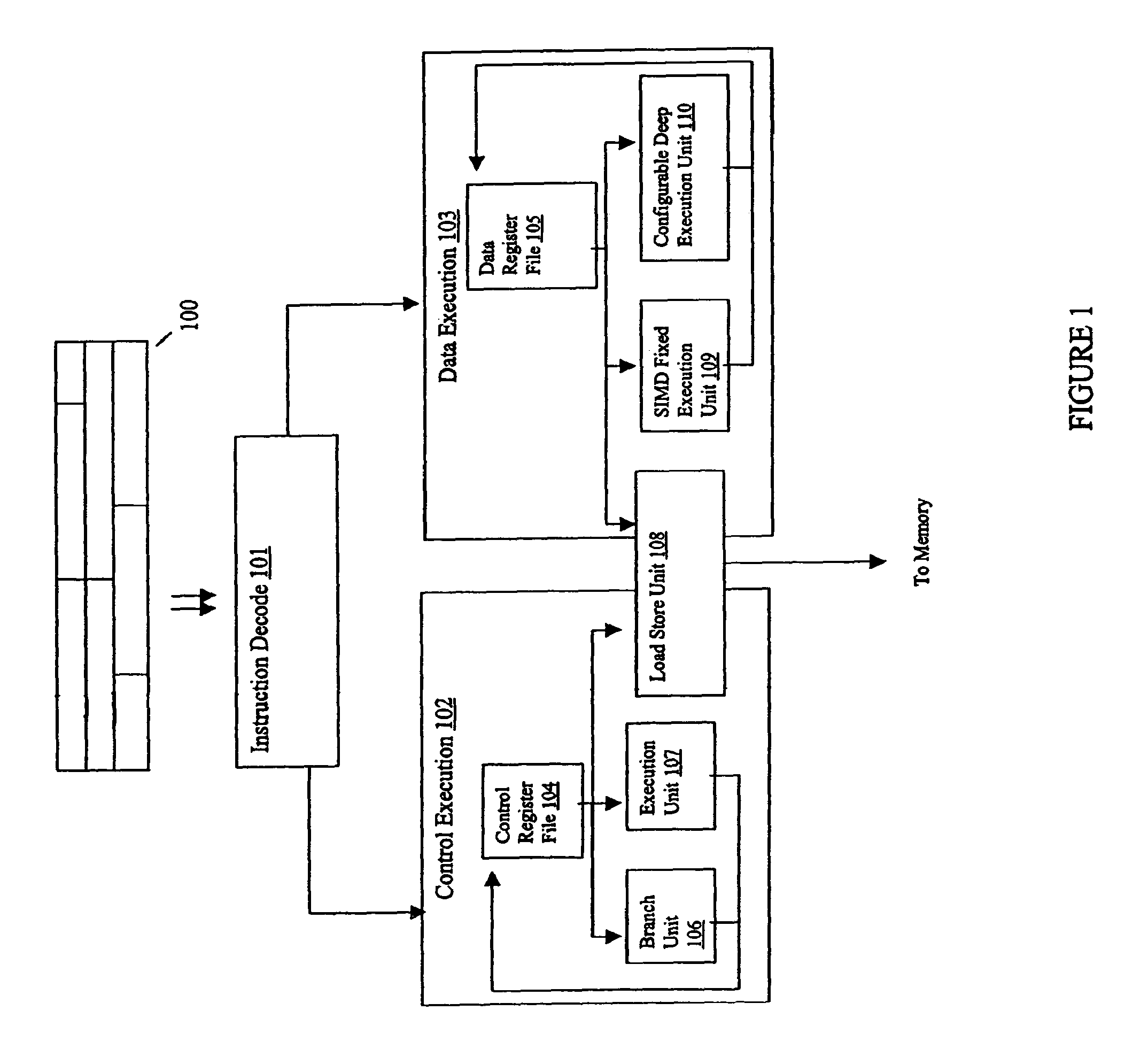

Apparatus and method for asymmetric dual path processing

Owner:NVIDIA TECH UK

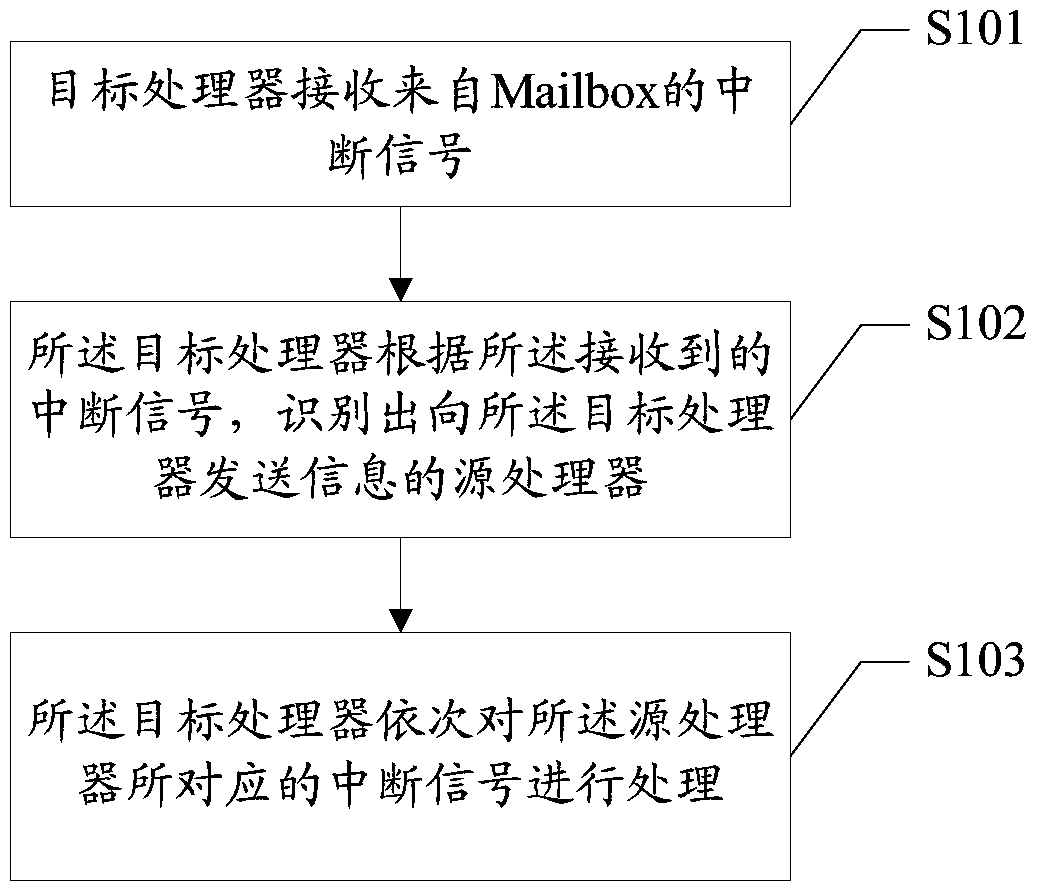

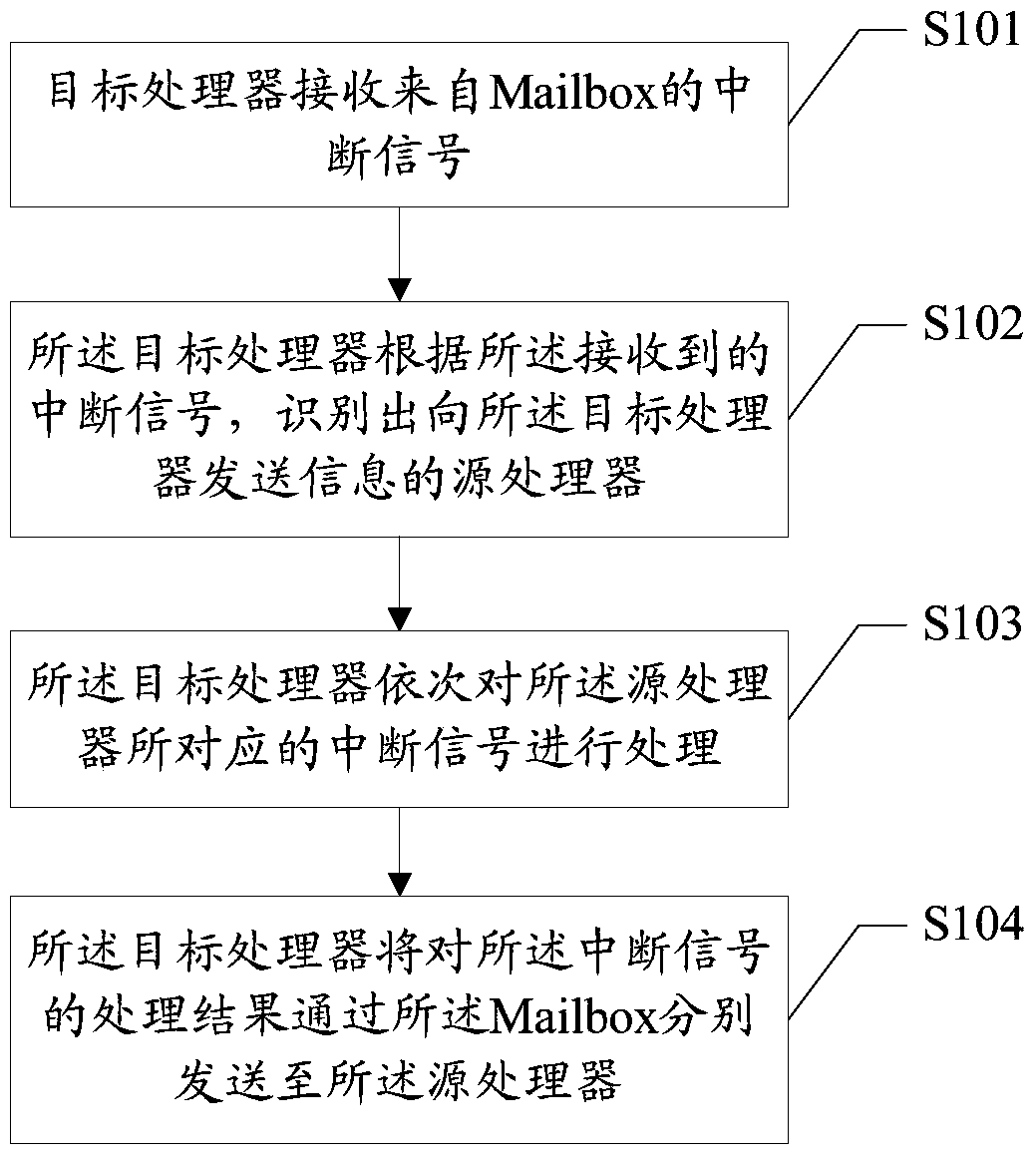

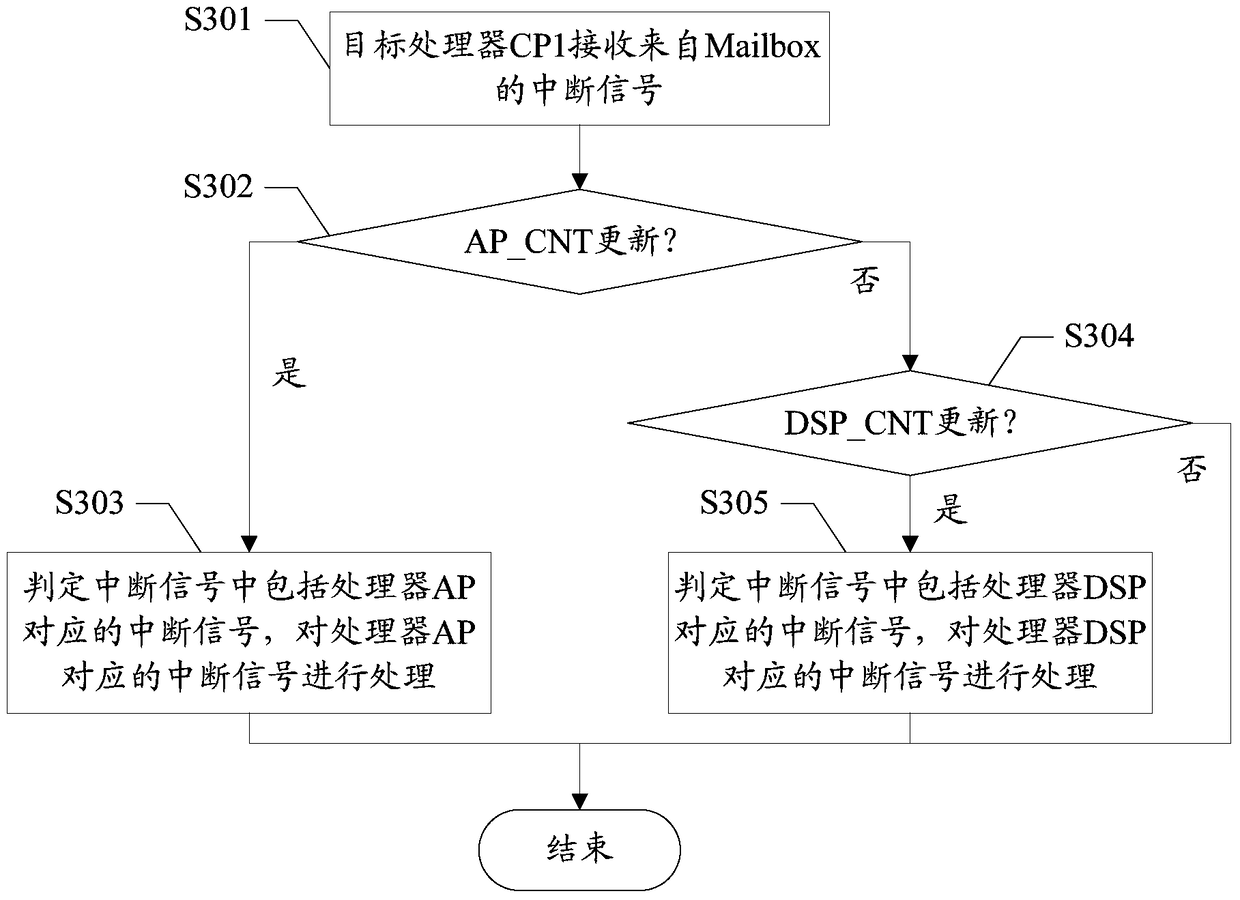

Asymmetric multiprocessor communication method and device

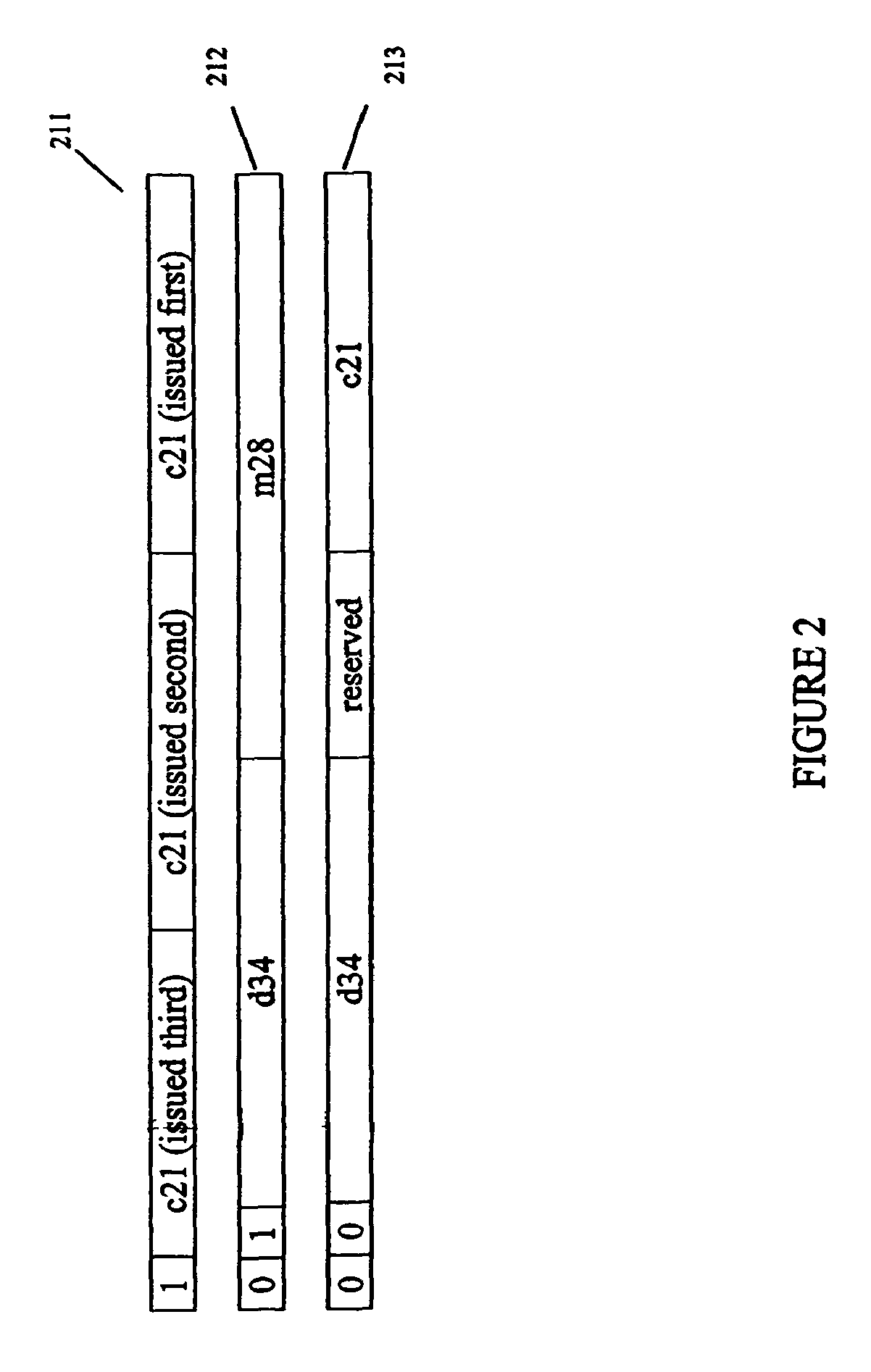

ActiveCN105808498BAvoid pile-up squeeze-and-lose situationsDigital computer detailsElectric digital data processingEmbedded systemAsymmetric multiprocessing

An asymmetric multiprocessor communication method and device, the method comprising: a target processor receiving an interrupt signal from a Mailbox, the interrupt signal being: when the Mailbox receives information sent to the target processor, The generated signal corresponds to the information one by one; the target processor identifies the source processor that sends information to the target processor according to the received interrupt signal; the target processor sequentially The interrupt signal corresponding to the source processor is processed. By adopting the method and device, the accumulation of interrupt signals can be effectively avoided, and the loss of interrupt signals can be prevented.

Owner:SPREADTRUM COMM (SHANGHAI) CO LTD

Image Processing Apparatus, Control Task Allocation Method, And Recording Medium

InactiveCN106484526AReduce performanceReduce power consumptionResource allocationPower supply for data processingElectricityDistribution control

The invention provides an image processing apparatus and the like for using universal firmware in a multi-core CPU image processing apparatus, even a performance priorty mode and electricity saving priorty mode and different modes is set. An image processing apparatus includes: a multi-core CPU having multiple cores; a selector that selects either a first mode or a second mode with respect to allocation of control tasks to the cores of the multi-core CPU; and an allocator that allocates control tasks to the cores of the multi-core CPU by the symmetric multiprocessing technology when the first mode is selected by the selector, and that allocates control tasks to the cores of the multi-core CPU by the asymmetric multiprocessing technology when the second mode is selected by the selector.

Owner:KONICA MINOLTA INC

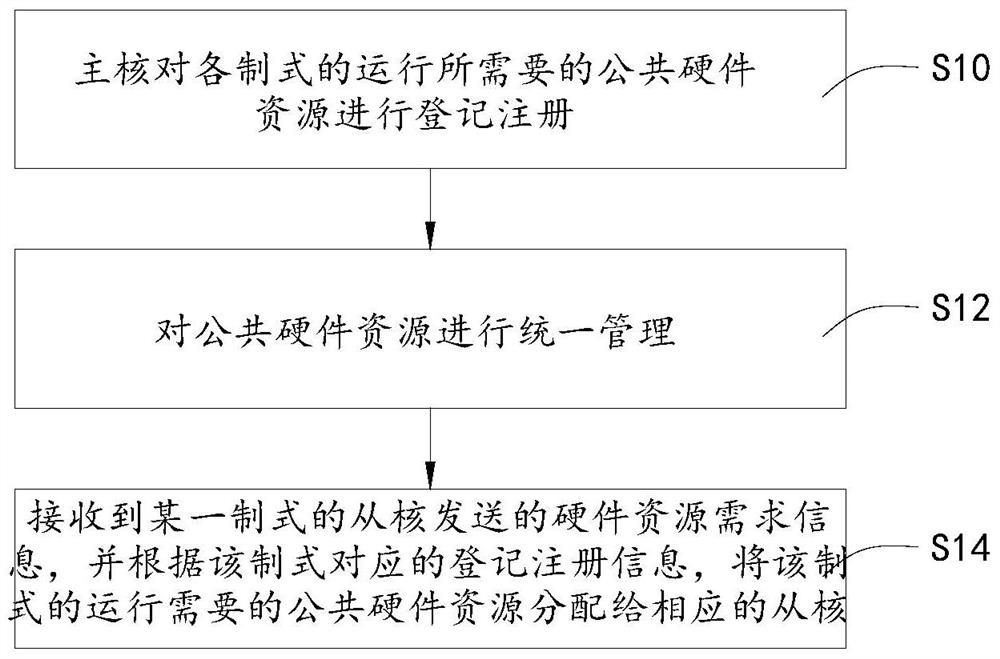

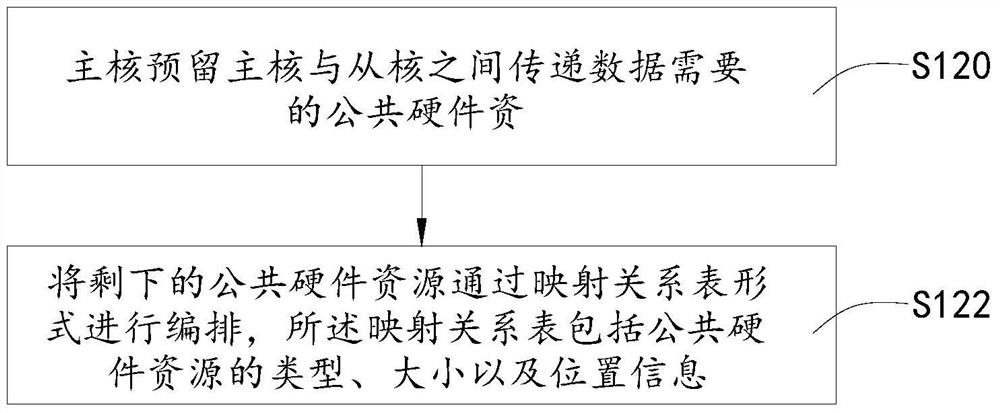

Multi-core heterogeneous system and its hardware resource management method

ActiveCN106919452BAvoid wastingResource allocationDigital computer detailsComputer hardwareEngineering

Provided are an asymmetric multiprocessing system and a method for managing a hardware resource thereof. The method for managing a hardware resource of the asymmetric multiprocessing system comprises: registering, by a master core, a common hardware resource required for an operation of each mode (S10); reading and managing the common hardware resource (S12); and receiving, from a slave core corresponding to one mode, information associated with a hardware resource required for an operation of the mode, and allocating, according to registration information corresponding to the mode, to the slave core a common hardware resource required for the operation of the mode (S14). The method for managing a hardware resource of the asymmetric multiprocessing system can dynamically allocate common hardware resources required by respective modes according to resource allocation requirements of the respective modes, thereby ensuring flexible use of the common hardware resources of the asymmetric multiprocessing system, and preventing waste of the common hardware resources.

Owner:ZTE CORP