A CMOS reference voltage buffer with low output resistance

A reference voltage buffering, low output technology, applied in instruments, regulating electrical variables, control/regulating systems, etc., can solve the problems of tight voltage space, maximum limit of input reference voltage, small equivalent transconductance and output resistance, etc. Achieve the effect of small circuit overhead and low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

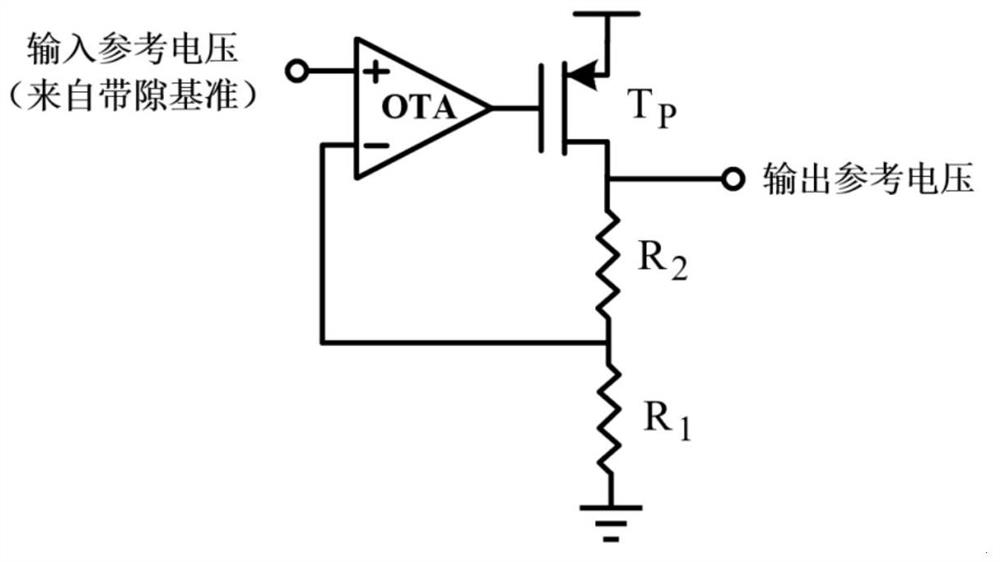

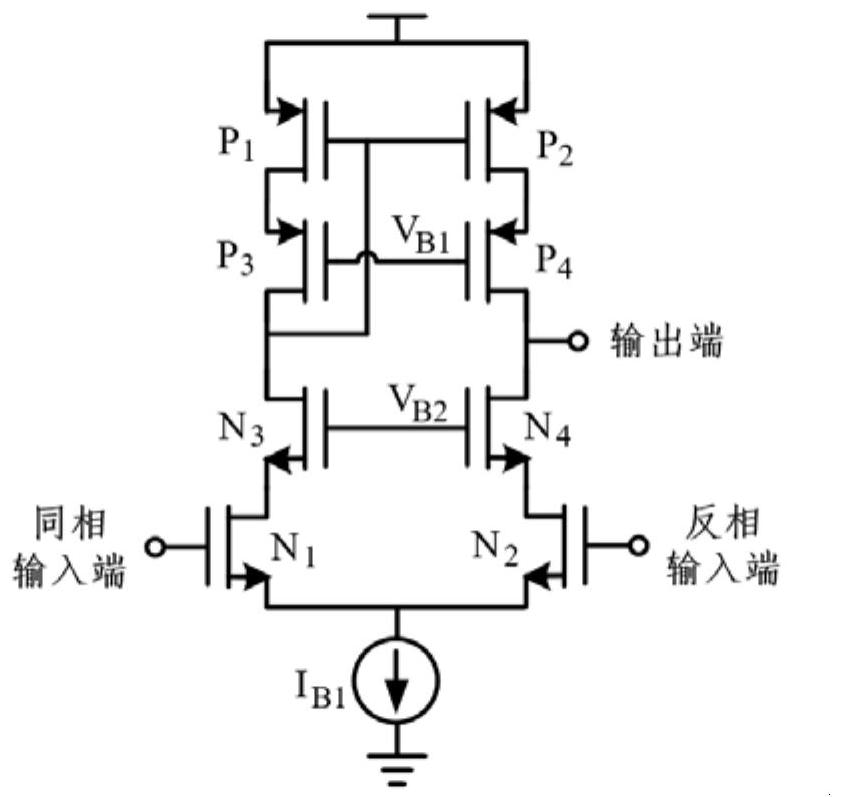

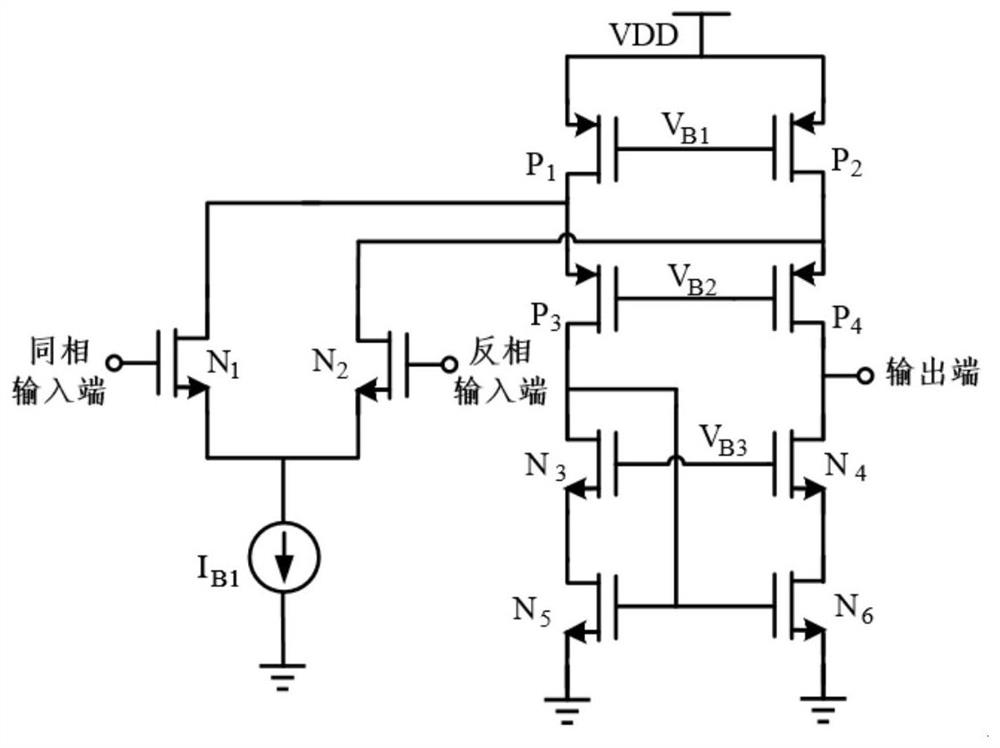

[0034] A CMOS reference voltage buffer with low output resistance, including a single-pole high-gain OTA, a power transmission PMOS transistor Tp, and a first feedback resistor R 1 and the second feedback resistor R 2 , wherein the non-inverting input terminal of the single-pole high-gain OTA inputs the reference voltage, and the inverting input terminal is connected to the first feedback resistor R 1 one end and the second feedback resistor R 2 one end, the first feedback resistor R 1 the other end of the ground, the second feedback resistor R 2 The other end of the power transmission PMOS transistor Tp is connected to the drain and outputs a reference voltage, the source of the power transmission PMOS transistor Tp is connected to the voltage source, and the gate is connected to the output terminal of the single-pole high-gain OTA. see Figure 4 As shown, the single-pole high-gain OTA includes a voltage source VDD, a first bias current source I B1 , the second bias curr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More