AXI bus structure and chip system

A bus structure and bus technology, applied in transmission systems, bus networks, digital transmission systems, etc., can solve the problems of chip congestion and large number of interconnected bus lines, and achieve the effect of reducing the number and eliminating congestion problems.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

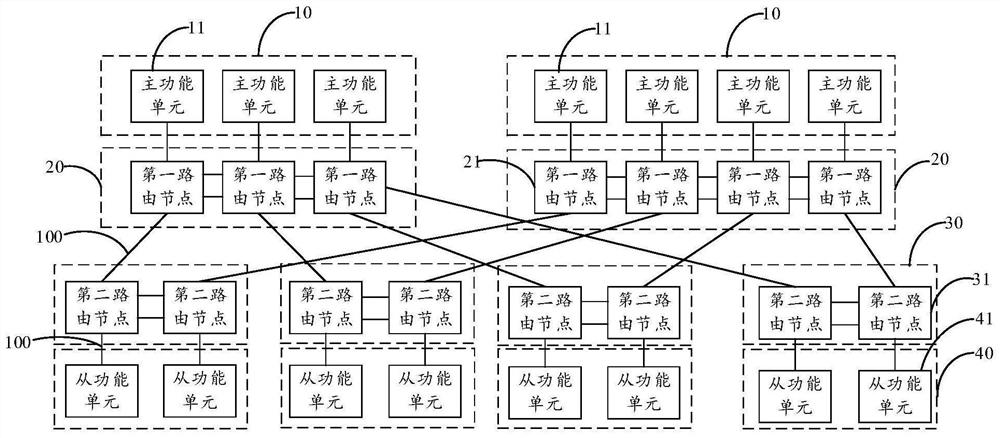

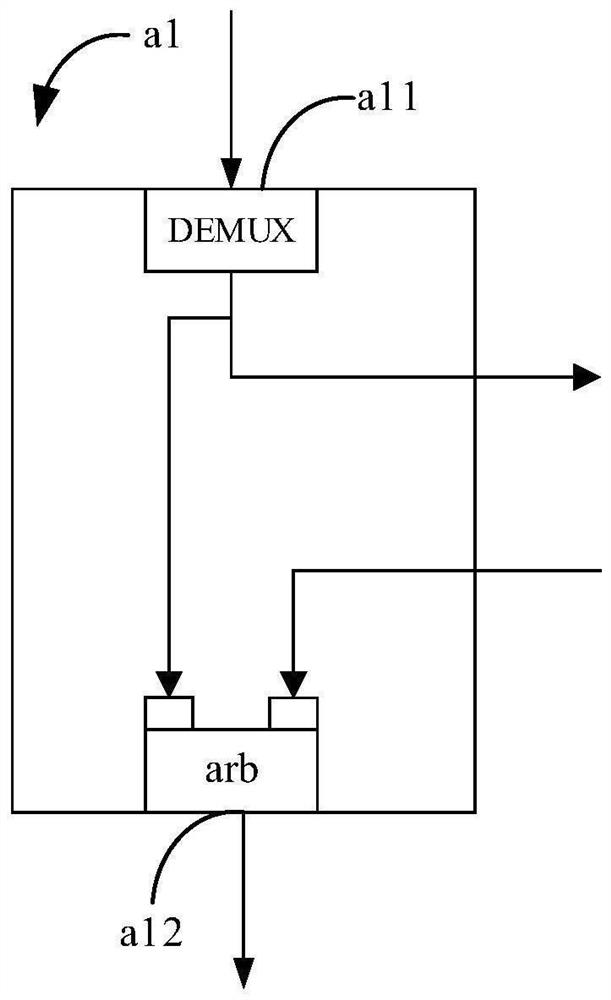

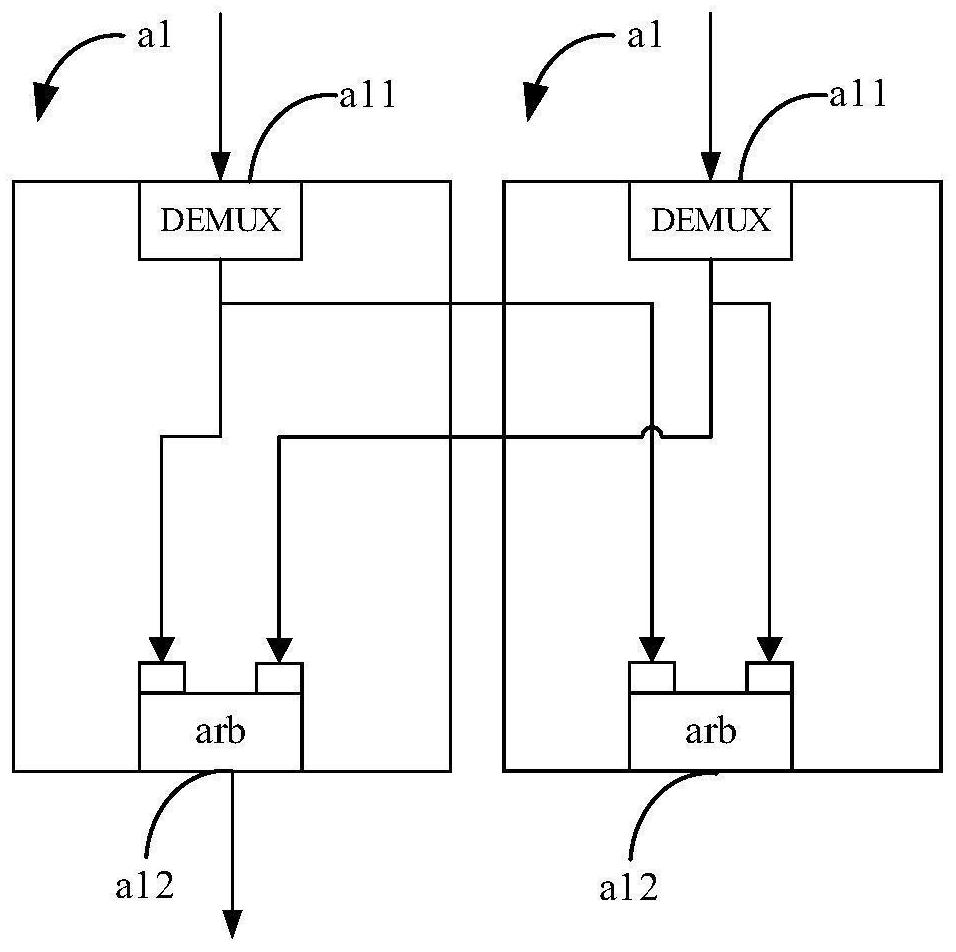

[0043] The technical solutions in the embodiments of the present application will be clearly and completely described below in conjunction with the drawings in the embodiments of the present application.

[0044]In the description of this application, it should be noted that the orientation or positional relationship indicated by the terms "inner", "outer", etc. is based on the orientation or positional relationship shown in the drawings, or the usual placement of the application product when it is used. Orientation or positional relationship is only for the convenience of describing the present application and simplifying the description, and does not indicate or imply that the referred device or element must have a specific orientation, be constructed and operated in a specific orientation, and thus should not be construed as limiting the present application. In addition, the terms "first", "second", etc. are only used for distinguishing descriptions, and should not be constr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More