Noise suppression high-voltage level shift circuit based on delay self-locking

A level shifting circuit and noise suppression technology, which is applied in the direction of logic circuit coupling device, logic circuit connection/interface arrangement, reliability improvement and modification, etc., can solve problems such as occupying a large layout area, high technical threshold, and increasing product cost. , to achieve high reliability and application value, suppress the transmission path, and occupy a small area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

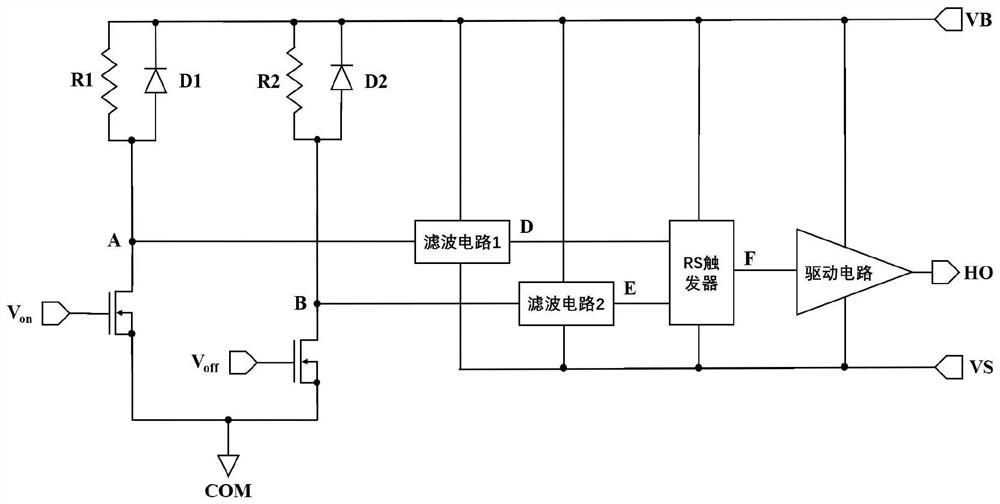

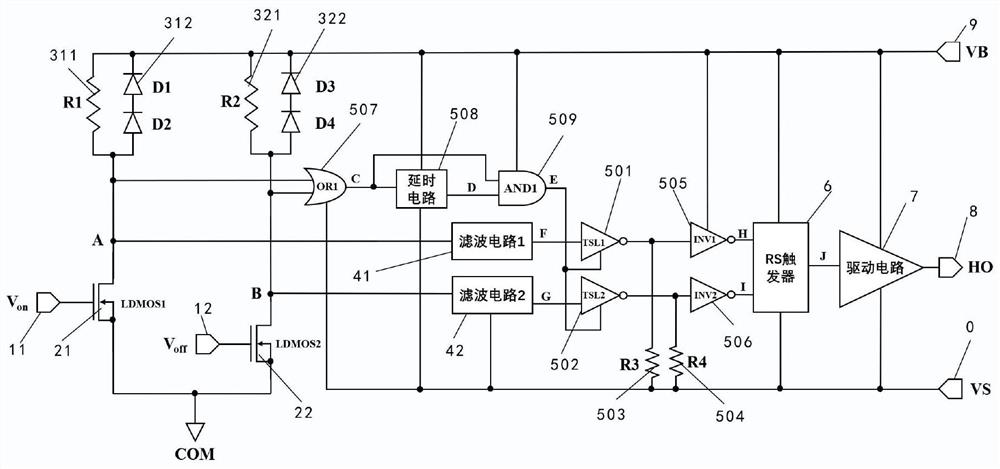

[0022] Such as image 3As shown, a noise suppression high-voltage level shift circuit based on delay self-locking is characterized in that it includes an input port 1, a level shift circuit 2, a voltage clamp circuit 3, a filter circuit 4, and a delay self-locking circuit 5. RS flip-flop 6, drive circuit 7, output port 8, high voltage bias port 9 and high voltage floating ground port 0; input port 1 includes first input port 11 and second input port 12; level shift circuit 2 includes the first An LDMOS transistor 21, a second LDMOS transistor 22; the voltage clamp circuit 3 includes a first clamp circuit 31 and a second clamp circuit 32; the first input port 11 is connected to the gate of the first LDMOS transistor 21; the first LDMOS transistor The source of 21 is grounded, and the drain of the first LDMOS transistor 21 is connected to the high voltage bias port 9 through the first clamp circuit 31; the second input port 12 is connected to the gate of the second LDMOS transis...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More