Automatic wiring method and device of chip top layer long and narrow channel and storage medium

An automatic wiring, narrow and long channel technology, applied in special data processing applications, instruments, electrical digital data processing and other directions, can solve problems such as winding congestion, and achieve the effect of solving local winding congestion and alleviating insufficient winding resources.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

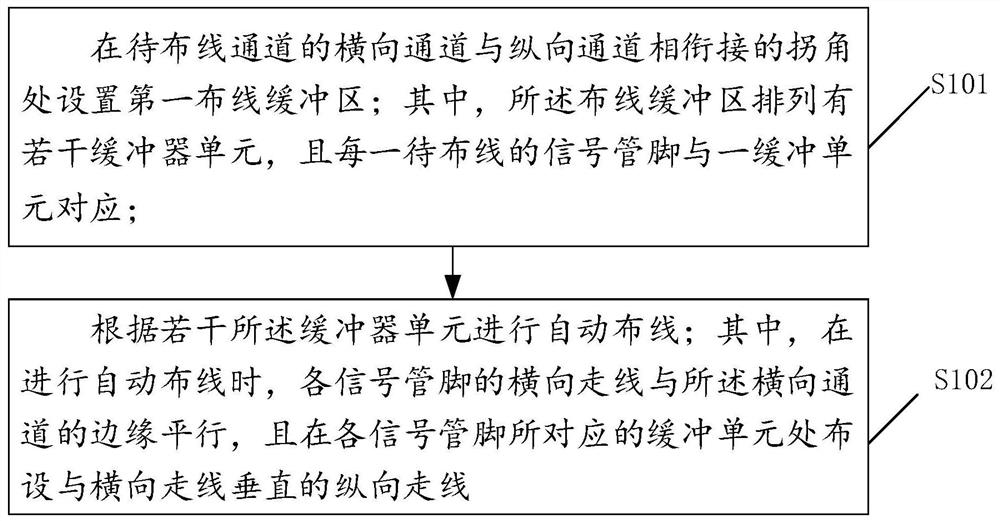

[0039] Such as figure 2 As shown, an embodiment of the present invention provides a method for automatic routing of long and narrow channels on the top layer of a chip, including:

[0040] Step S101: Set a first wiring buffer at the corner where the horizontal channel and the vertical channel of the channel to be wired are connected; wherein, the wiring buffer is arranged with a number of buffer units, and each signal pin to be wired is connected to a The buffer ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More