Interface conversion circuit, multi-chip interconnection system and test method thereof

An interface conversion and interconnection system technology, applied in the field of chip testing, can solve the problems of complex test vectors, poor versatility, and poor flexibility, and achieve the effect of improving versatility and flexibility, accurate and effective testing, and reducing data transmission.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, but not to limit the present invention. In addition, it should be noted that, for the convenience of description, only some structures related to the present invention are shown in the drawings but not all structures.

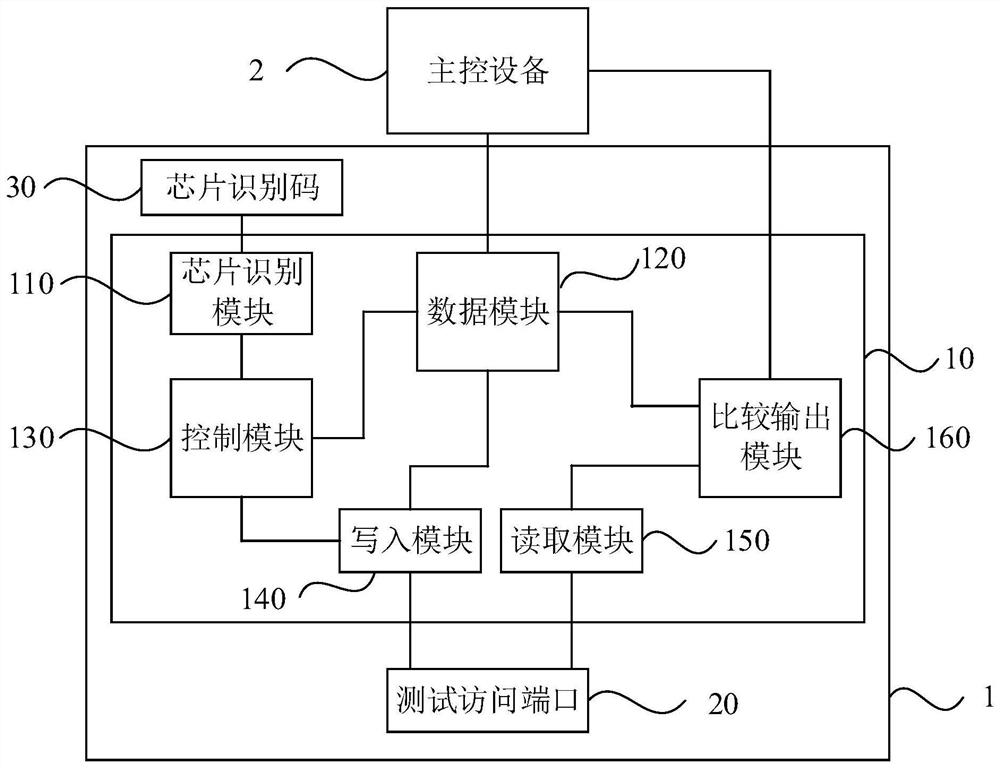

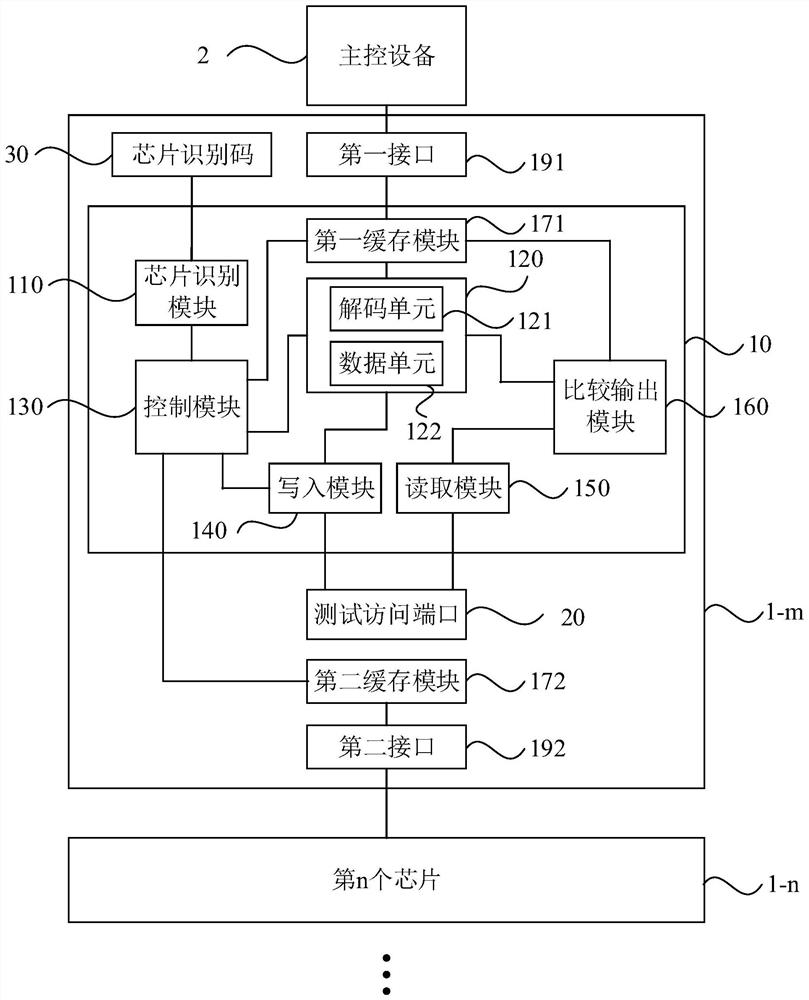

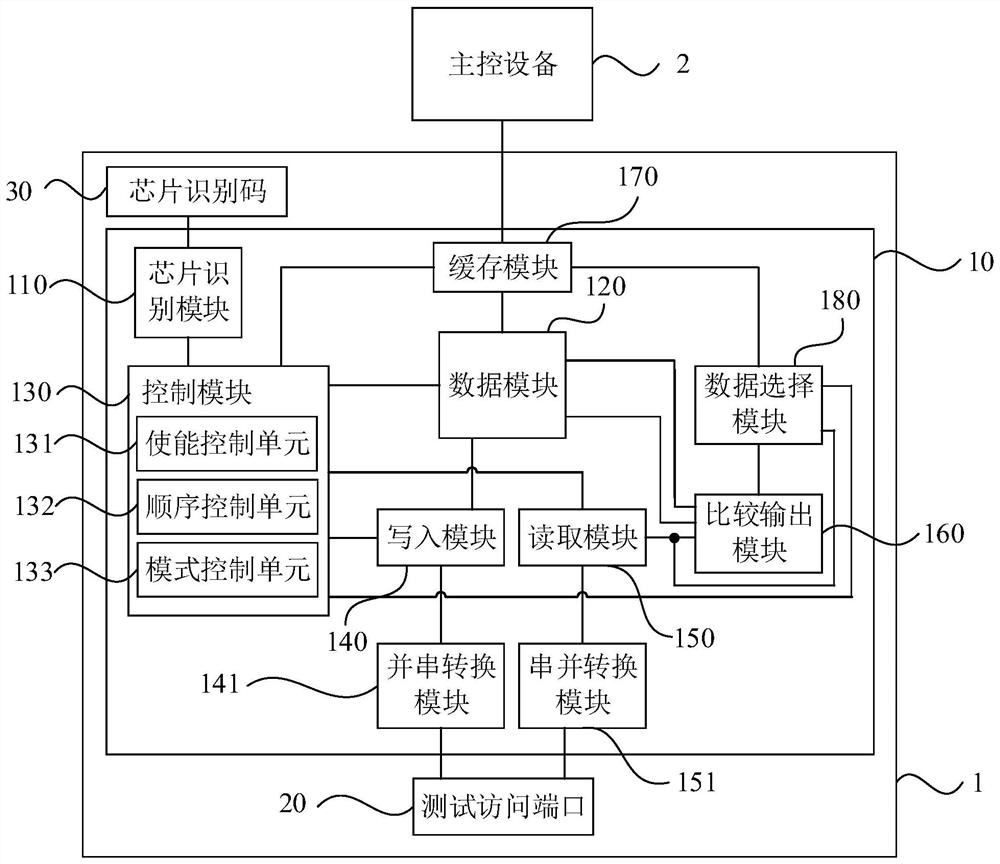

[0044] The embodiment of the present invention provides an interface conversion circuit, which is placed inside the chip and used for chip testing. figure 1 It is a schematic structural diagram of an interface conversion circuit provided by an embodiment of the present invention. seefigure 1 , the chip 1 is a chip in the multi-chip interconnection system, and the chip 1 contains a chip identification code 30, and the chip identification code 30 is used to indicate the ID of the chip (such as the number of the chip...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More