FPGA-based I3C logic controller implementation method, I3C read-write test device and I3C read-write test system

A technology of logic controller and implementation method, applied in general control system, control/regulation system, program control, etc., can solve problems such as inability to test camera modules

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

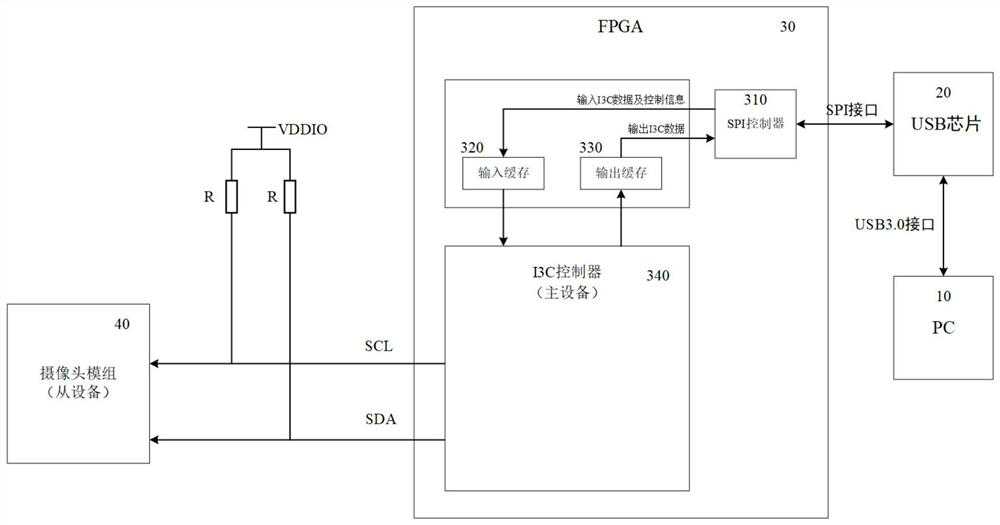

[0071] Such as figure 1 As shown, the present application provides a kind of I3C reading and writing test system, including PC upper computer 10, USB chip 20, FPGA30, I3C slave device (here is camera module) 40; USB module 20 is connected with upper computer 10 through USB line , used to transmit data between host computer 10 and USB chip 20; USB chip 20 is connected to FPGA 30 through SPI bus, used for data transmission between USB chip 20 (USB3.0 chip is used in this solution) and FPGA 30, FPGA 30 The SPI controller 310 is implemented by FPGA internal logic. The USB chip 20 is connected to the PC host computer 10 through a USB bus.

[0072] The SPI controller 310 receives the control command sent from the PC host computer 10 and writes it into the input buffer 320; the control information includes a start signal, an end signal, a master device waiting for a slave device response flag signal, a write data flag signal, and a read data flag signal. Flag signal, read data stop...

Embodiment 2

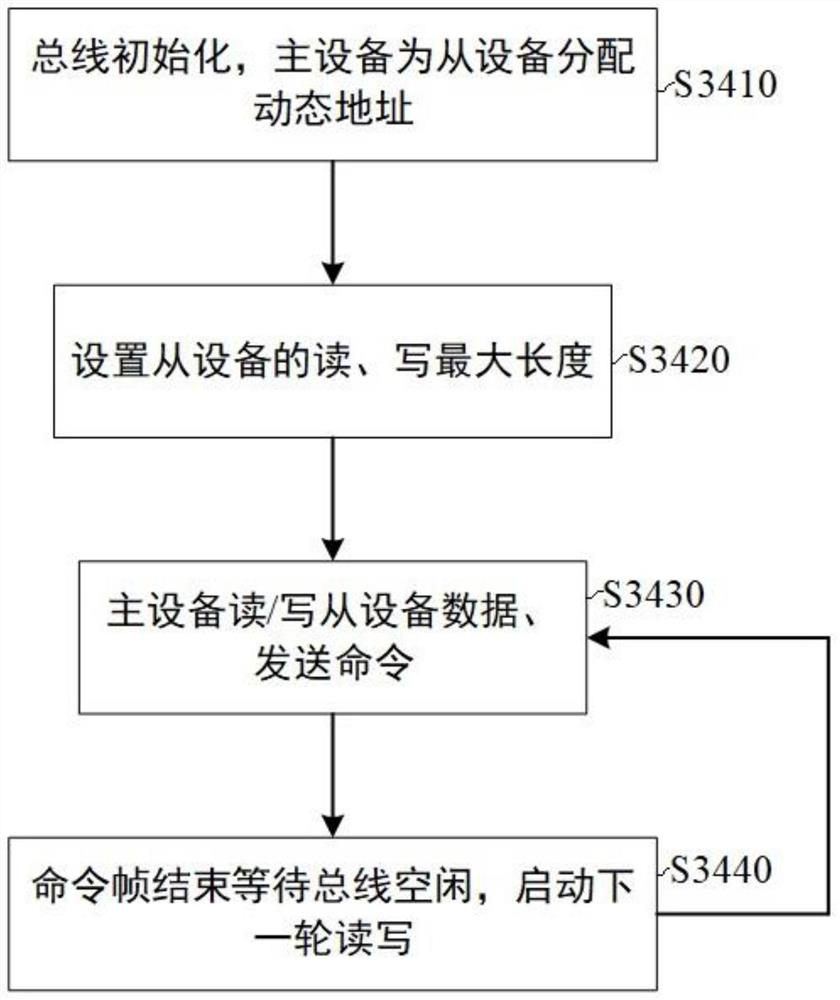

[0078] On the basis of Embodiment 1, this embodiment provides a method for implementing an FPGA-based I3C logic controller, including:

[0079] S100, receiving a control command output by the host computer based on the encapsulated I3C protocol;

[0080] Based on the user's operation instructions, the upper computer sends control instructions to the I3C main device FPGA30 according to the packaged I3C protocol, and writes the I3C read / write control commands and data into the FPGA internal input buffer through the USB3.0 interface and the SPI interface of the USB chip.

[0081] S200, assigning a dynamic address to a slave device with an I3C read / write function according to the control instruction, and setting a maximum length value of data that can be read / written once;

[0082] Based on the I3C control command of the upper computer, the I3C master device FPGA assigns a dynamic address (Dynamic Address) to the slave device with I3C read and write functions; the I3C bus includes...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More