Device and method for reducing precision loss

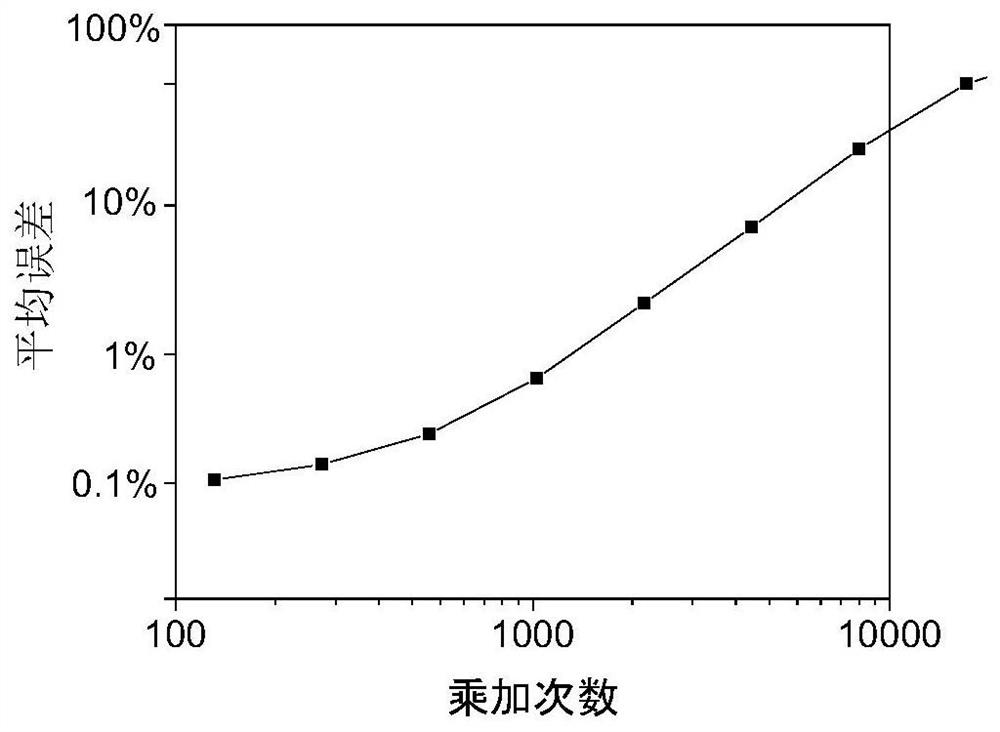

A precision and addition operation technology, applied in the field of devices that reduce precision loss, to achieve the effect of reducing calculation errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0045] Example 1, such as Figure 5 As shown, a device for reducing precision loss of the present invention includes a module A and a module B. After module A executes a multiplication and addition operation task, it passes the multiplication and addition value to module B, module A is cleared, and module A continues to perform the next multiplication and addition operation task, and passes the multiplication and addition value to module B and the previous multiplication and addition value Accumulation is performed, module A is cleared, and after execution in sequence, multiple multiplication and addition operations are completed, and the accumulated value of module B is output.

[0046] In a possible implementation manner, the multiplication-accumulation value in module A is stored in register 1, and the accumulation value in module B is stored in register 2. Clock 1 counts the number of multiplication and addition operations of module A, and clock 2 counts the number of acc...

Embodiment 2

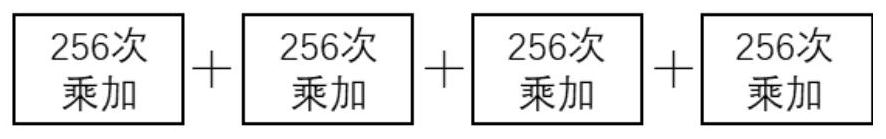

[0048] Example 2, such as Figure 6 As shown, a device for reducing precision loss in the present invention includes N modules A and one module B.

[0049] In a possible implementation manner, the multiplication and addition values in the N modules A are respectively stored in a register i, where i represents a sequence number, and i=1, 2, . . . , N. For example, the multiply-accumulate value of the first module A is stored in register 1, the multiply-accumulate value of the second module A is stored in register 2, ..., the multiply-accumulate value of the Nth module A is stored in register N.

[0050] In a possible implementation manner, the clock i counts the times of multiplication and addition operations of the N modules A respectively, where i represents a serial number, and i=1, 2, . . . , N. For example, clock 1 counts the number of multiplication and addition operations of the first module A, clock 2 counts the number of times of multiplication and addition operatio...

Embodiment 3

[0053] Example 3, such as Figure 7 As shown, a device for reducing precision loss in the present invention includes N modules A and one module B. The difference from Embodiment 2 is that the device also includes: a register L, which is located before the selector MUX, and stores the multiplication and addition values stored in all registers i, and the gate MUX sequentially selects the multiplication and addition values in the register L and transmits to module B. Inserting an additional register L in the gate MUX can realize the sequential gate of register i and seamless subtask switching, simplify the timing control in the multiplier-adder array, and reduce the complexity.

[0054] In a possible implementation, N modules A can use the same clock i to count the number of multiplication and addition operations (for example, clock 1, clock 2, ..., clock N all use clock 1), and the multiplication of N modules A After the number of addition operations reaches the first pres...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com