Memory control method and device

A memory control and memory chip technology, applied in the field of communications, can solve problems such as increased interrupt frequency and increased response burden.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] Preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings, wherein the accompanying drawings constitute a part of the application and together with the embodiments of the present invention are used to explain the principle of the present invention and are not intended to limit the scope of the present invention.

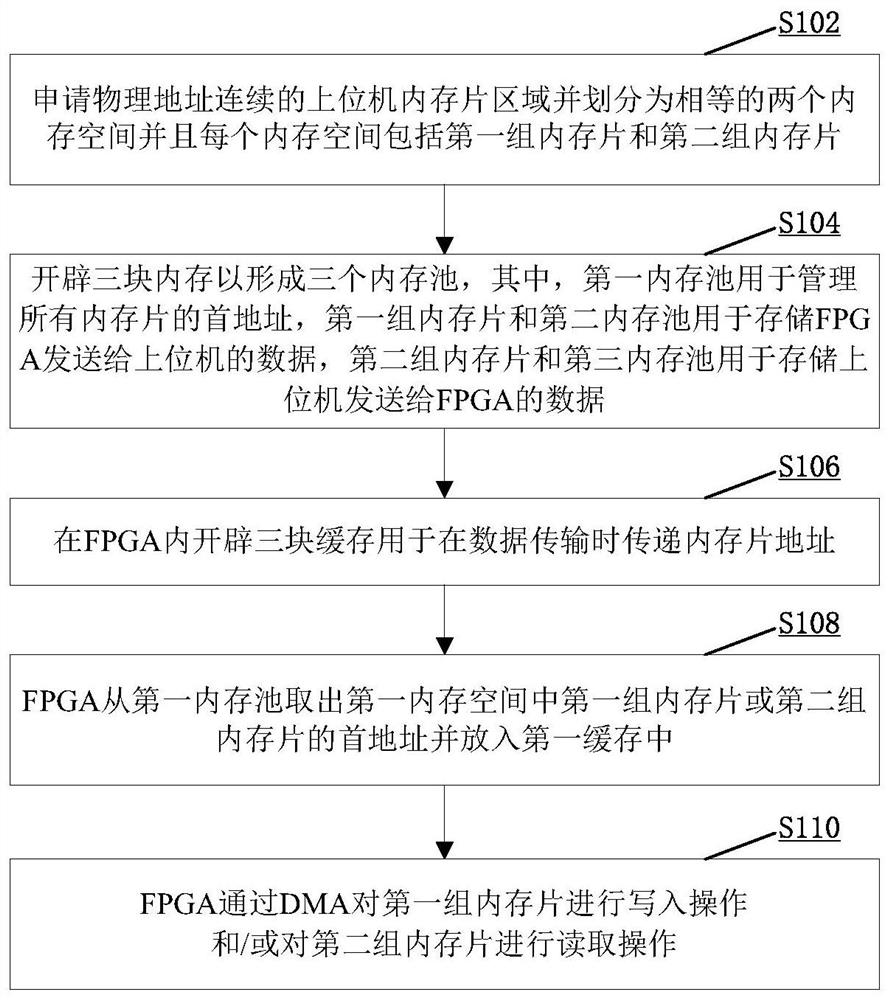

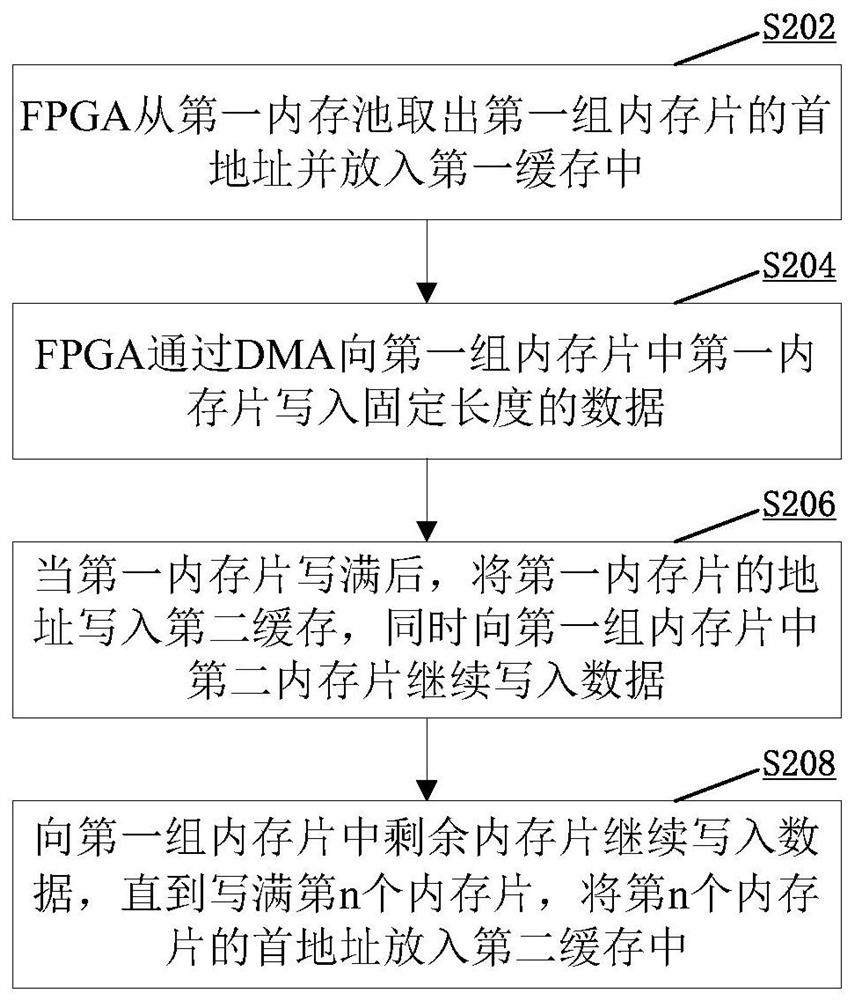

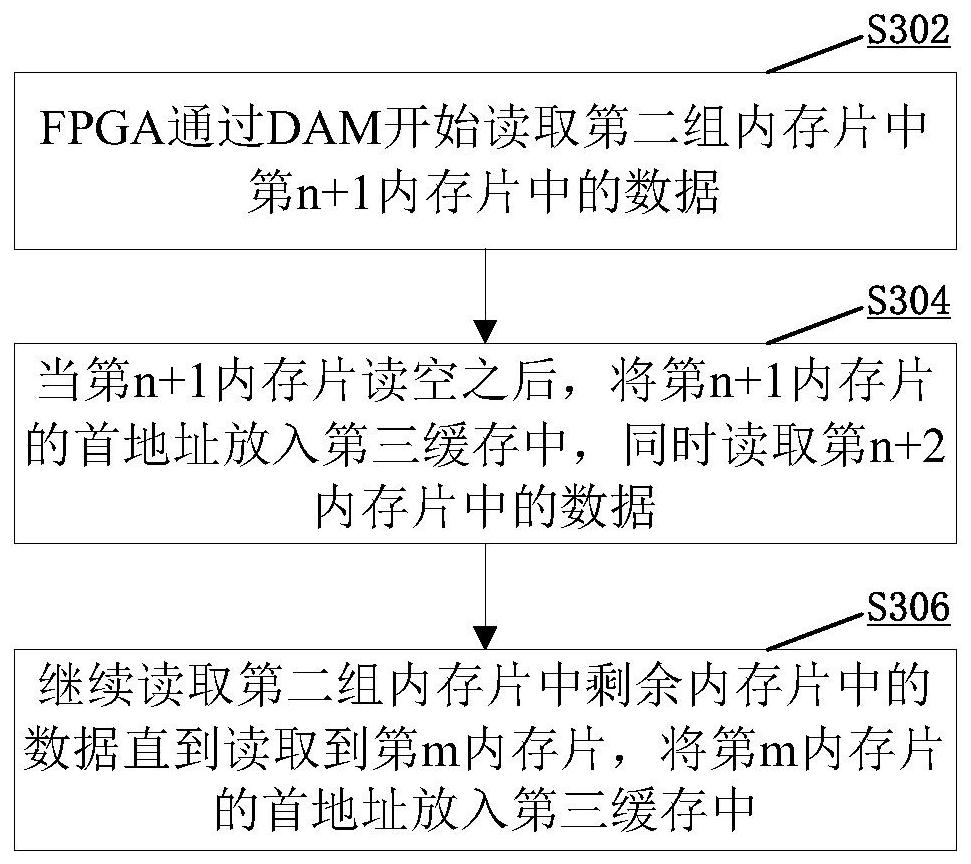

[0032] A specific embodiment of the present invention discloses a memory control method. like figure 1As shown, the memory control method includes: step S102, apply for a host computer memory slice area with continuous physical addresses and divide it into two equal memory spaces and each memory space includes a first group of memory slices and a second group of memory slices; step S104 , open up three pieces of memory to form three memory pools, among which, the first memory pool is used to manage the first address of all memory slices, the first group of memory slices and the second memory ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More