System-level packaging method and packaging structure thereof

A technology of system-level packaging and interconnection structure, which is applied in the field of system-level packaging method and its packaging structure, can solve the problems of poor packaging effect, large package size, and difficult process, so as to reduce height, reduce bonding stress, simplify The effect of craft

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

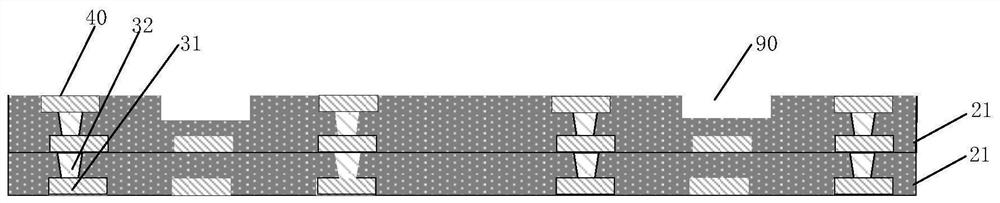

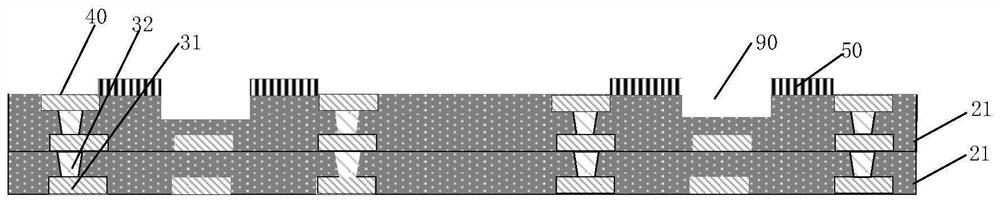

[0035] refer to Figure 1 to Figure 5 , this embodiment 1 provides a system-in-package method, including the following steps:

[0036] S01: Provide a PCB board, the surface of the PCB board has a plurality of grooves 90, and the surface of the PCB board is formed with a plurality of exposed first pads 40;

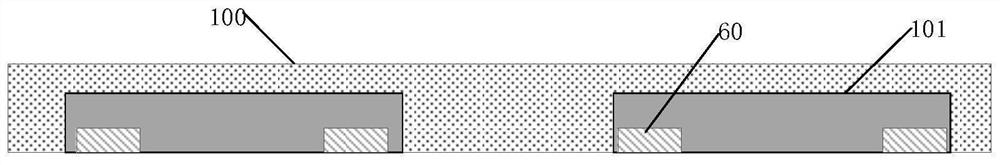

[0037] S02: Provide a device wafer 100, the device wafer 100 includes a plurality of first chips 101, and a plurality of exposed second pads 60 are formed on the surface of the first chips 101;

[0038] S03: bonding the device wafer 100 to the PCB board through the connection layer, the first pad 40 is opposite to the second pad 60 to form a gap 70a;

[0039] S04: The connection layer has a first opening at the position opposite to the groove 90, and the first opening and the groove 90 are jointly surrounded by the connection layer, the device wafer 100 and the PCB board to form a cavity 51, and the cavity 51 serves as the first chip 101 working chamber;

[0040] S05 : Fo...

Embodiment 2

[0077] refer to Image 6 , this embodiment 2 provides a system-in-package method, which is different from embodiment 1 in that: after forming the conductive bump 70, it also includes forming a via hole 80, the via hole 80 penetrates the device wafer 100 and extends to the first chip 101 superior.

[0078] In the present invention, a communication hole 80 is opened on the device wafer 100, which penetrates the device wafer 100 and extends to the first chip 101, so that the first chip 101 is exposed to the external atmosphere, thereby improving the working performance of the packaging structure and improving its utilization rate , and can be used in more occasions, making it more flexible.

[0079] Specifically, in this embodiment, at least one device wafer 100 is provided with a via hole 80 on the surface.

[0080] The other parts are the same as those in Embodiment 1, and will not be repeated here.

Embodiment 3

[0082] refer to Figure 5, Embodiment 3 provides a system-in-package structure, including:

[0083] A PCB board, the PCB board includes opposite front and back sides, the front side of the PCB board has a groove 90, and there are a plurality of exposed first welding pads 40 on the front side of the PCB board;

[0084] A device wafer 100, the device wafer 100 has a first chip 101, the surface of the device wafer 100 has a plurality of exposed second pads 60, the first pad 40 is arranged opposite to the second pad 60, the device wafer 100 Bonding on the surface of the PCB board through the connection layer, the first welding pad 40 is arranged opposite to the second welding pad 60;

[0085] The connection layer has a first opening at a position opposite to the groove 90, and the first opening and the groove 90 are jointly surrounded by the device wafer 100 and / or the PCB board to form a cavity 51, and the cavity 51 serves as a working cavity for the first chip 101;

[0086] Th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More