Wafer-level system packaging structure and method

A system packaging, wafer-level technology, applied in microstructure technology, microstructure devices, manufacturing microstructure devices, etc., can solve the problems of low packaging efficiency, large packaging size, and difficult process, so as to improve packaging efficiency and reduce High, simplified process effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

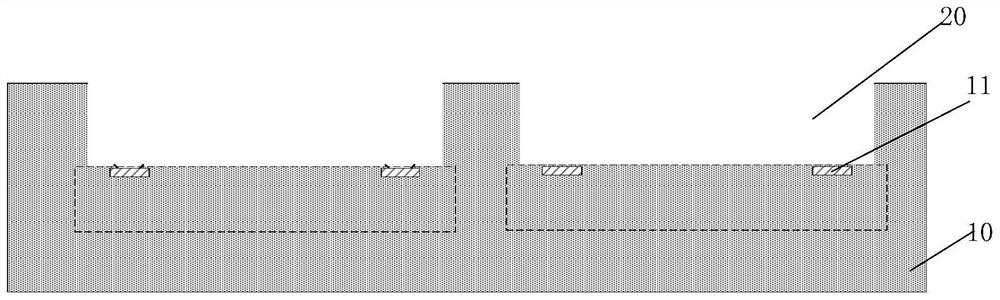

[0031] This embodiment 1 provides a wafer-level packaging method, which includes the following steps:

[0032] S01: Provide a device wafer, the surface of the device wafer has a plurality of exposed first pads, the surface of the device wafer forms a first cavity, and at least part of the first pads are located in the first below the cavity;

[0033] S02: providing a first chip, the surface of the first chip has a plurality of exposed second pads;

[0034] S03: Bond the first chip to the bottom of the first cavity through a connection layer, the connection layer has a first opening, and the first opening is covered by the first chip and / or the device wafer forming a second cavity, the second cavity is used as a working cavity of the first chip, and the first pad is opposite to the second pad to form a gap;

[0035] S04: A first conductive bump is formed in the gap by an electroplating process, and the first bonding pad and the second bonding pad are electrically connected th...

Embodiment 2

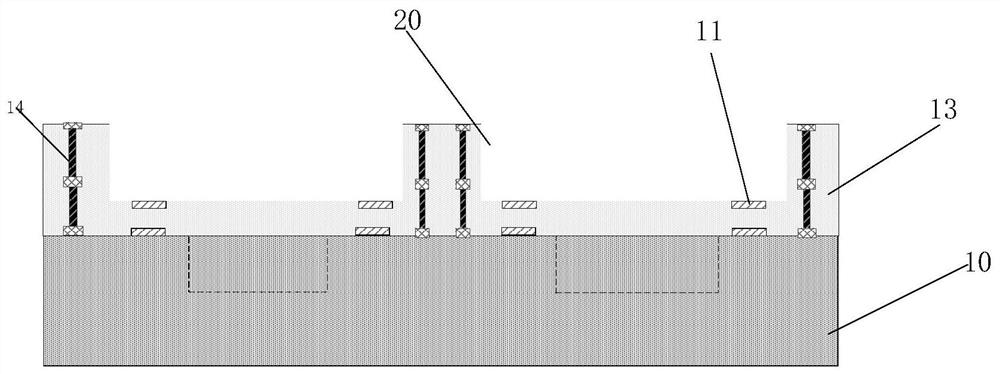

[0086] refer to Figure 11 , the difference from the first embodiment is that the backside of the device wafer 10 further includes a third pad 12 , and the third pad 12 is located on the interconnect structure in the device wafer 10 and on the surface of the second chip 80 . The formed fourth pads 81 are electrically connected, the third pads 12 and the fourth pads 81 are arranged opposite to each other, and are formed between the third pads 12 and the fourth pads 81 during the electroplating process The second conductive bumps 90 . In other embodiments, before or after the first conductive bumps 11 are formed, the third pads 12 and the fourth pads 81 may be connected by conductive materials such as solder balls and conductive pillars.

[0087] The exposed area of the third pad 12 or the fourth pad 81 is 5-200 square microns. Within this range, the pad can be in sufficient contact with the electroplating solution to avoid the influence of insufficient contact between the pa...

Embodiment 3

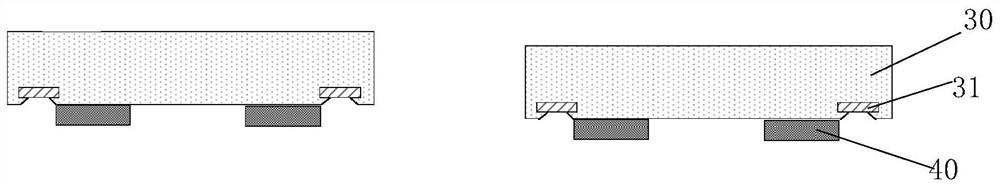

[0089] refer to Figure 12 , and the difference from the first embodiment is that a third chip 60 is bonded on the first chip 30 , and the third chip 60 is electrically connected to the first chip 30 . Specifically, the second surface of the first chip 30 includes a fifth bonding pad 32 , and the fifth bonding pad 32 is electrically connected to the first chip 30 , and the electrical connection may be realized by interconnecting wires inside the first chip 30 . The electrical connection can also be achieved by plugs, which is not limited here. The sixth pad 61 is formed on the surface of the third chip 60, and the fifth pad 32 and the sixth pad 61 are oppositely arranged. According to the electroplating process, a third conductive bump 70 is formed between the fifth bonding pad 32 and the sixth bonding pad 61; the third chip 60 and the first chip 30 can also be electrically connected through an electroless plating process, such as refer to Figure 13 , the third chip 60 and ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| area | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More