Method for automatically correcting electric leakage path of MOS device

A technology of MOS devices and correction methods, which is applied in the direction of instruments, electrical digital data processing, special data processing applications, etc., can solve the problems of not considering leakage path, unsatisfactory correction results, affecting production efficiency, etc., to solve time-consuming and error risks High, improve the level and quality of chip manufacturing, reduce the effect of manpower and time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

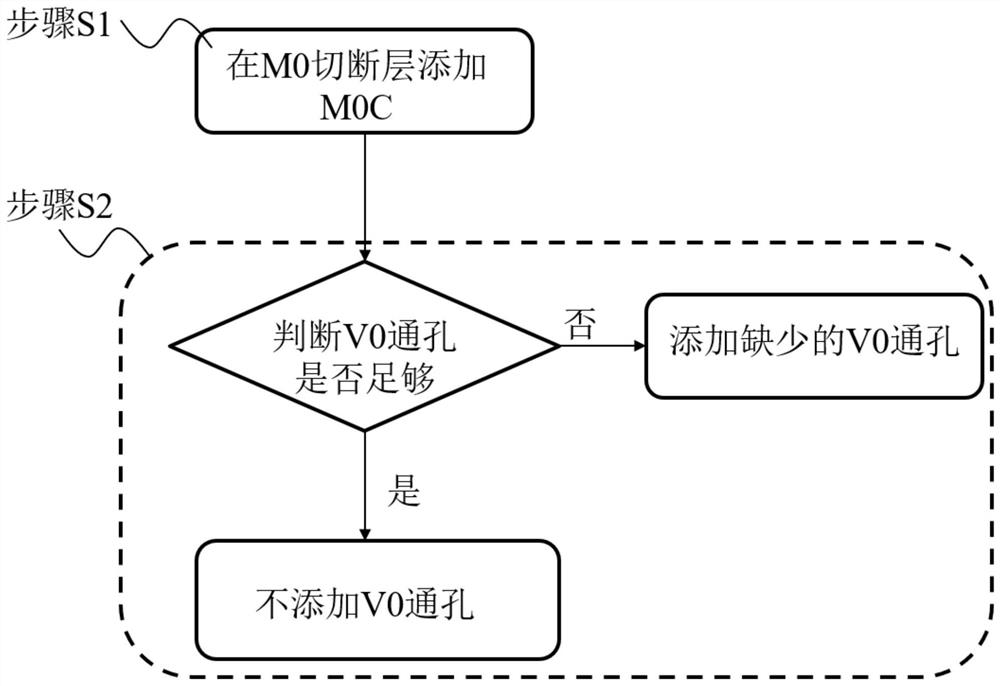

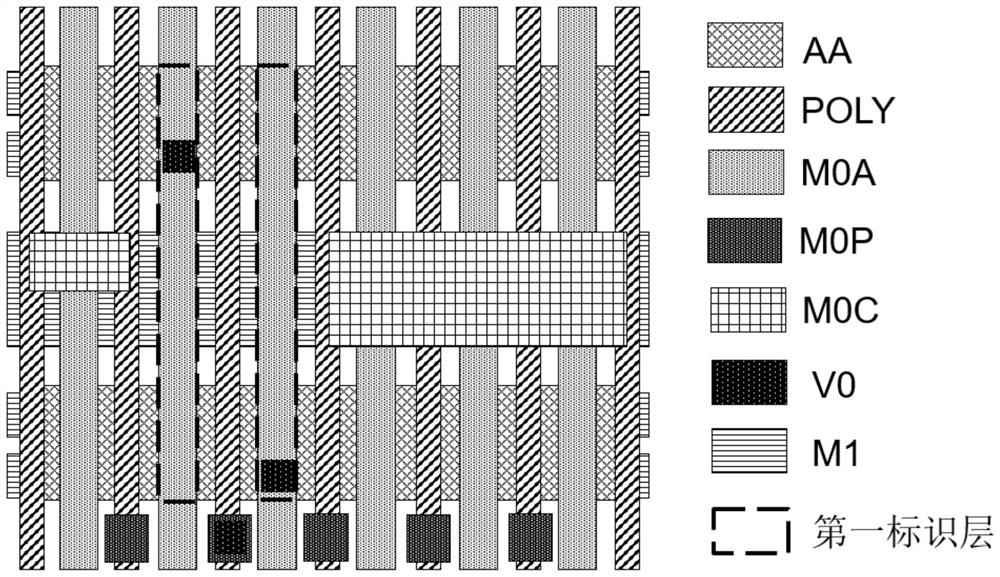

[0026] Such as figure 1 As shown, this embodiment provides a method for automatically correcting the leakage path of a MOS device, including: reading in the layout file, and determining the MOS device to be corrected as the target device; using the preset leakage path correction module to correct the target device Leakage path: In the leakage path correction module, the correction method of the MOS device with leakage path is defined. The correction method of this embodiment is as follows figure 2 As shown, step S1. Add M0C in the M0 cut-off layer, and cut off the M0 connection line to disconnect the source and / or drain of the target device from the source and of other MOS devices (ie floating gate, floating gate) / or the connection of the drain end; step S2. judge whether the source end, the drain end and the gate end of the target device can be respectively connected to the M1 connection line through the existing V0 through hole; if not, then add the missing V0 through hol...

Embodiment 2

[0035] In this embodiment, after the layout file is read in, the method of determining the MOS device to be corrected as the target device is given as an example, as shown in Figure 5 As shown, in step 1. Obtain the MOS device information in the layout file read in; Step 2. Use the preset leakage path screening module to screen whether there is a leakage path in the MOS device; Step 3. Screen the existence of the leakage path The MOS device is used as the target device.

[0036] The preset leakage path screening module defines conditions for judging whether there is a leakage path in the MOS device. The judgment conditions defined in this embodiment include: if there is a source terminal and a drain terminal of a certain MOS device connected together with source terminals and drain terminals of other MOS devices, it is judged that the MOS device is a MOS device with a leakage path; If the source terminal or drain terminal of a certain MOS device is connected to the source te...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More