Processor low-power blocking type time delay method and device and readable medium

A processor and low-power technology, applied in the computer field, can solve the problems of high processor power consumption and waste of processor resources, and achieve the effect of reducing power consumption and saving processor resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

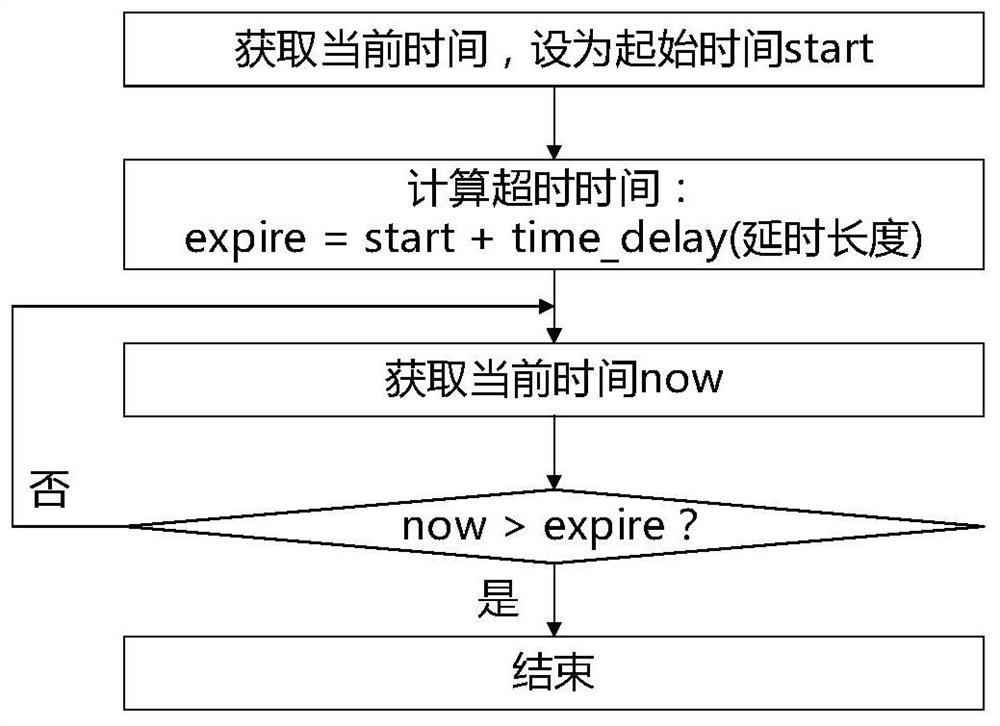

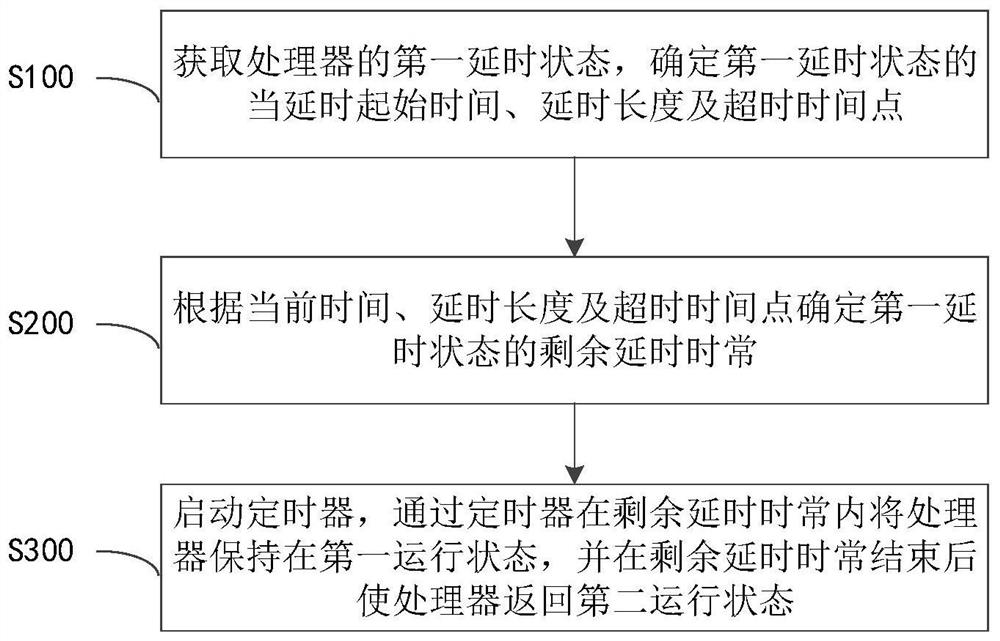

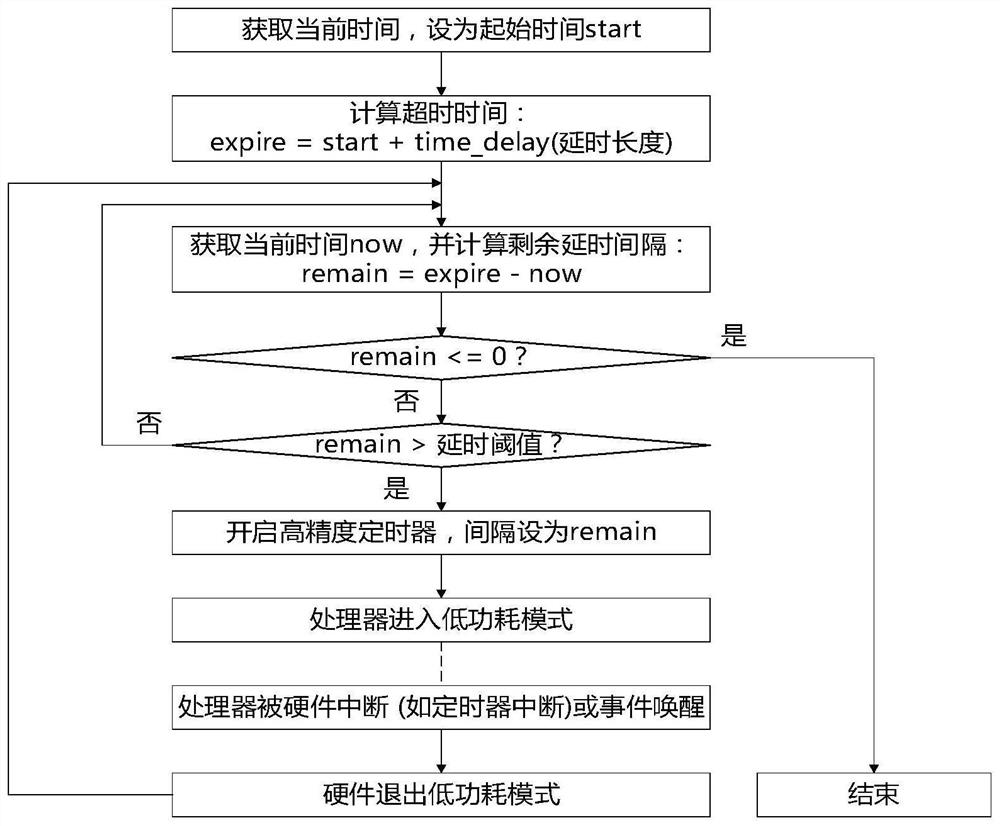

Method used

Image

Examples

Embodiment Construction

[0020] This part will describe the specific embodiment of the present invention in detail, and the preferred embodiment of the present invention is shown in the accompanying drawings. Each technical feature and overall technical solution of the invention, but it should not be understood as a limitation on the protection scope of the present invention.

[0021] In the description of the present invention, several means one or more, and multiple means two or more. Greater than, less than, exceeding, etc. are understood as not including the original number, and above, below, within, etc. are understood as including the original number.

[0022] In the description of the present invention, the continuous labeling of the method steps is for the convenience of review and understanding. In combination with the overall technical solution of the present invention and the logical relationship between each step, adjusting the implementation order between the steps will not affect the tech...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More