4H-SiC metal semiconductor field effect transistor with P-type doped region and recessed buffer layer

A metal semiconductor and field effect transistor technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of reducing effective channel resistance, breakdown voltage drop, breakdown voltage deterioration, etc., to improve breakdown voltage, breakdown The effect of increasing the breakdown voltage and increasing the saturation current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

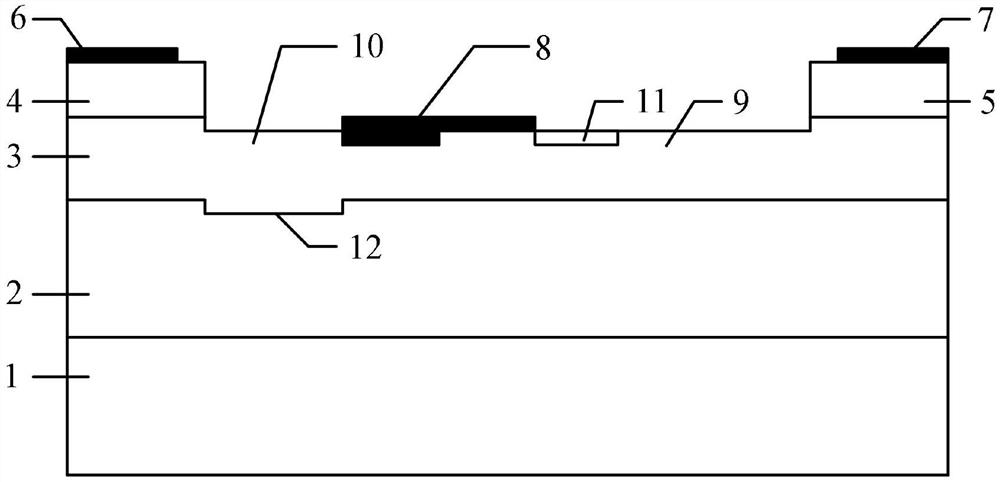

[0021] Such as figure 1 As shown, a 4H-SiC metal-semiconductor field-effect transistor with a P-type doped region and a recessed buffer layer includes, from bottom to top: 4H-SiC semi-insulating substrate 1, P-type buffer layer 2, and N-type channel layer 3 , the doping concentration of the P-type buffer layer 2 is 1.4×10 15 cm -3 , with a thickness of 0.5 μm; the doping concentration of the N-type channel layer 3 is 3×10 17 cm -3 , with a thickness of 0.25 μm; both sides of the N-type channel layer 3 are respectively 0.5 μm long N + type source cap layer 4 and drain cap layer 5, both of which have the same doping concentration and thickness and are respectively 1.0×10 20 cm -3 and 0.2 μm, the surface of the source cap layer 4 and the drain cap layer 5 is respectively the source electrode 6 and the drain electrode 7, and a recessed channel surface is formed between the source electrode 6 and the drain electrode 7, and the N-type channel layer 3 Above and 0.5 μm away from...

Embodiment 2

[0025] A 4H-SiC metal-semiconductor field-effect transistor with a P-type doped region and a recessed buffer layer, including a doping concentration of 1×10 17 cm -3 The length and thickness of the P-type doped region are 0.2 μm and 0.05 μm respectively, and the depth of the recessed buffer layer is 0.03 μm.

[0026] The remaining technical solutions of this embodiment are consistent with Embodiment 1.

Embodiment 3

[0028] A 4H-SiC metal-semiconductor field-effect transistor with a P-type doped region and a recessed buffer layer, including a doping concentration of 4×10 17 cm -3 The length and thickness of the P-type doped region are 0.5 μm and 0.05 μm respectively, and the depth of the recessed buffer layer is 0.08 μm.

[0029] The remaining technical solutions of this embodiment are consistent with Embodiment 1.

[0030] Through simulation experiments, under the same conditions, compared with the double-recessed 4H-SiC metal-semiconductor field-effect transistor in the prior art, the breakdown voltage of the present invention has been improved by 61.57%, and the saturated drain current has also been improved to a certain extent, thus The output power density of the device is greatly improved, and the output power density is increased by about 72.85%.

PUM

| Property | Measurement | Unit |

|---|---|---|

| length | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More