Processor verification method and related device

A verification method, technology of a processor, applied in the field of electronics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

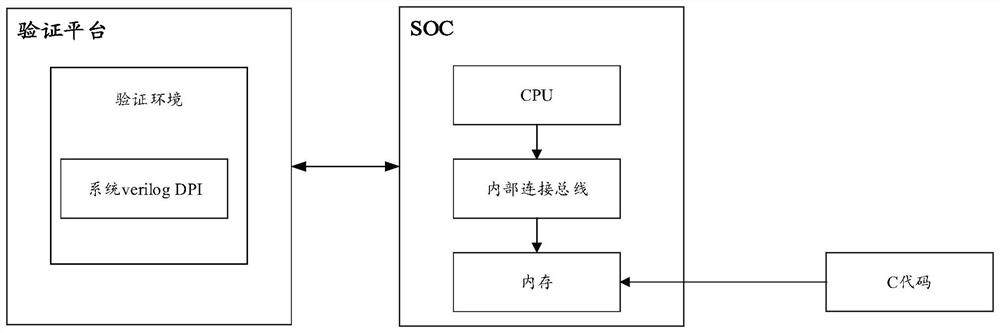

[0037] The technical solutions in the embodiments of the present application will be described below with reference to the accompanying drawings.

[0038] In order to better understand the solutions of the embodiments of the present application, the following first introduces related terms and concepts that may be involved in the embodiments of the present application.

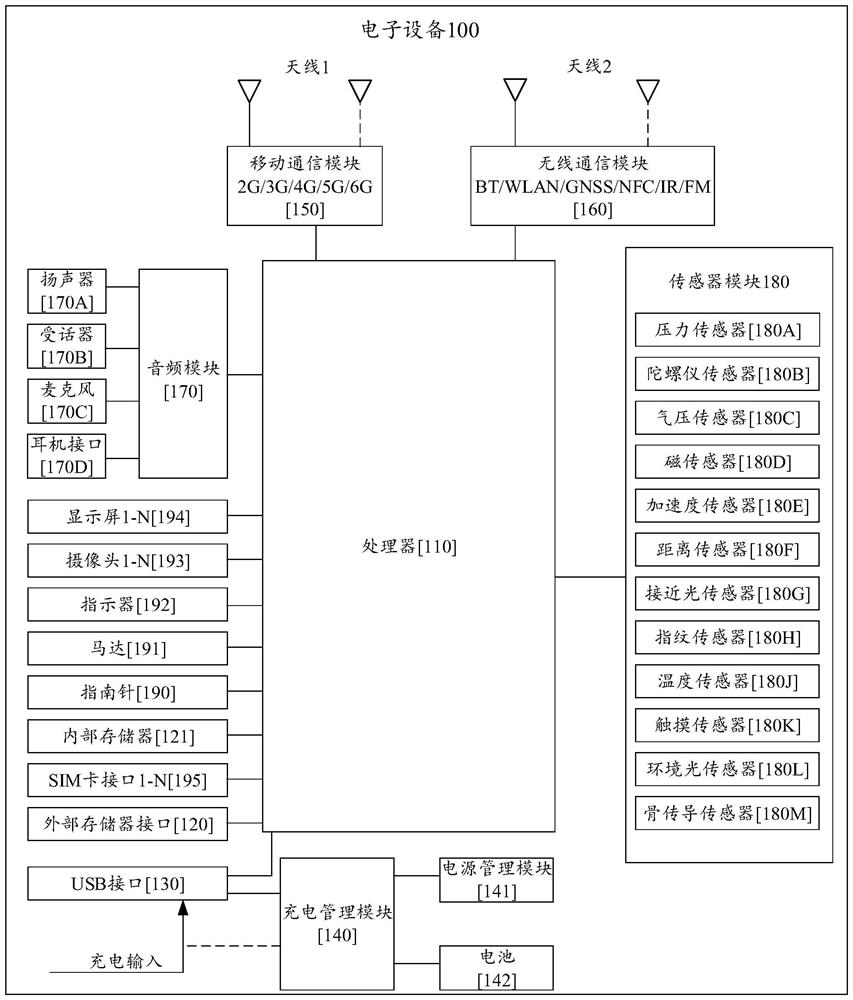

[0039] In a specific implementation, electronic devices may include various devices with processor functions, for example, handheld devices (smart phones, tablet computers, etc.), vehicle-mounted devices (navigators, auxiliary reversing systems, driving recorders, car refrigerators, etc.), Wearable devices (smart bracelets, wireless headphones, smart watches, smart glasses, etc.), computing devices or other processing devices connected to wireless modems, and various forms of user equipment (User Equipment, UE), mobile stations (MobileStation , MS), a virtual reality / augmented reality device, a terminal device...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More