Phase synchronization update without synchronization signal transmission

A phase and signal technology, applied in the field of electronic equipment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

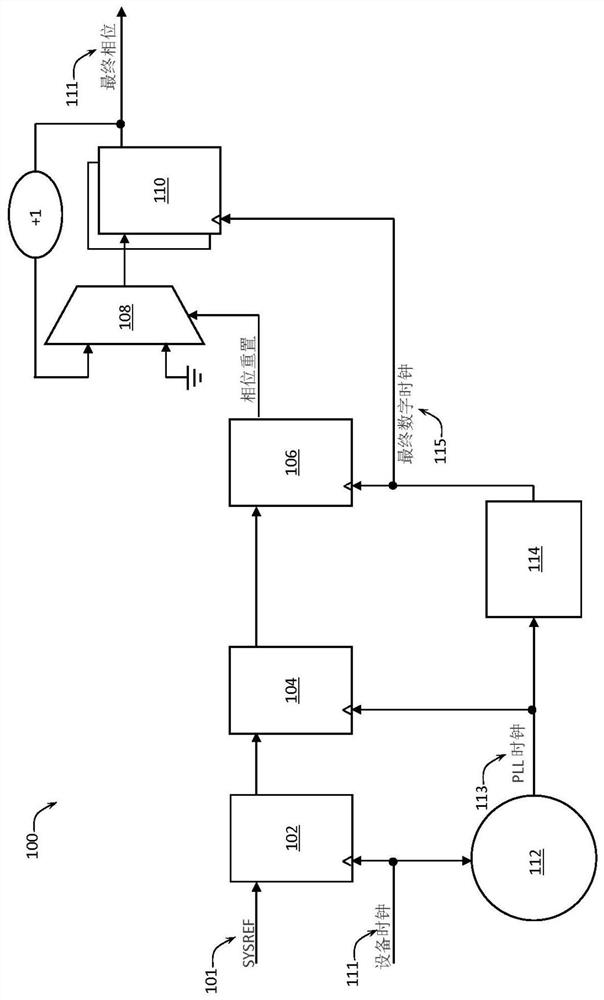

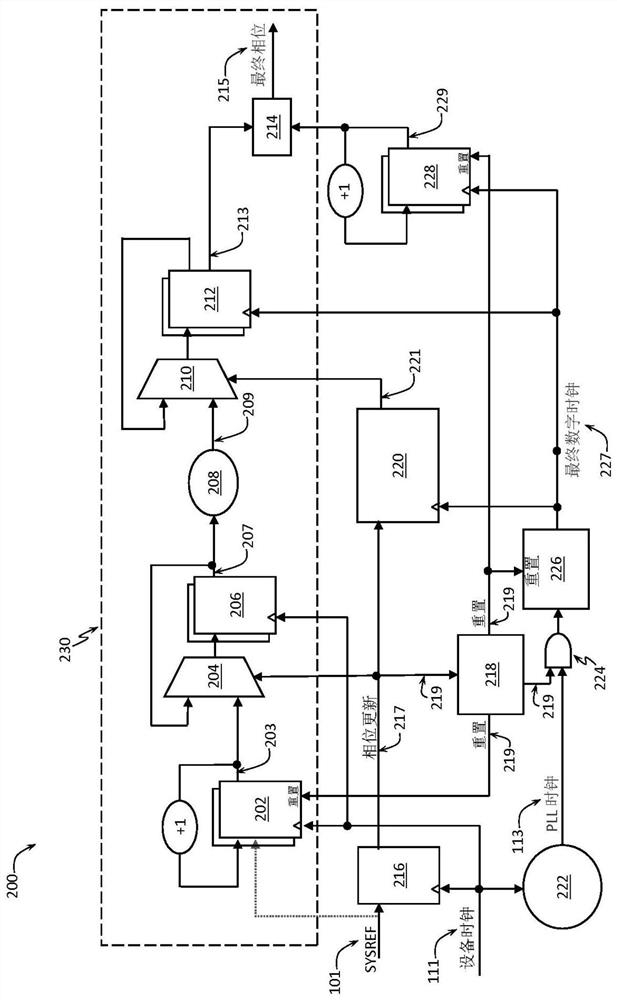

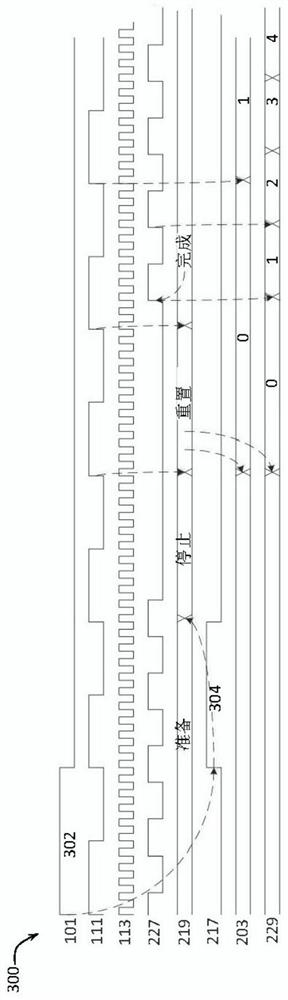

[0018] review

[0019] Embodiments of the present disclosure provide systems and methods for implementing phase synchronous updates based on an incoming SYSREF signal without requiring synchronous distribution of the SYSREF signal. In the context of this disclosure, the SYSREF signal can be distributed to various IC components if it is distributed to various IC components in such a way that substantially maintains a predefined delay between the arrival of pulses in the SYSREF signal and the final digital clock signal generated based on the PLL clock in the high-speed domain Described as a "synchronous" distribution (for example, when the SYSREF signal is clocked by a high-speed clock). Synchronous distribution of the SYSREF signal in the high-speed domain is often difficult due to the strict set-and-hold constraints of very high-speed digital signal transmission. Furthermore, providing phase synchronous updates without synchronous signal transmission can advantageously redu...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap