Code rate compatible multi-element LDPC code bit-level punching method

A technology compatible with LDPC codes and bit rates, applied in the field of electronic communication, can solve the problems of high error probability of information recovery and high bit error rate of punching nodes, and achieve increased complexity, low bit error rate, and low probability of information recovery errors Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

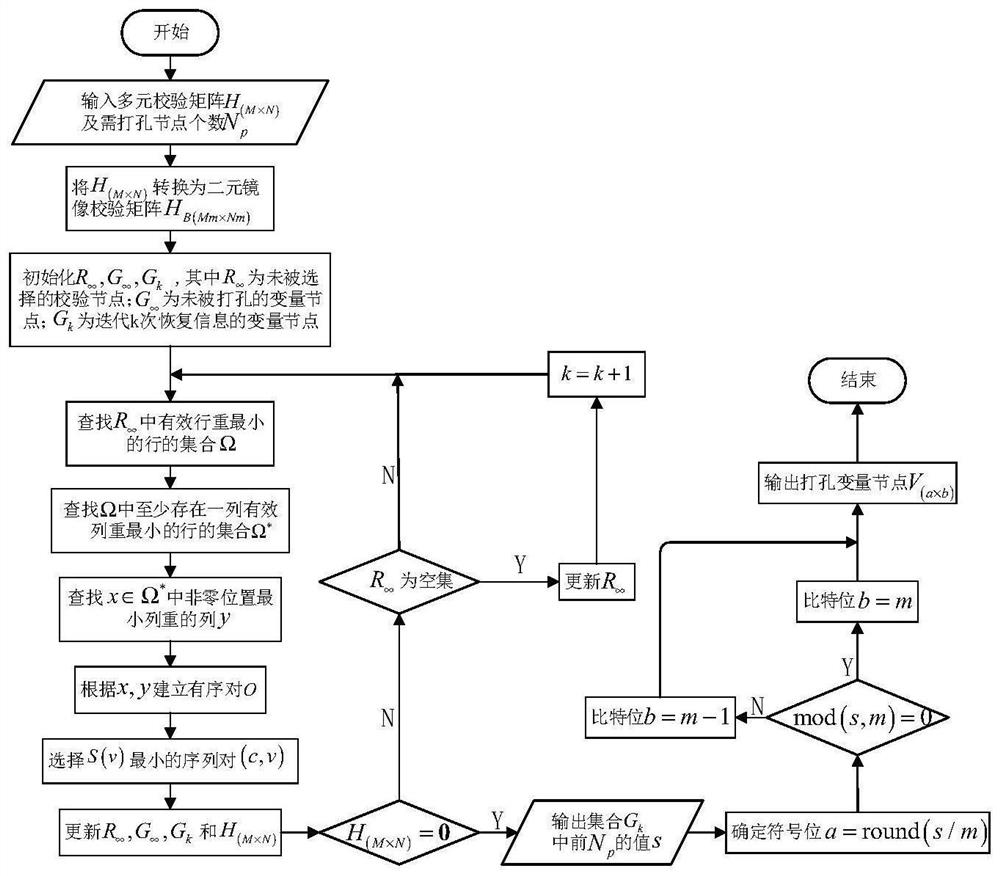

[0042] The present invention provides a technical solution: a bit-level punching method of multiple LDPC codes with compatible code rates, comprising the following steps:

[0043] Obtain the number of iterations, and group the variable nodes of the binary mirror matrix according to the number of iterations;

[0044] Extract the bit and sign bit of the grouping variable node, and output the position of the punching variable node.

[0045] It is not difficult to find through the above steps that the bit-level punching algorithm of the present invention includes two parts, that is, firstly group the variable nodes of the binary mirror matrix according to the number of iterations, and secondly determine the bits of the grouping variable nodes so as to output the punching variable nodes. position, so that in the case of only one pair of codecs, any change from low code rate to high code rate can be realized, and at the same time, the complexity of the system will not be increased w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More