Discrete device testing method

A technology of discrete devices and testing methods, applied in semiconductor/solid-state device testing/measurement, electrical components, circuits, etc., can solve problems such as affecting chip quality and unstable test results of 300mm wafer products, achieving convenient testing and improving testing. The effect of precision and chip quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

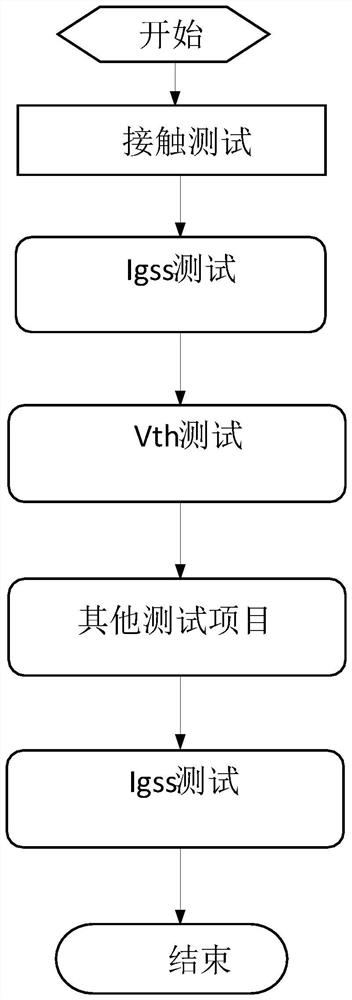

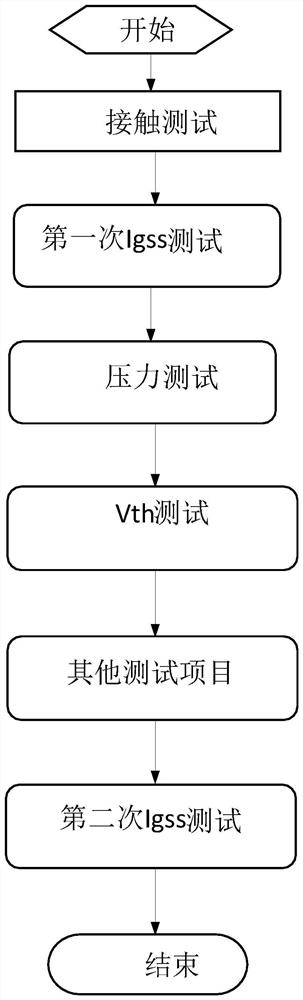

[0035] like figure 2 As shown, the discrete device testing method of the present invention comprises the following steps:

[0036] Step 1, contact test; the contact test mainly confirms whether the probe is in good contact with the pad (pin pad) of the discrete device. The contact test generally adopts the method of applying current to measure the voltage, and the test time is generally between several milliseconds to several hundred milliseconds. Testers are purchased on demand.

[0037] Step 2, the first gate-source leakage (lgss) test; apply a voltage to the gate of the discrete device according to the specifications, the drain and source are short-circuited, and the leakage current between the gate and the source is tested. Between tens of volts, the test time is generally tens of milliseconds.

[0038] Step 3, stress test; the stress test mainly applies voltage or current to the gate, drain, and source of the discrete device within a certain period of time. The applie...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More