Chip system integration method and device and computer readable storage medium

A chip system and integration method technology, applied in CAD circuit design and other directions, can solve problems such as low integration efficiency, achieve accurate and reasonable classification, storage, and avoid low processing efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

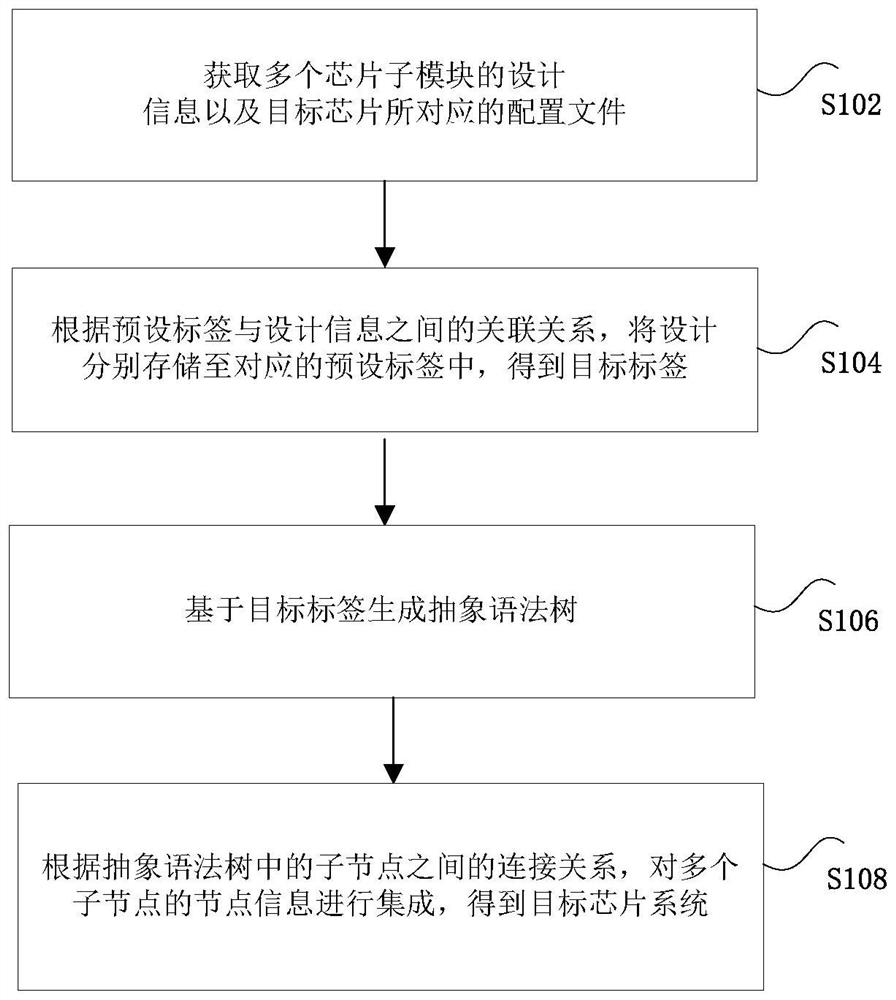

[0030]According to an embodiment of the present invention, a method embodiment of a method for integrating a chip system is provided. It should be noted that the steps shown in the flowchart of the accompanying drawings may be executed in a computer system such as a set of computer-executable instructions, Also, although a logical order is shown in the flowcharts, in some cases the steps shown or described may be performed in an order different from that herein.

[0031] In addition, it should also be noted that an electronic device can be used as the execution body of the method for integrating the chip system in the embodiment of the present invention.

[0032] figure 1 is a flowchart of an optional chip system integration method according to an embodiment of the present invention, such as figure 1 As shown, the method includes the following steps:

[0033] Step S102 , acquiring design information of a plurality of chip sub-modules and configuration files corresponding to ...

Embodiment 2

[0091] According to another aspect of the embodiments of the present invention, an integrated device of a chip system is also provided, wherein, Figure 7 It is a schematic diagram of an integrated device of a chip system according to an embodiment of the present invention. like Figure 7 As shown, the apparatus includes: an acquisition module 701 , a storage module 702 , a generation module 703 and an integration module 704 .

[0092] The acquisition module 701 is used for acquiring design information of multiple chip sub-modules and configuration files corresponding to the target chip, wherein the configuration files at least include preset tags for storing design information, and the multiple chip sub-modules are used for Integrate the target chip; the storage module 702 is used to store the design information in the corresponding preset labels according to the association relationship between the preset labels and the design information, so as to obtain a plurality of tar...

Embodiment 3

[0101] Optionally, according to another aspect of the embodiments of the present invention, there is also provided a computer-readable storage medium, where a computer program is stored in the computer-readable storage medium, wherein the computer program is configured to execute the above embodiments when running 1. The integration method of the system-on-a-chip.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More