Electrostatic discharge protective circuit having high trigger current

An electrostatic discharge protection and trigger current technology, applied in circuits, electrical components, electrical solid devices, etc., can solve the problems of unacceptable or sending signals, small trigger current, latching, etc., to avoid latching effect, good ESD The effect of protective ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

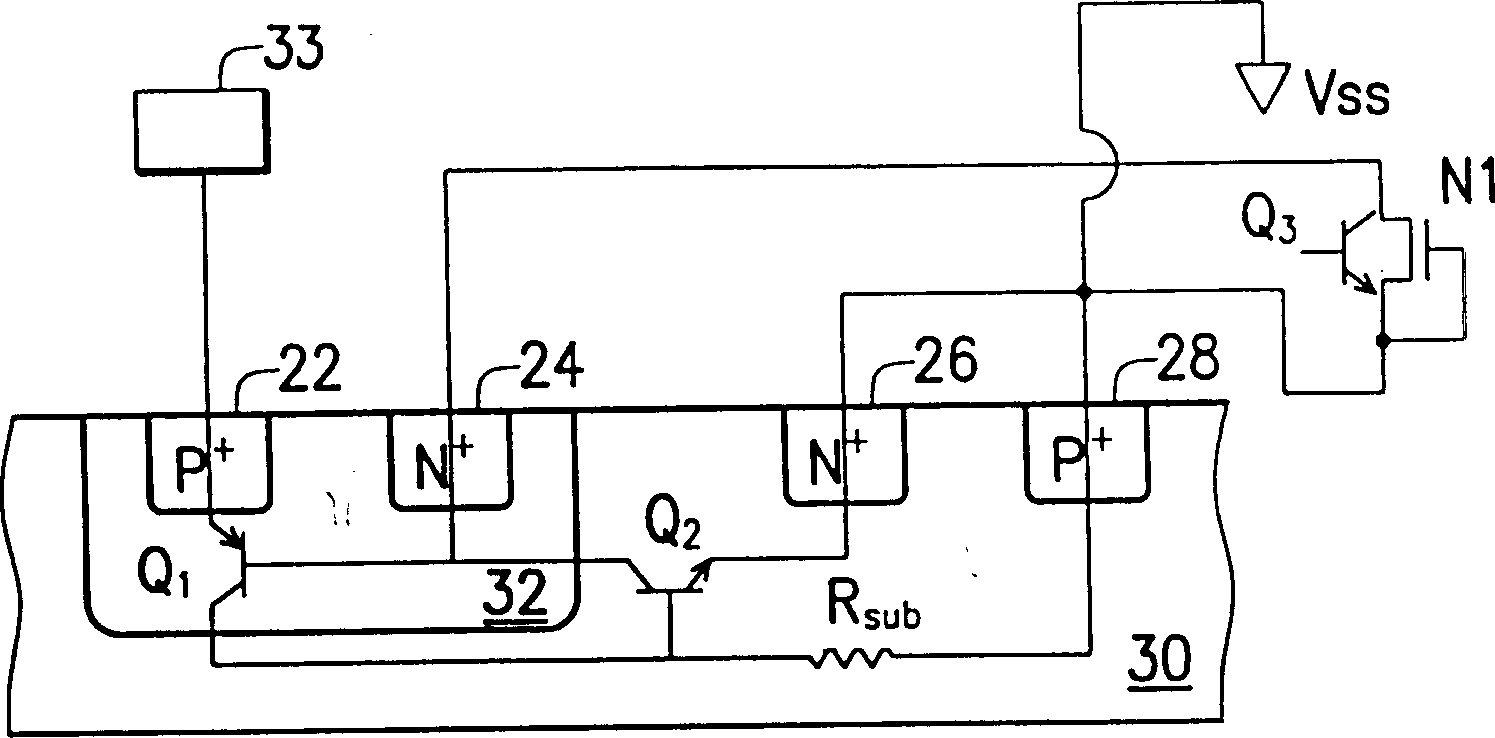

[0024] In order to make the above-mentioned purposes, features and advantages of the present invention more obvious and understandable, a preferred embodiment is specifically cited below, together with the attached Figure 3-9 , as detailed below:

[0025] image 3 It is a schematic cross-sectional view of the ESD protection circuit of the present invention. Figure 4 for image 3 A layout diagram of the SCR shown.

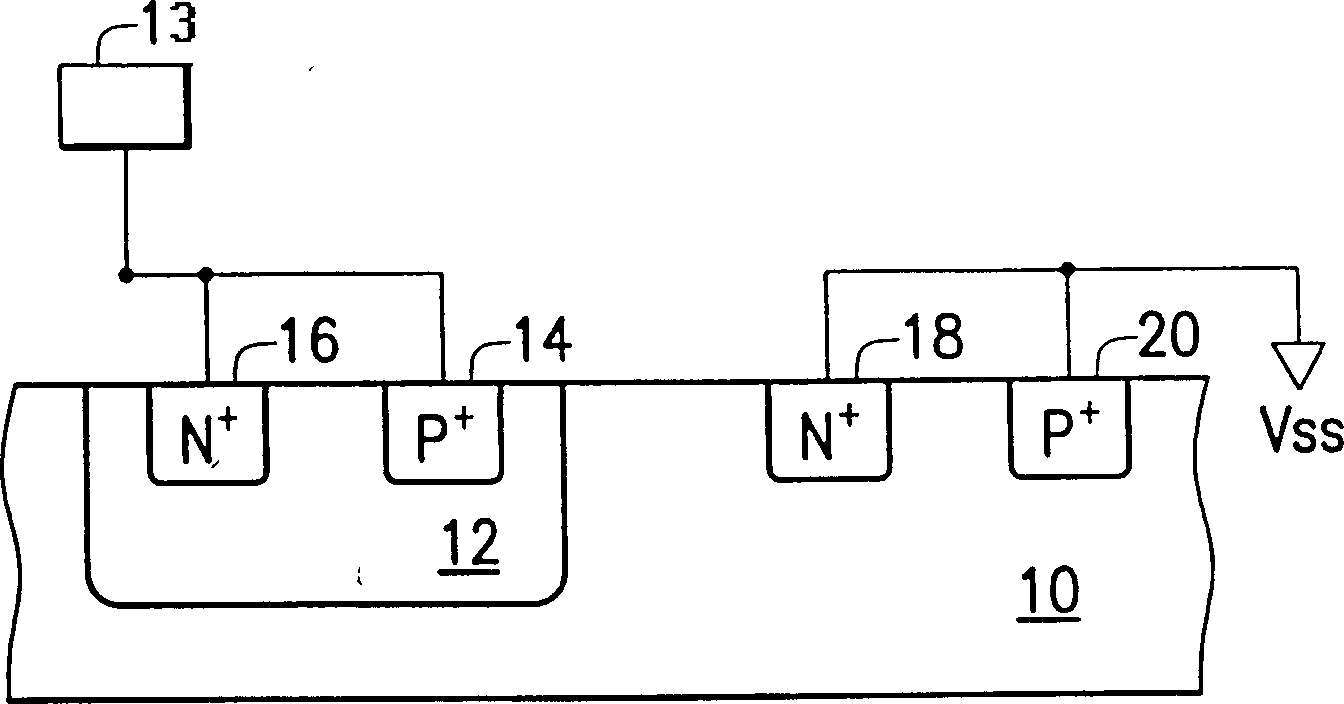

[0026] image 3 Among them, the ESD protection circuit of the present invention mainly includes two components, one is a lateral SCR, and the other is an NMOS N1. Such as image 3 , Figure 4 As shown, the P+ doped region 22, the N-type well 32, the P-type substrate 30 and the N+ doped region 26 constitute the PNPN structure of the lateral SCR, which are respectively used as the anode, the positive gate, the negative gate and the lateral SCR of the lateral SCR. cathode. The P+ doped region 22 is directly coupled to a bonding pad 33 . The P-type substrate ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More