Producing method for thin-film transistor array baseplate

A technology of thin-film transistors and array substrates, which is applied in the field of manufacturing thin-film transistor array substrates, can solve the problems of reduced yield and production capacity, and achieve the effect of reducing production costs and the number of photomasks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

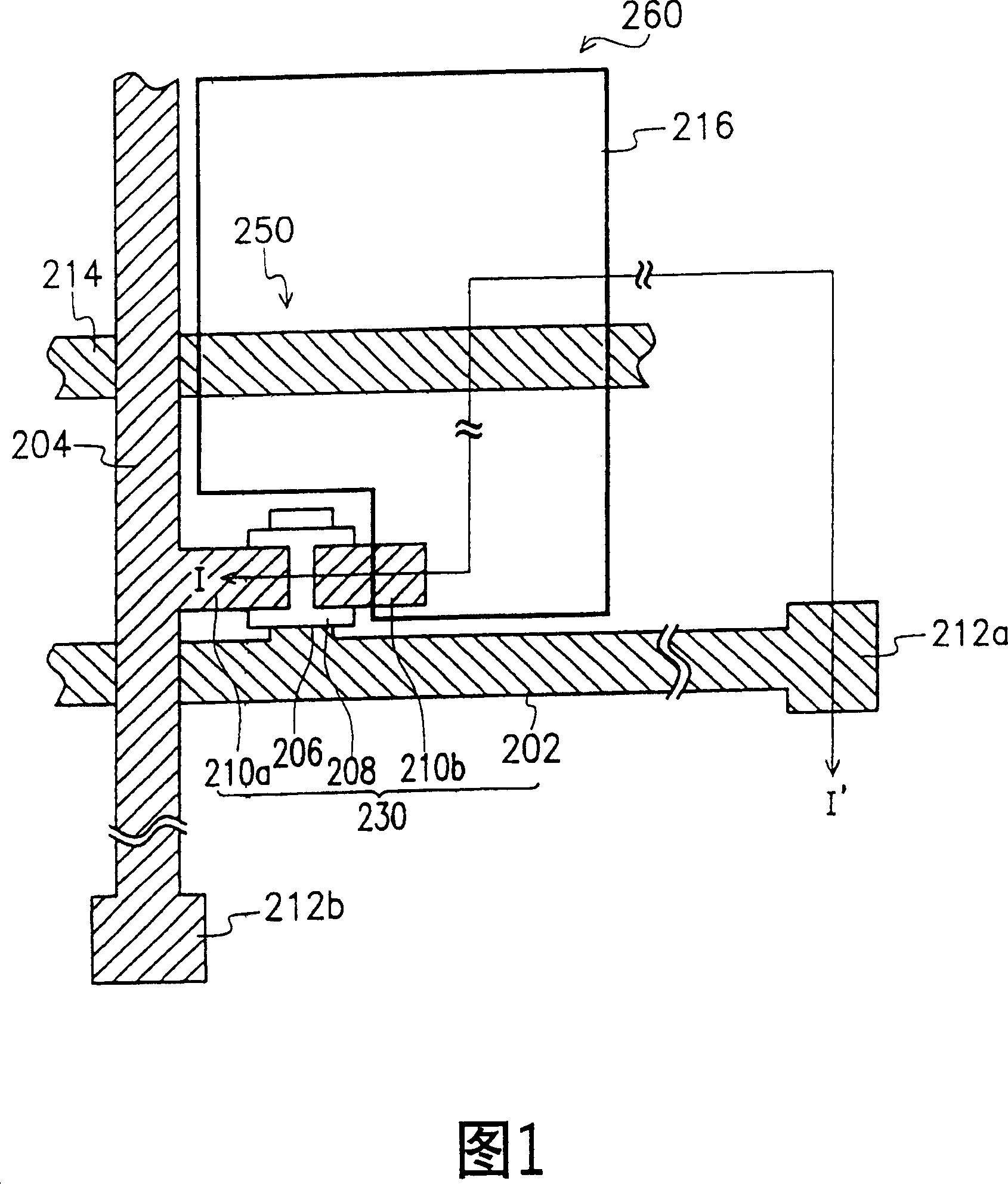

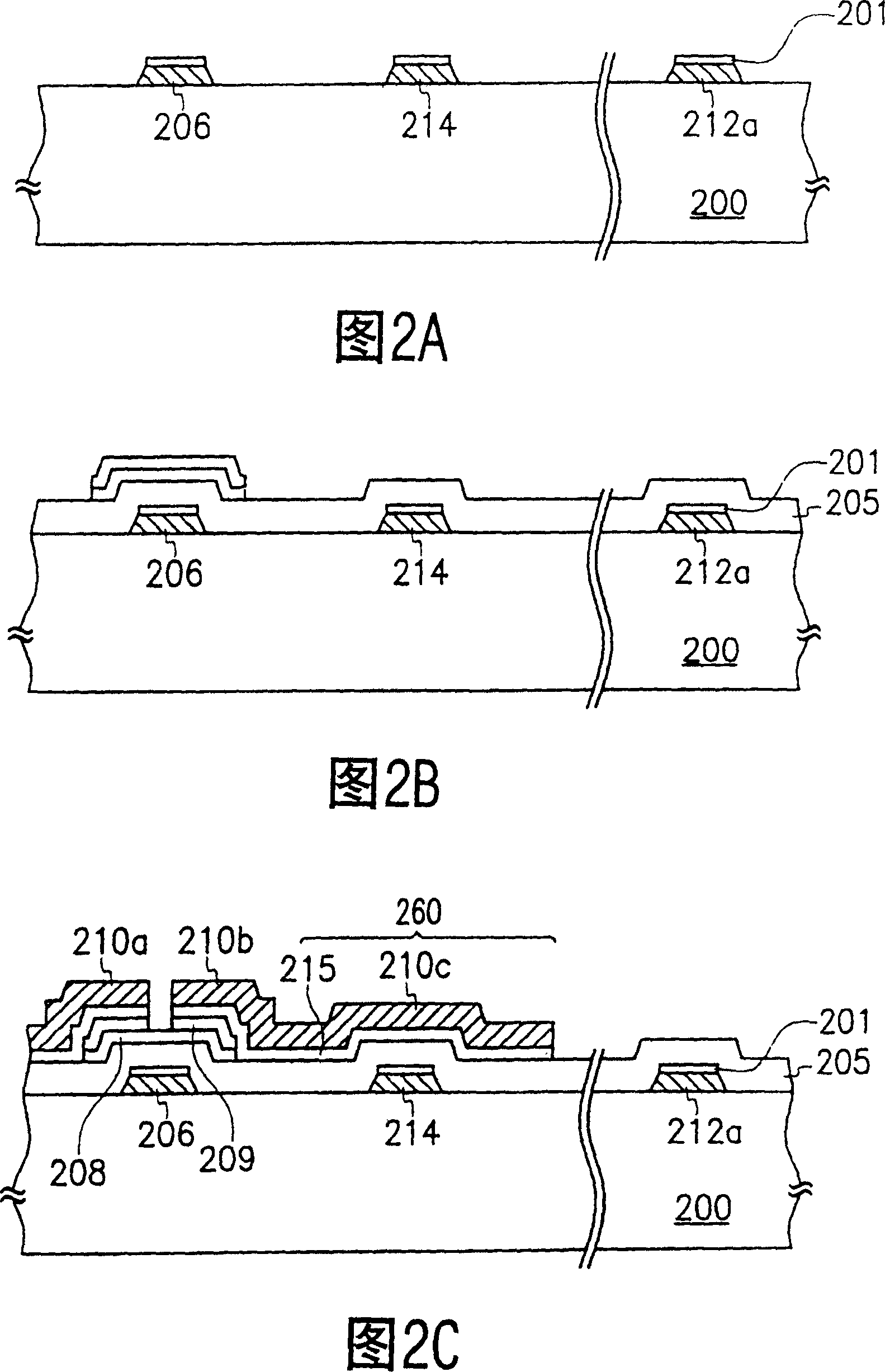

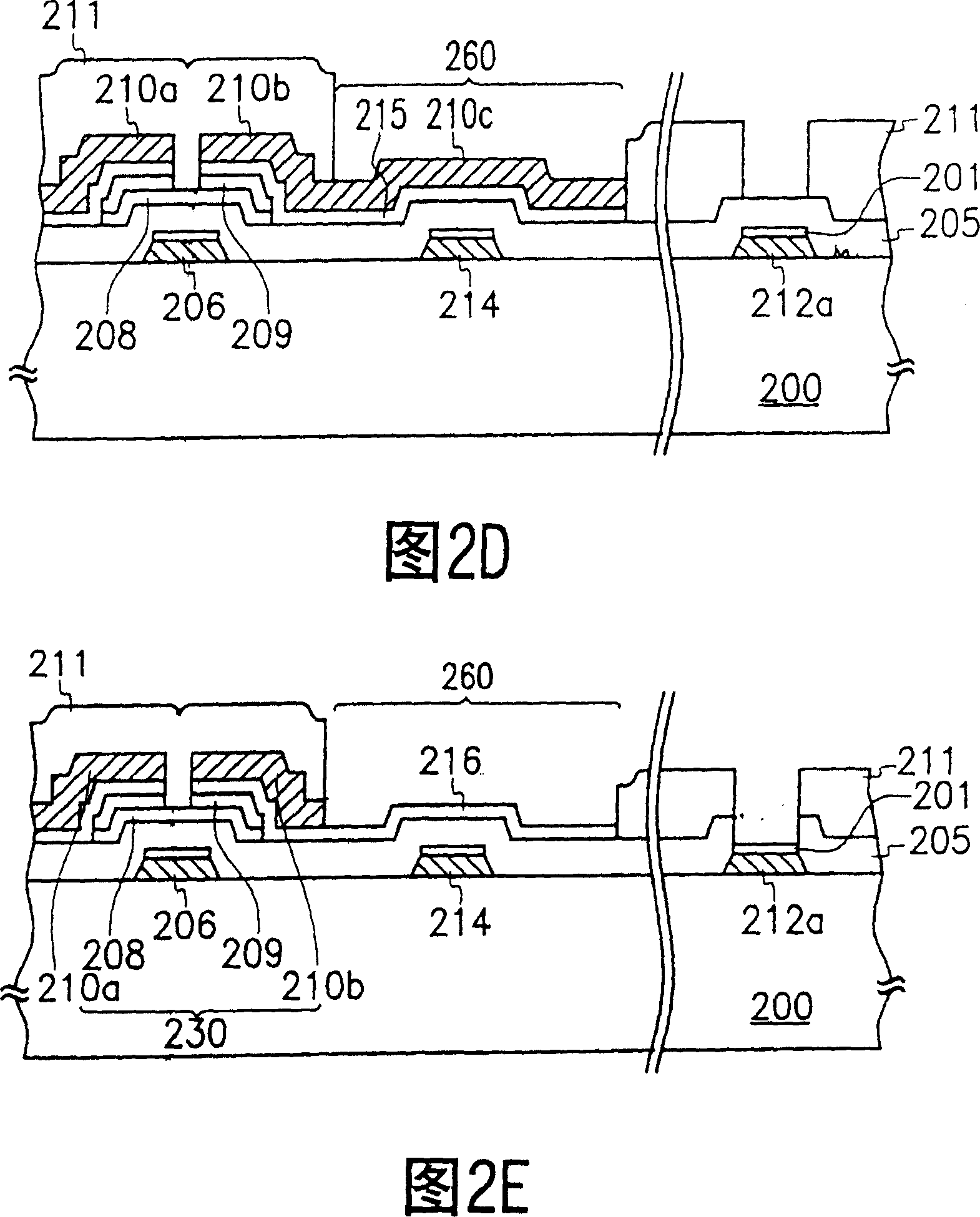

[0046] As shown in FIG. 1, it is a schematic top view of a thin film transistor array substrate according to a preferred embodiment of the present invention; as shown in FIGS. 2A to 2E, it is a thin film transistor array according to a preferred embodiment of the present invention. The schematic cross-sectional view of the manufacturing process of the substrate is a schematic cross-sectional view from I-I in FIG. 1 .

[0047] Please refer to FIG. 1 and FIG. 2A at the same time. Firstly, a substrate 200 is provided, wherein the substrate 200 is, for example, a glass substrate or a plastic substrate. Afterwards, a first metal layer (M1) (not shown) is formed on the substrate 200, and a first photomask manufacturing process is performed to define the gate 206 and the scanning wiring electrically connected to the gate 206 202 , a common line 214 parallel to the scanning wiring 202 and a first terminal portion 212 a formed at an edge of the substrate 200 . Wherein, the first termi...

no. 2 example

[0058] 3A to FIG. 3N are schematic cross-sectional views of a manufacturing process of a thin film transistor array substrate according to another preferred embodiment of the present invention, which are schematic cross-sectional views taken from I-I' in FIG. 1 .

[0059] Please refer to FIG. 1 and FIG. 3A at the same time. First, a first metal layer (M1) (not shown) is formed on the substrate 200, and the first photomask manufacturing process is performed to define the gate 206 and the gate 206. The scanning wiring 202 electrically connected, the common line 214 parallel to the scanning wiring 202 and the first terminal portion 212 a formed at two edges of the substrate 200 . Wherein, the first terminal portion 212a is electrically connected to the scanning wiring 202, and is subsequently used to electrically connect to the driving circuit, and the common line 214 is subsequently used as the lower electrode of the pixel storage capacitor 250. In a preferred implementation In ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More