Memory controller which increases bus utilization by reordering memory requests

A memory controller and reordering technology, applied in the field of computing systems, can solve problems such as slowing down the access speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

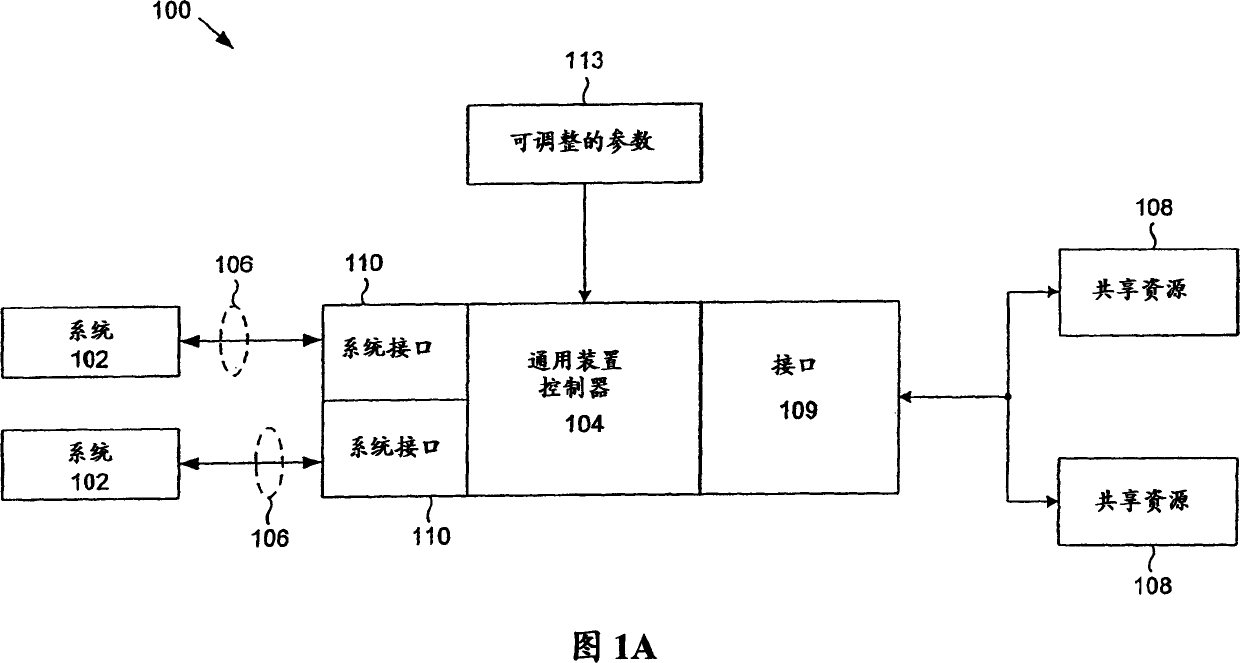

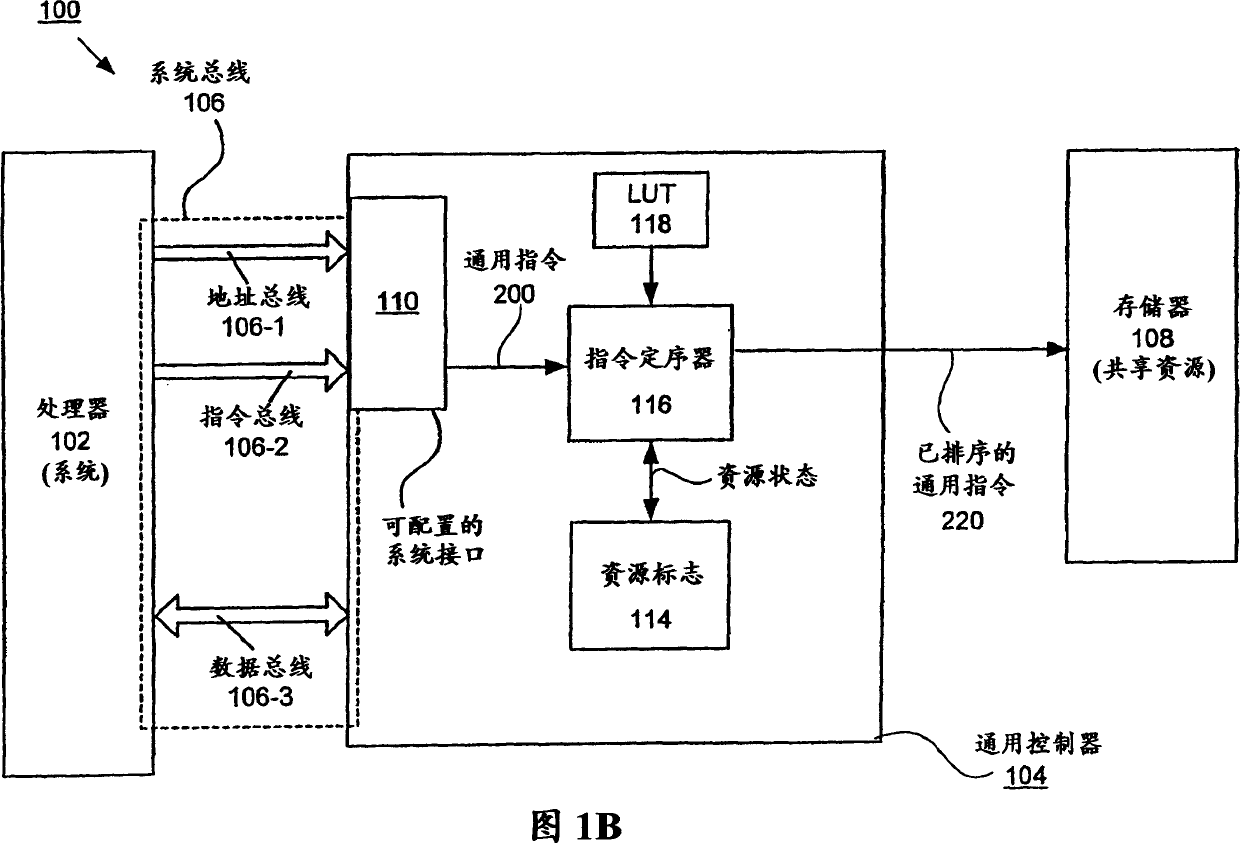

[0045] DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0046] In systems with several devices, such as processors, sharing common resources, various methods have been used to avoid conflicts when more than one device requests access to shared resources. One approach is to resolve conflicts by sequentially operating the processor and by using a time-sharing processor. At this point, in order to avoid conflicts, the processor simply accesses the shared resources "in turn". Such systems that are commonly used include "passing bells" or "marking systems," in which the potentially conflicting processors are simply polled by the system in the same order as the pass bells for a group of users.

[0047] Unfortunately, the use of sequential processor access methods typically imposes significant limitations on the overall computer system due to the actual amount of time spent polling the competing processor.

[0048] Another traditional approach to avoiding conflict is to rely on the establish...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More