Method for making shallow channel isolation

A manufacturing method and technology of shallow trenches, which can be used in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., and can solve the problems of semiconductor component operation, silicon oxide plug depression, affecting the electrical characteristics of semiconductor components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

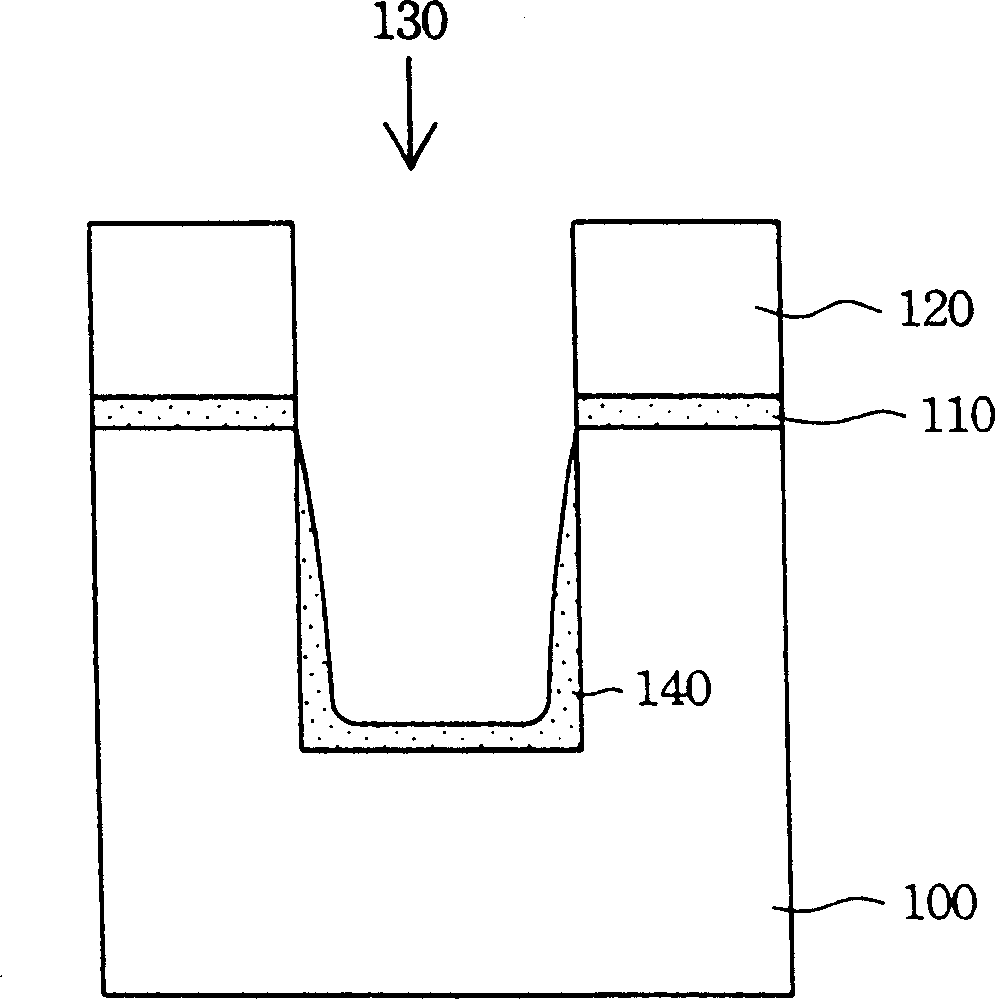

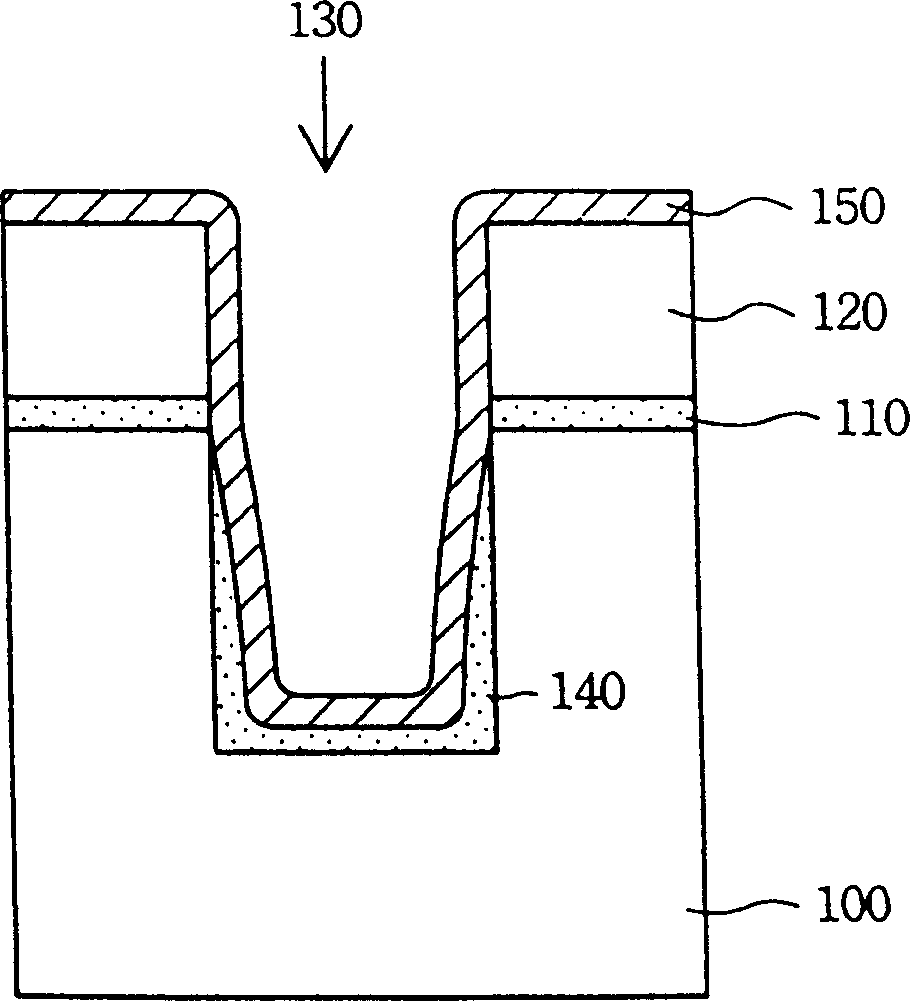

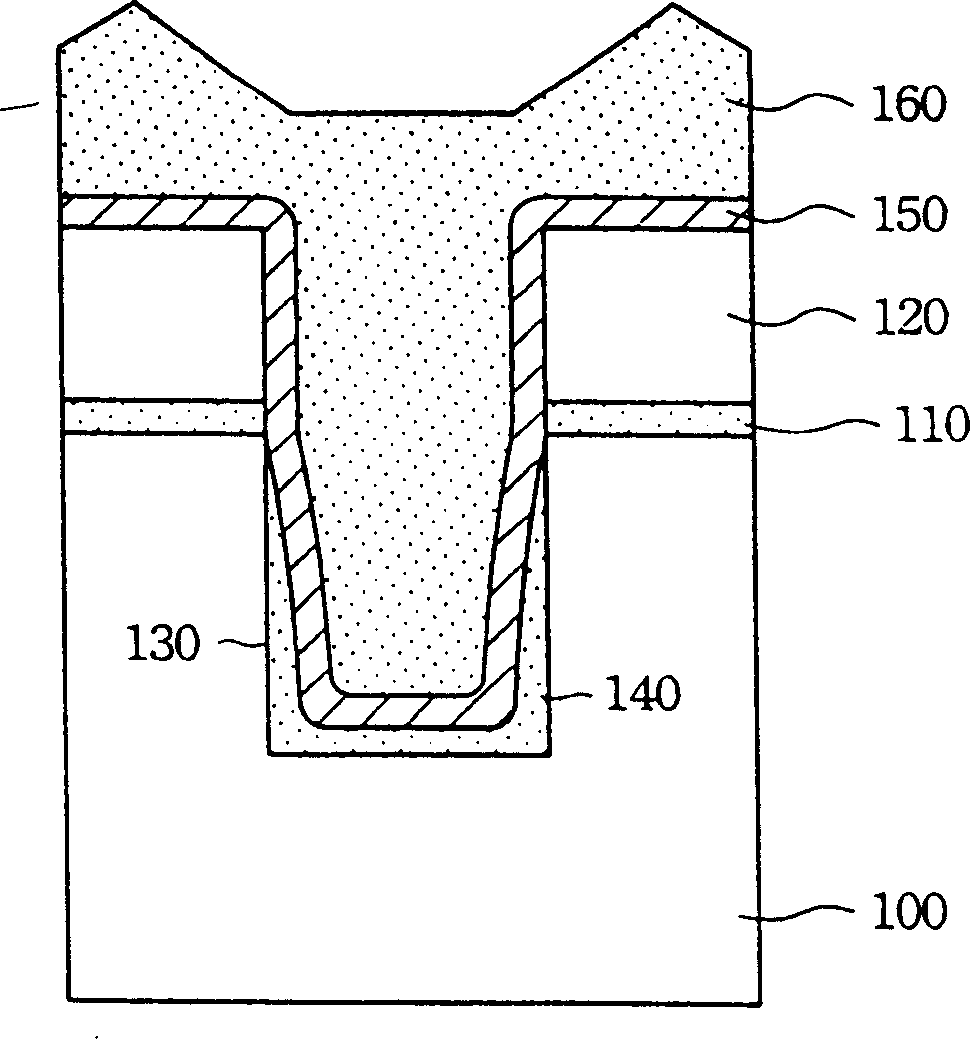

[0032] see Figure 1-5 , which shows a cross-sectional view of a manufacturing process of shallow trench isolation according to a preferred embodiment of the present invention.

[0033] figure 1 In this method, a pad oxide layer 110 and a silicon nitride layer 120 are sequentially formed on the substrate 100 first, and then a lithographic etching process is performed to pattern the silicon nitride layer 120 and the pad oxide layer 110 to expose part of the surface of the substrate 100 . Next, using the silicon nitride layer 120 as a mask, the exposed substrate 100 is etched to form a trench 130 in the substrate 100 .

[0034] A thermal oxidation method is then performed to form a liner oxide layer 140 on the surface of the trench 130 to repair the structural damage caused on the surface of the trench 130 during the etching process. Please note that the thickness of the liner oxide layer 140 formed on the top edge of the trench 130 is relatively thin, because of its geometry,...

PUM

| Property | Measurement | Unit |

|---|---|---|

| refractive index | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More