Decimal frequency-dividing synthesizer with sinusoidal generator

A technology of fractional frequency division and frequency synthesizer, which is applied in the direction of automatic power control and electrical components, and can solve problems such as interval error and timing error

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] best practice

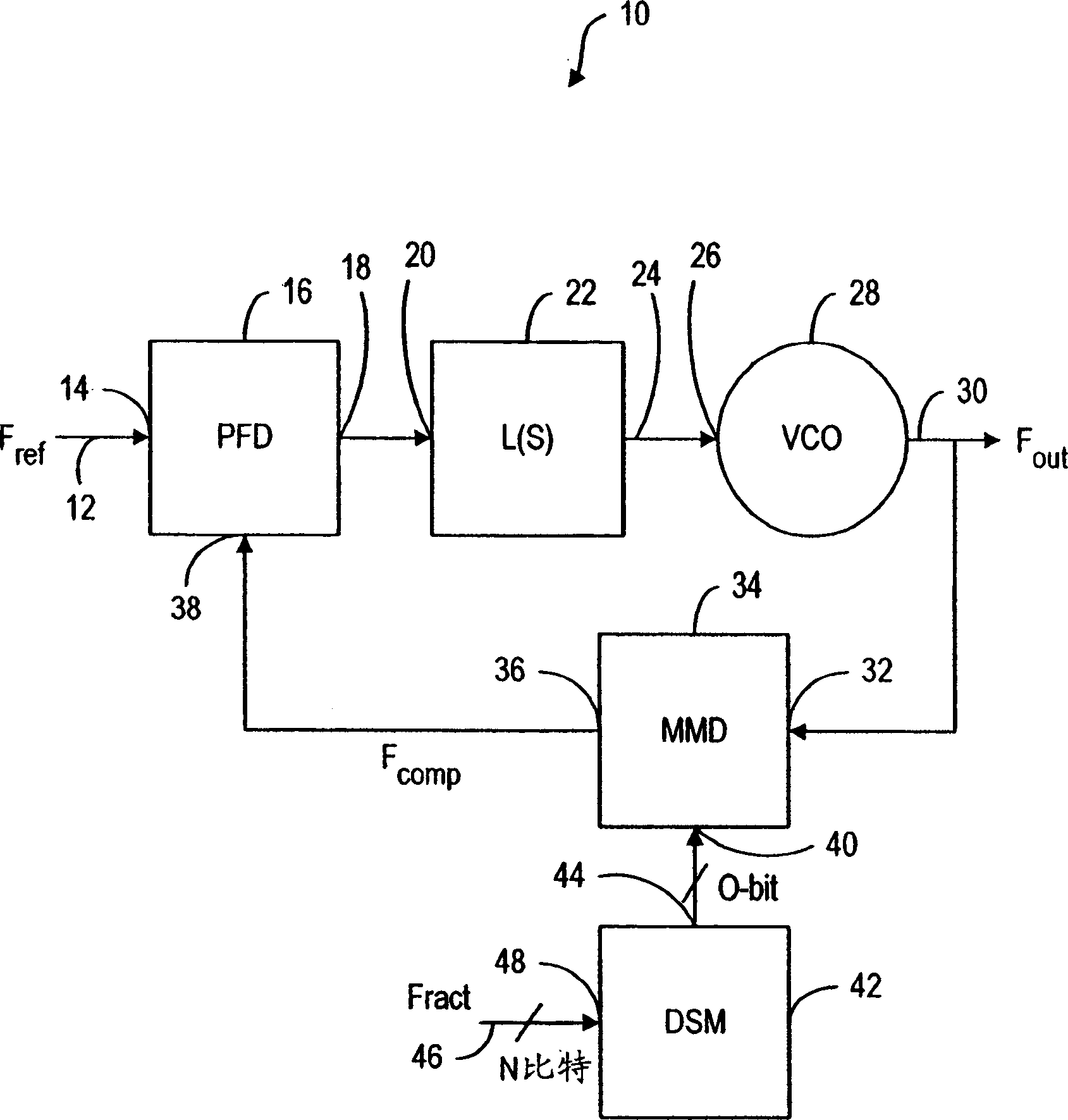

[0034] See now the attached drawings and consider first figure 1, a schematic functional block diagram of a typical delta-sigma modulator based on a fractional phase-locked loop frequency synthesizer is illustrated there and generally designated as 10. The fractional delta-sigma frequency synthesizer 10 includes a phase frequency detector (PFD) 16 , a loop filter 22 , and a voltage controlled oscillator (VCO) 28 . A reference frequency to frequency synthesizer 10 at input 12 is used at input 14 of PFD 16 . Multimode frequency divider 34 is located between VCO output 30 and input 38 of PFD 16 . Output 18 of PFD 16 is coupled to input 20 of loop filter 22 . Loop filter 22 functionally operates as an integrating capacitor. An output 24 of loop filter 22 is coupled to a VCO input 26 . VCO 28 produces a frequency signal at VCO output 30 in response to a signal at its input 26 . The frequency Fout at the VCO output 30 is coupled to the input 32 of a mult...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More