High speed data link control protocol receiving processing module and data processing/method

A link control protocol and high-speed data technology, applied to electrical components, transmission systems, etc., can solve problems such as large chip area and ineffective increase in port speed, and achieve the effect of improving processing capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

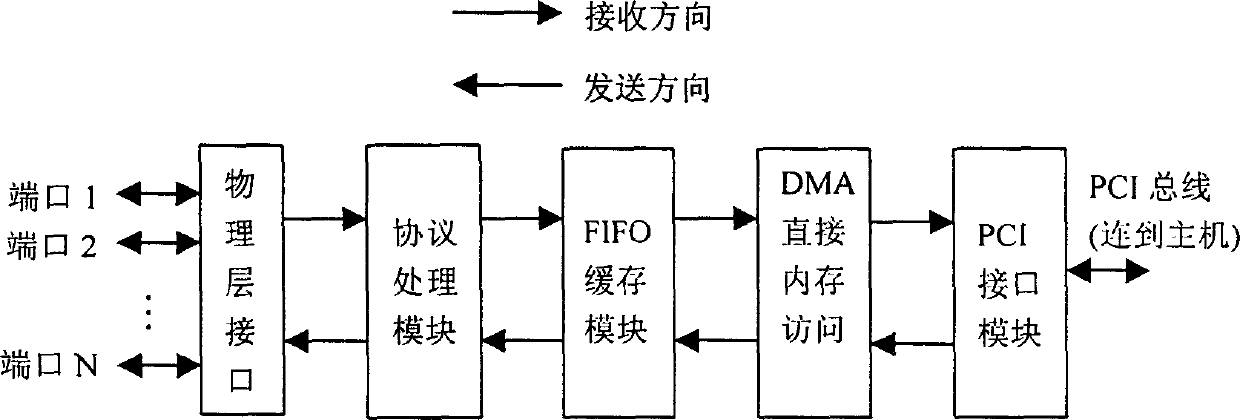

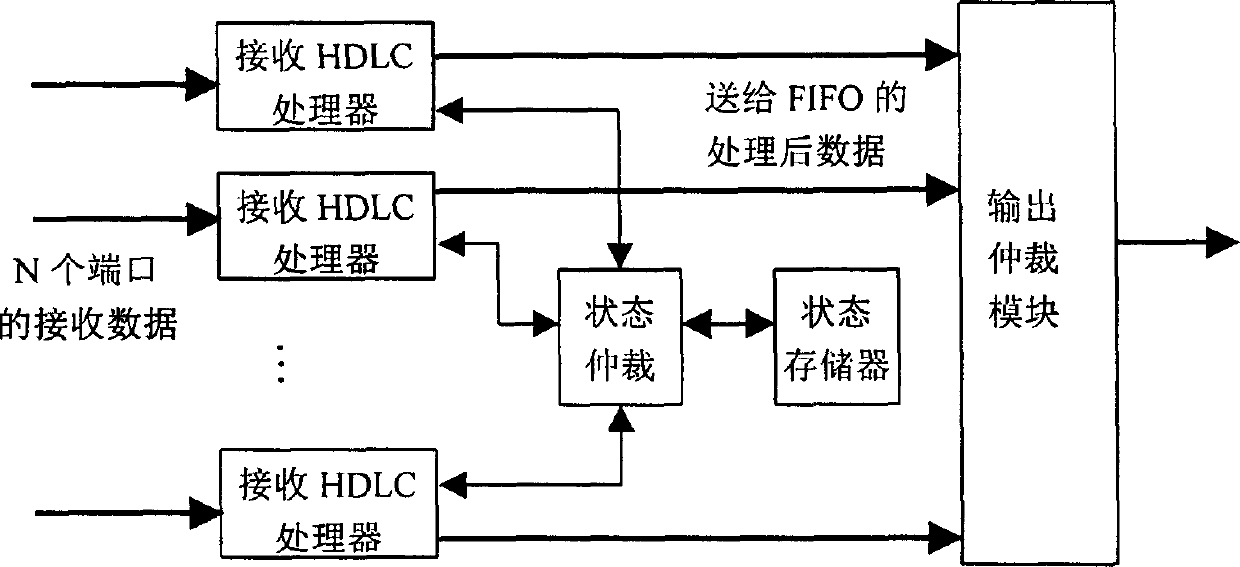

[0038] A kind of HDLC protocol receiving processing module and data processing method thereof for controlling the serial port communication controller chip of N (taking N=16 as embodiment) ports that the present invention proposes, in conjunction with accompanying drawing, describe in detail as follows:

[0039] The HDLC protocol receiving processing module structure of the present embodiment is as shown in Figure 5, and it is made up of a port arbitration module, a receiving HDLC protocol processor and a state memory module; Wherein, the input end of the port arbitration module is connected with 16 ports simultaneously Connection, the input end of the receiving HDLC protocol processor is connected to the output end of the port arbitration module, and is connected to the state memory module bidirectionally at the same time, the output end of the receiving HDLC protocol processor is connected to the input end of the first-in-first-out buffer (FIFO) of the subsequent circuit .

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More