Imbedded grating semiconductor devices

A technology of semiconductors and buried gates, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, transistors, etc., and can solve the problems of not being able to obtain conventional shutdown characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

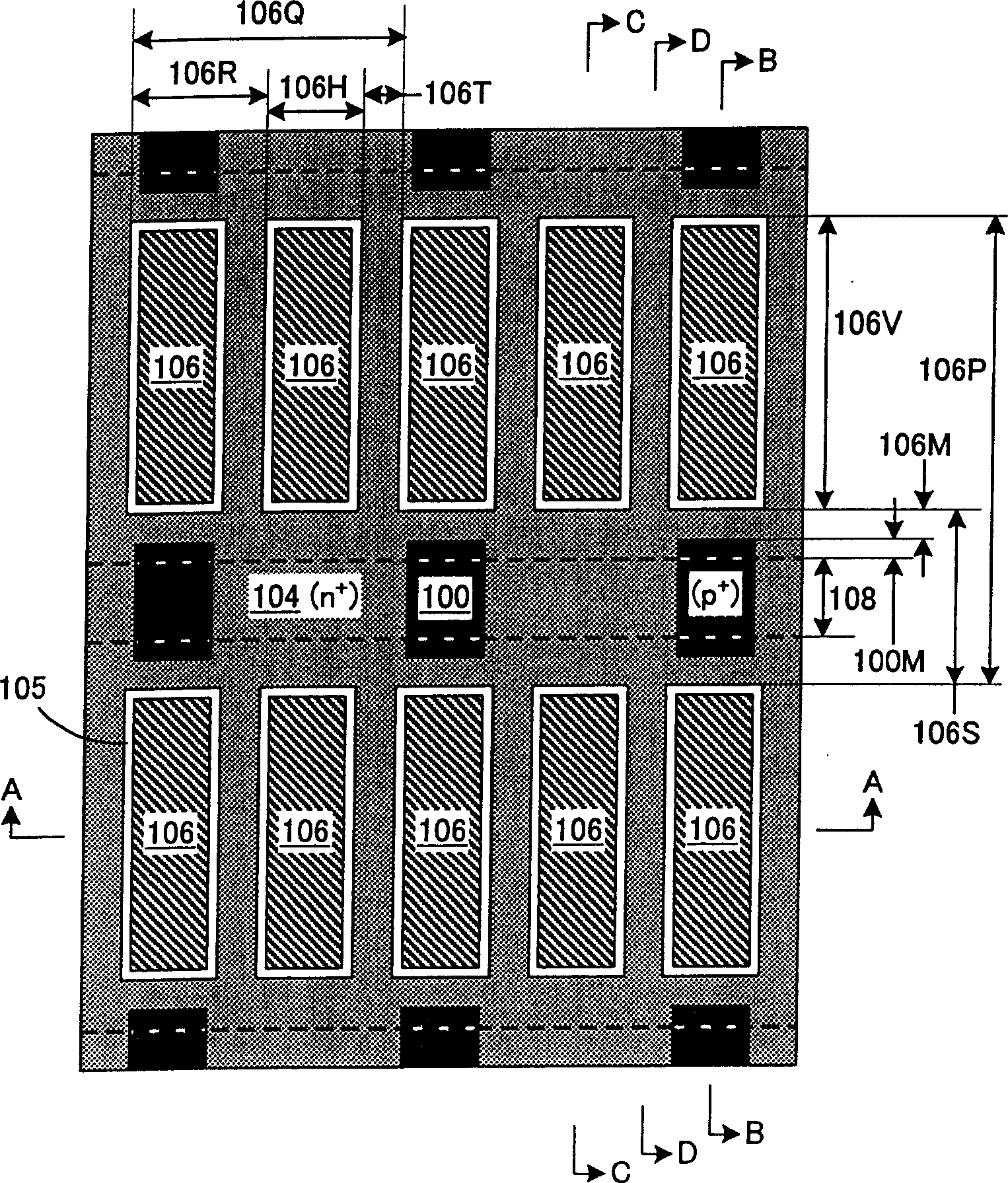

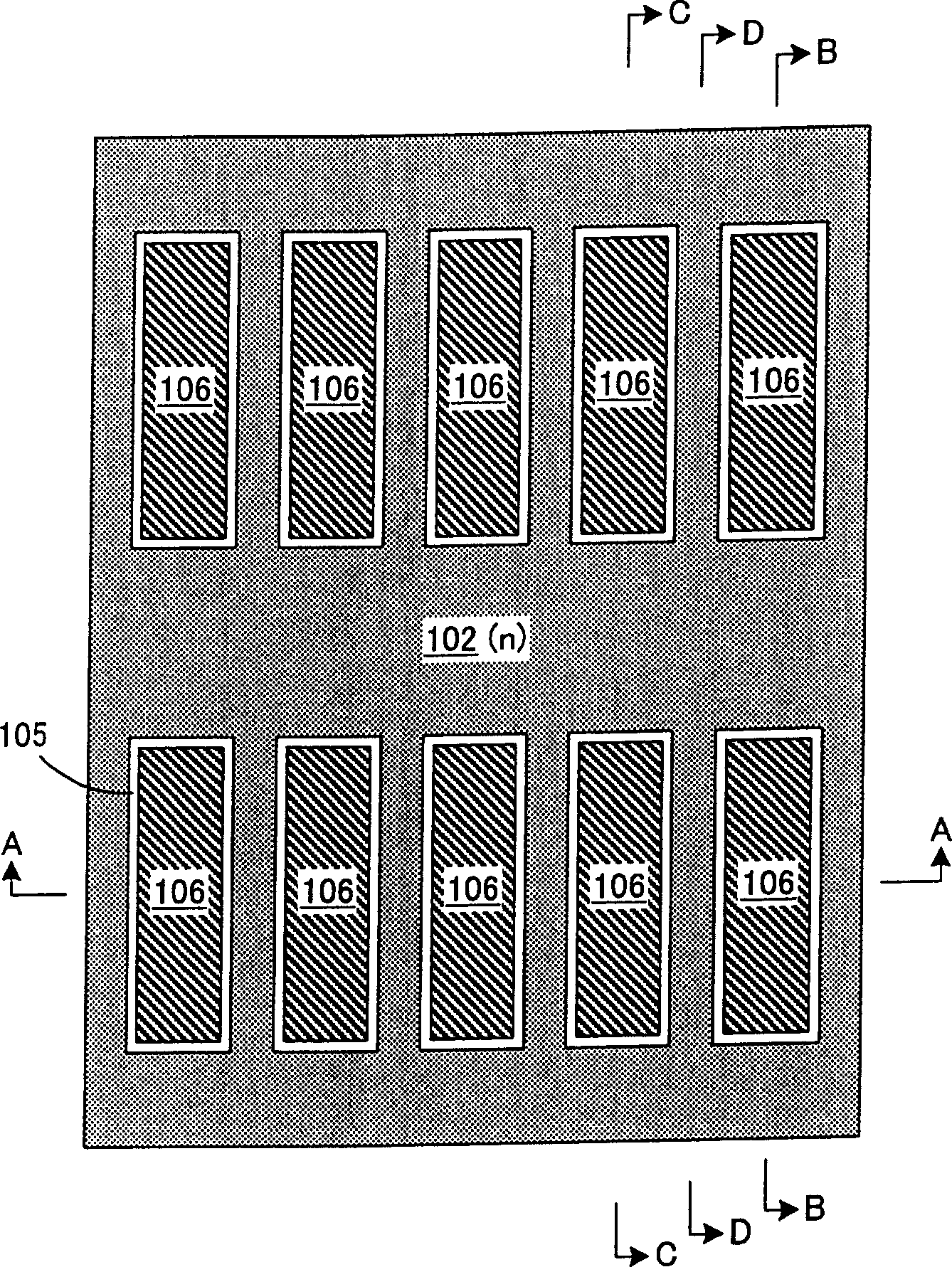

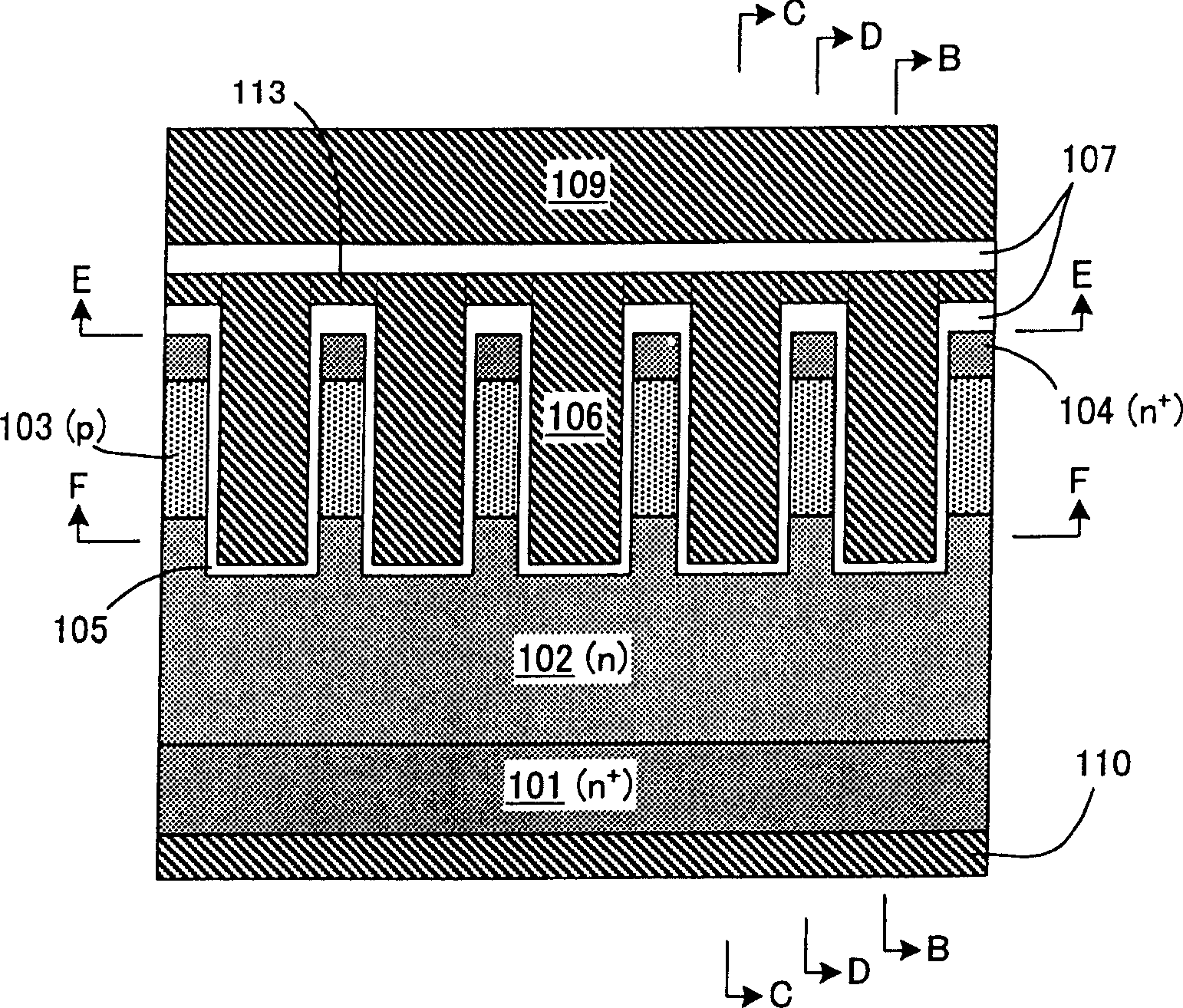

[0076] The first embodiment is a field effect type semiconductor device according to an embodiment of the present invention, having a trench type insulating gate thereon. Figure 1 to Figure 6 The structure of the field effect type semiconductor device according to the first embodiment is shown. image 3 yes figure 1 and figure 2 Sectional view of part A-A in. Figure 4 yes figure 1 and figure 2 Sectional view of part B-B in . Figure 5 yes figure 1 and figure 2 Sectional view of part C-C in . Figure 6 yes figure 1 and figure 2 Sectional view of part D-D in . figure 1 yes Figure 3 to Figure 6 A cross-sectional view of part E-E in (this plane is referred to as the "surface" of the semiconductor substrate in the specification). figure 2 yes Figure 3 to Figure 6 Cross-sectional view of part F-F in Fig.

[0077] The present field effect type semiconductor device is constructed to have a power MOS function. This field effect type semiconductor device has a st...

no. 2 example

[0101] The second embodiment is also an embodiment of the field effect type semiconductor device of the present invention, which has a trench type insulating gate. Figure 14 to Figure 17 The structure of the field effect type semiconductor device of the second embodiment is shown. Figure 15 yes Figure 14 A cross-sectional view of part B-B in the middle, while Figure 16 yes Figure 14 The cross-sectional view of part C-C in the middle. Figure 17 yes Figure 14 A cross-sectional view of part D-D in, Figure 14 yes Figure 15 to Figure 17 Cross-sectional view of part F-F in Fig. Figure 15 to Figure 17 The sectional view of the E-E part in the first embodiment is the same as that of the first embodiment figure 1 the same, where the reference numbers respectively start from "1 ** " to "2 ** ". Figure 14 The sectional view of part A-A is the same as that of the first embodiment image 3 Same, where the reference numerals are changed in the same way. In the followi...

no. 3 example

[0109] The third embodiment is also an embodiment of the field effect type semiconductor device of the present invention, which has a trench type insulated gate. Figure 22 to Figure 27 The structure of the field effect type semiconductor device of the third embodiment is shown. Figure 24 is Figure 22 and Figure 23 The cross-sectional view of part A-A in . Figure 25 is Figure 22 and Figure 23 A cross-sectional view of part B-B in the middle, while Figure 26 yes Figure 22 and Figure 23 The cross-sectional view of part C-C in the middle. Figure 27 yes Figure 22 and Figure 23 Sectional view of part D-D in . Figure 22 is Figure 24 to Figure 27 The cross-sectional view of part E-E in, Figure 23 is Figure 24 to Figure 27 Cross-sectional view of part F-F in Fig.

[0110] Like the first and second embodiments, the present field effect type semiconductor device is composed to perform the Power MOS function. In terms of structure, this embodiment has the sam...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More