Channel structure of high voltage NMOS field transistor in EEPROM peripheral circuit and manufacturing method thereof

A channel structure and peripheral circuit technology, applied in the manufacture of circuits, electrical solid devices, semiconductor/solid devices, etc., can solve the problems of increasing process cost, reducing isolation size, increasing lithography, etc., to save process cost and reduce isolation size, the effect of increasing the threshold voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0011] Since the doping concentration of the transistor channel of the EEPROM cell is usually relatively low, the isolation between the cells is difficult. A sufficiently high threshold voltage Vt2.

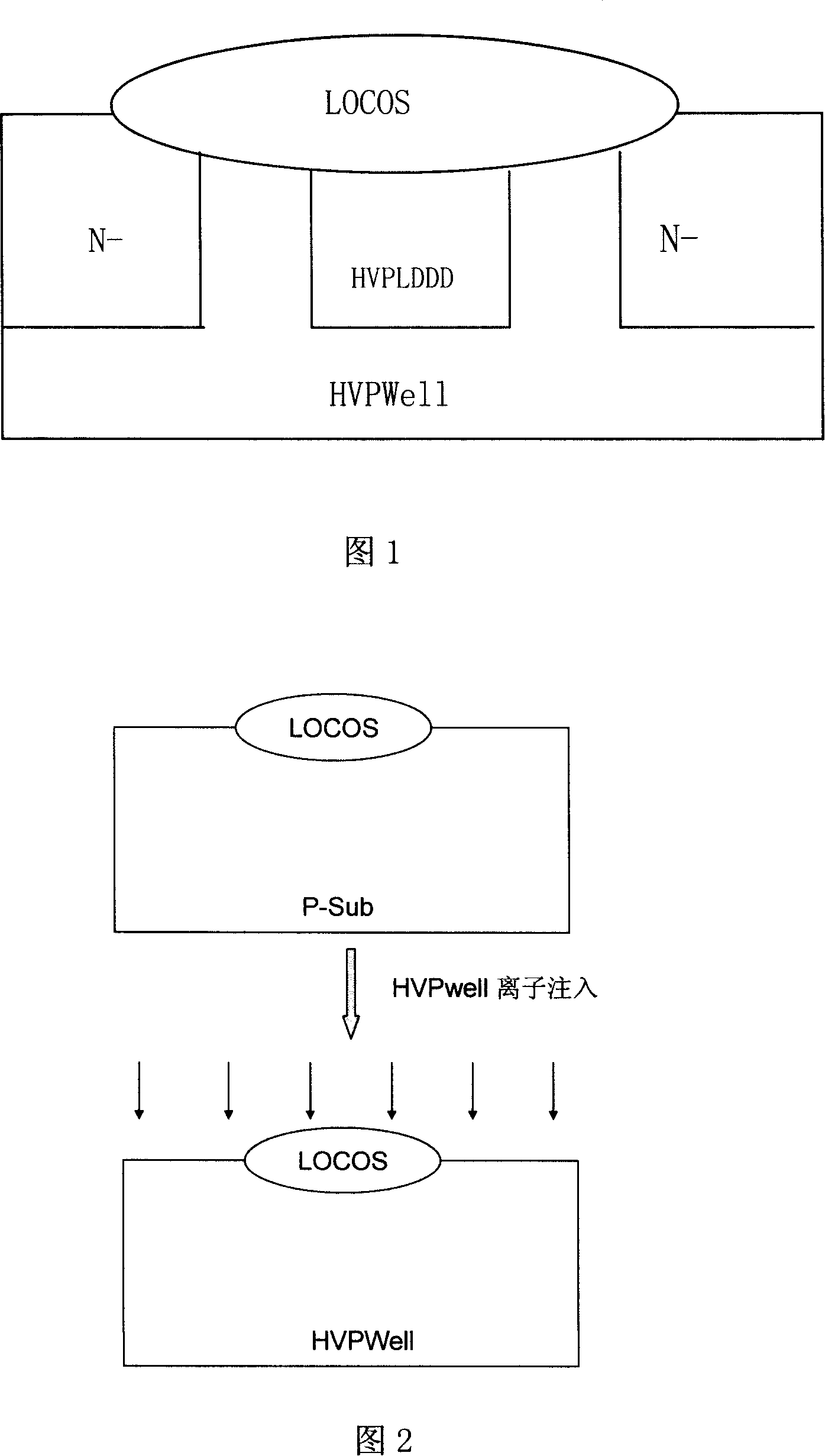

[0012] The channel structure of the high-voltage NMOS field transistor in the EEPROM peripheral circuit of the present invention is shown in Figure 1. On the high-voltage P-well (HV PWell), two lightly doped source-drain N-type N-regions of unit tubes are formed, and in the N-region Boron ions are implanted in the channel between them, and at the same time, the N-region and the channel are isolated by local silicon oxide (LOCOS). A structure in which a field implantation region is embedded in the channel of the field effect transistor is formed.

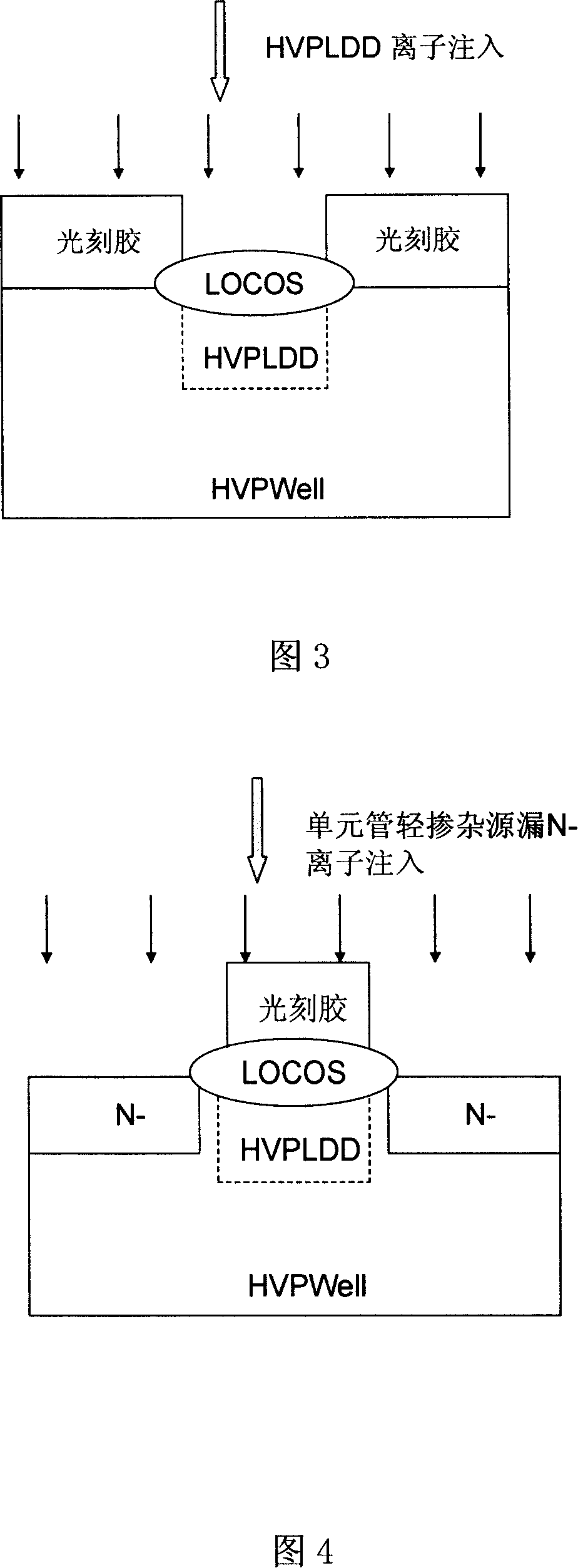

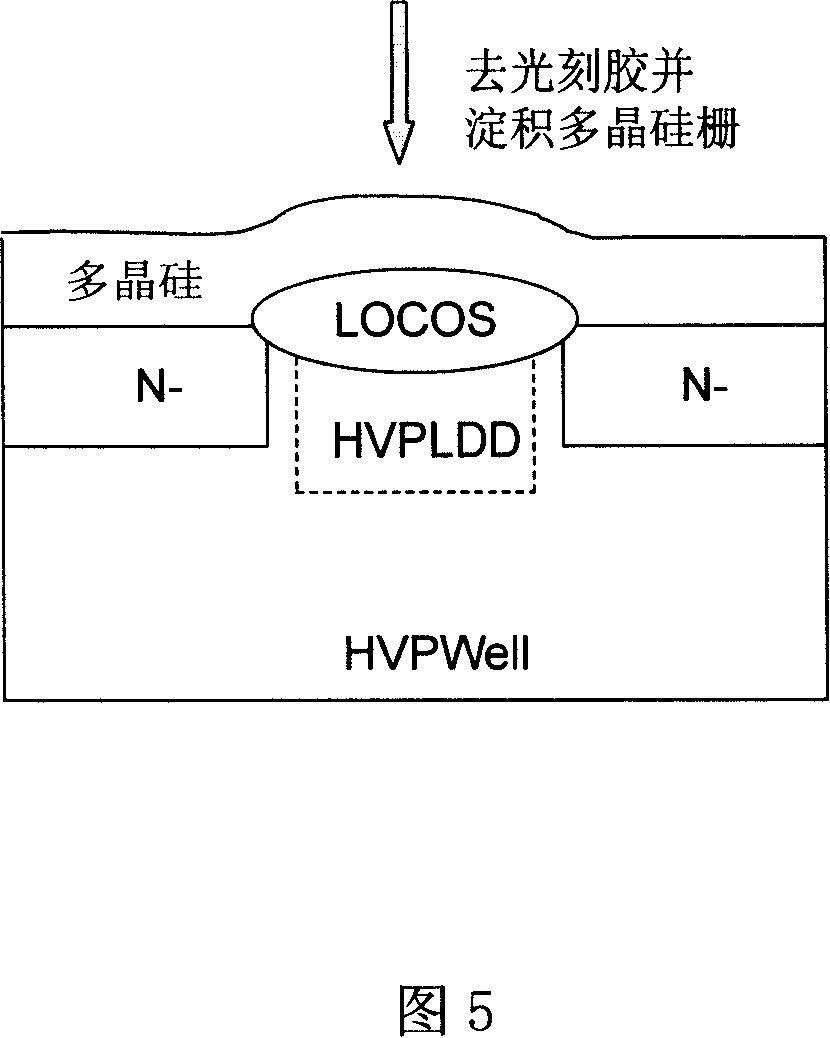

[0013] The manufacturing process flow of the high-voltage NMOS field transistor that realizes the above channel structure is:

[0014] On a P-type substrate (P-Sub) with LOCOS isolation, HV Pwell ion implantation is performed to form ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More