Layered power source noise monitoring device of ultra large scale integrated circuit and system

A large-scale integrated circuit, power supply noise technology, applied in the direction of electrical solid devices, circuits, electrical components, etc., can solve the problems of limiting noise measurement time resolution, unreliable reference voltage, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

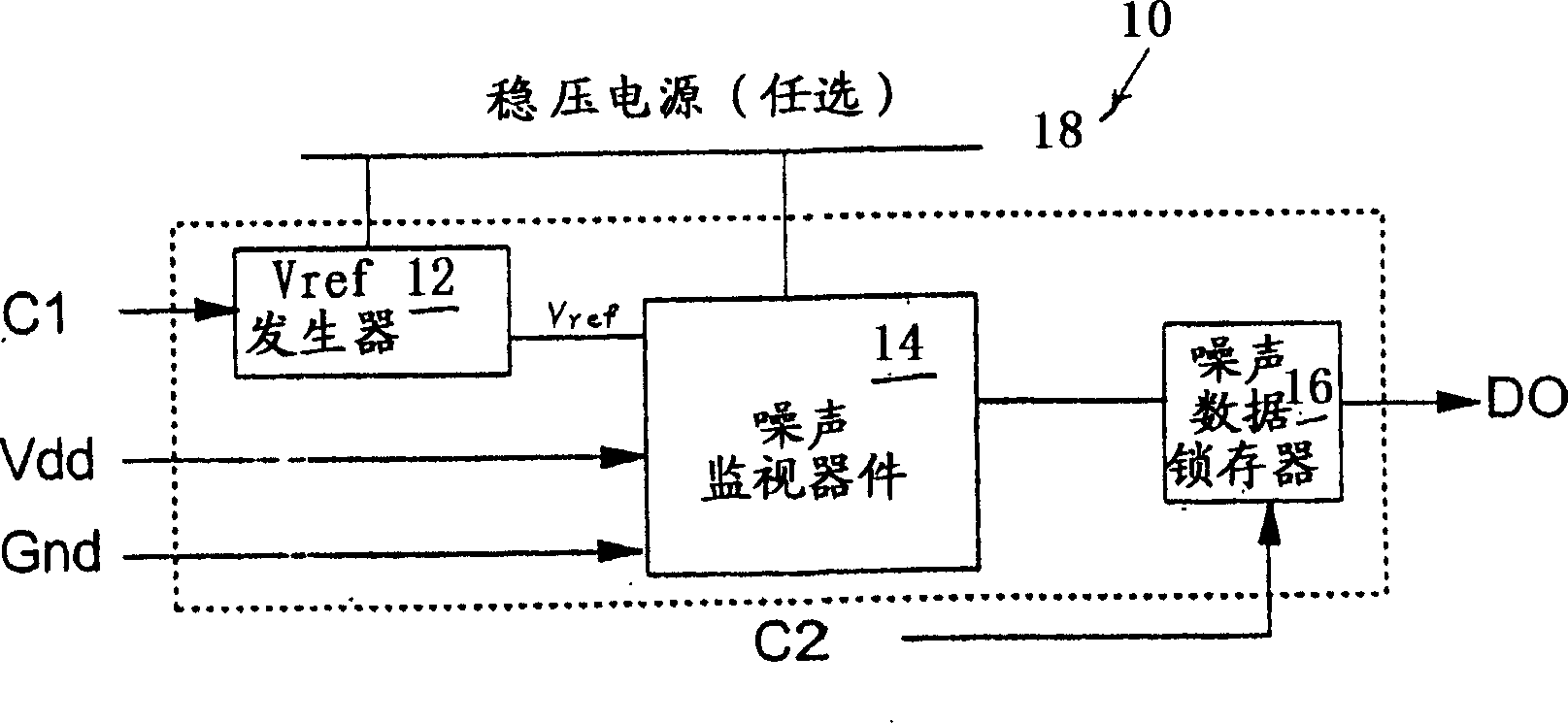

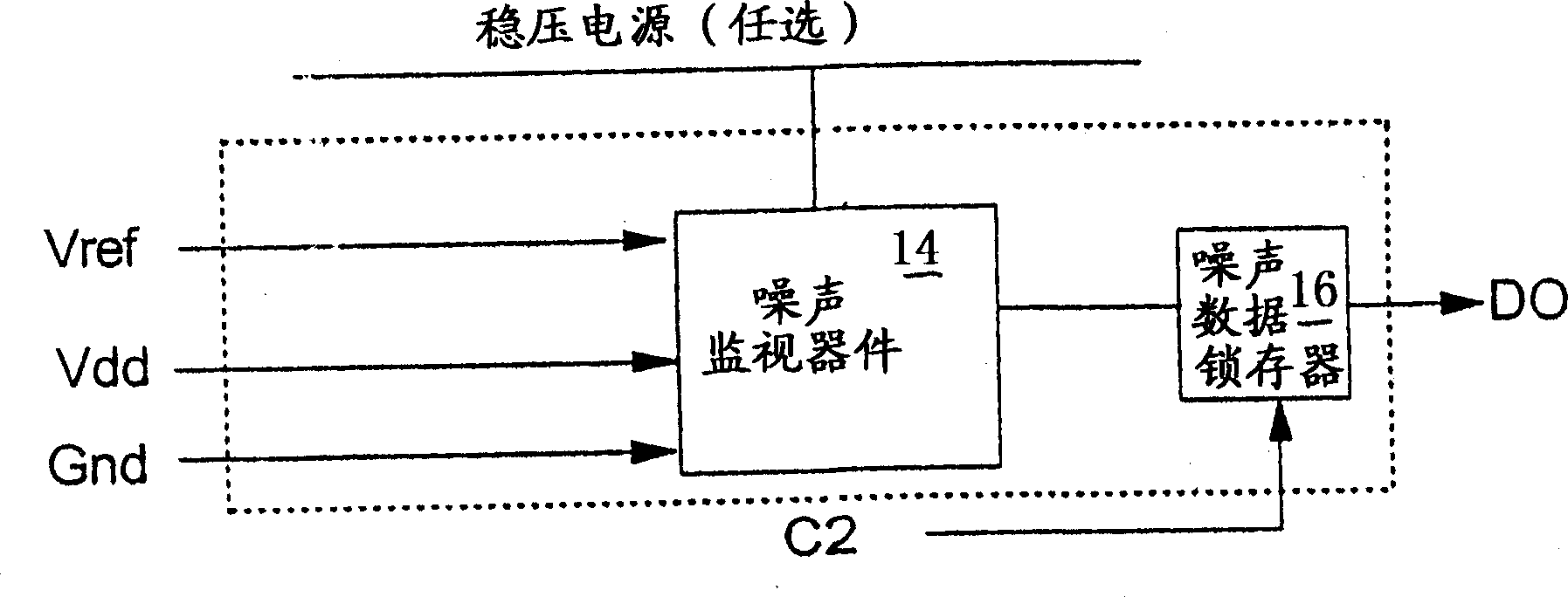

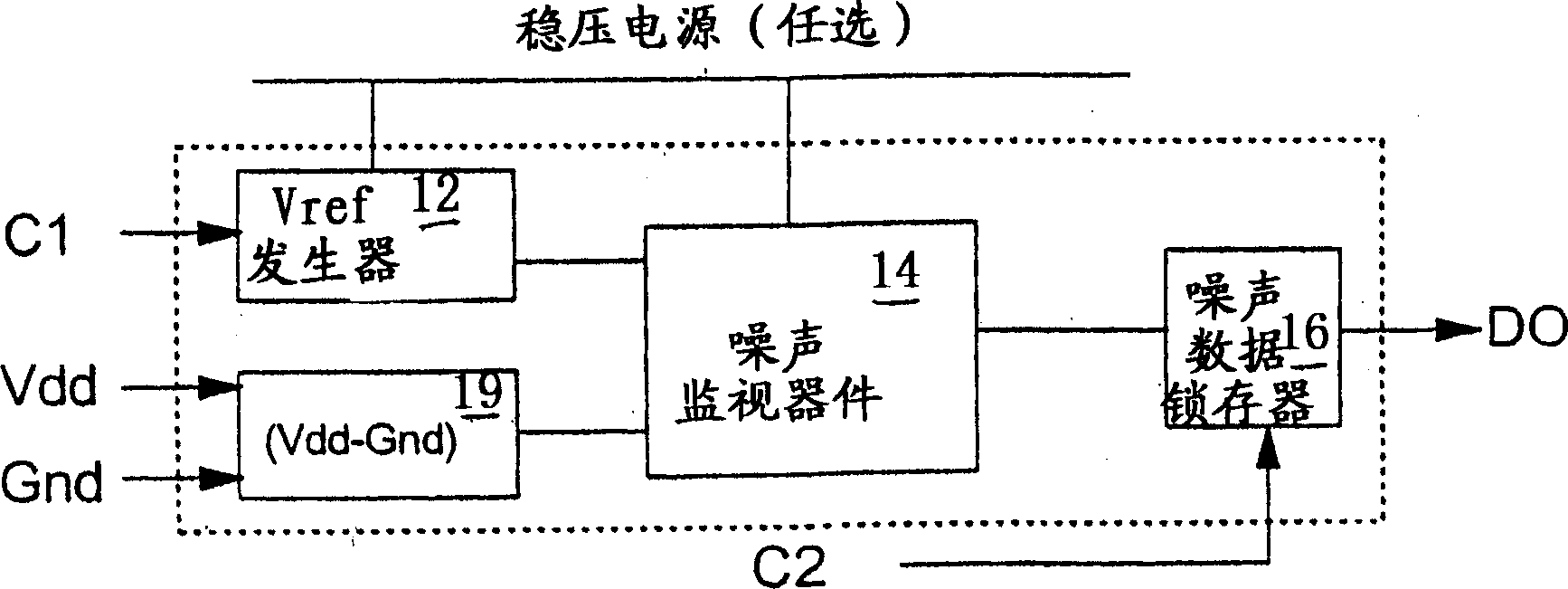

[0023] In the present invention, a noise monitoring device is fabricated on a chip to measure the noise on the chip. A noise monitoring system includes multiple such on-chip noise monitoring devices distributed at various critical places on the chip. A noise analysis algorithm analyzes noise characteristics based on the noise data collected by these noise monitoring devices, and a layered noise monitoring system maps the noise of each core to the system-on-chip.

[0024] Each macro (macro) is internally designed with a high-resolution on-chip noise monitoring device. Monitor the noise of individual macros in parallel or sequentially to measure noise interference between different macros. The hierarchical noise monitoring system monitors and stores per-core and per-chip power supply noise information as part of the internal self-test (BIST) system. This approach can be further extended from chip-level systems to package-level systems to provide hierarchical full-spectrum nois...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com