Manufacturing method of multilayer printed circuit board

A multi-layer printing and circuit board technology, applied in the direction of printed circuit manufacturing, multi-layer circuit manufacturing, printed circuit, etc., can solve the problems of prolonging the manufacturing time, increasing the manufacturing cost, high impedance of the wall circuit layer, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

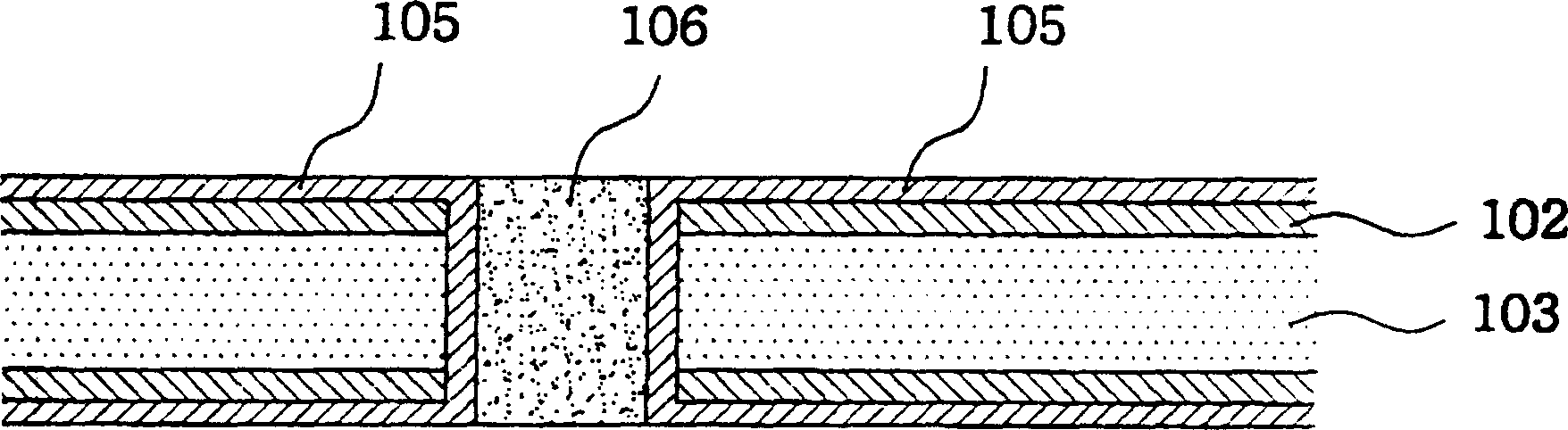

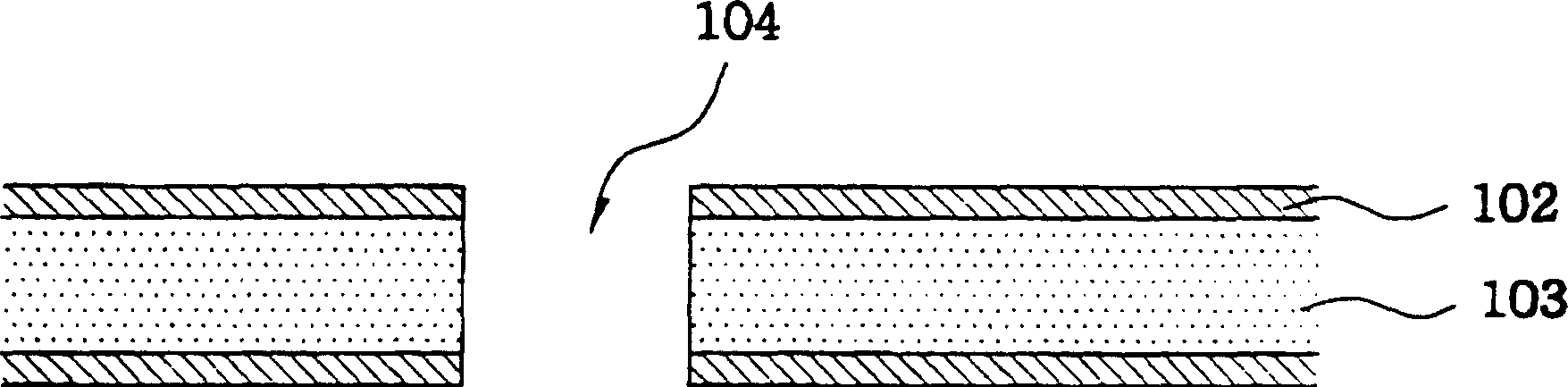

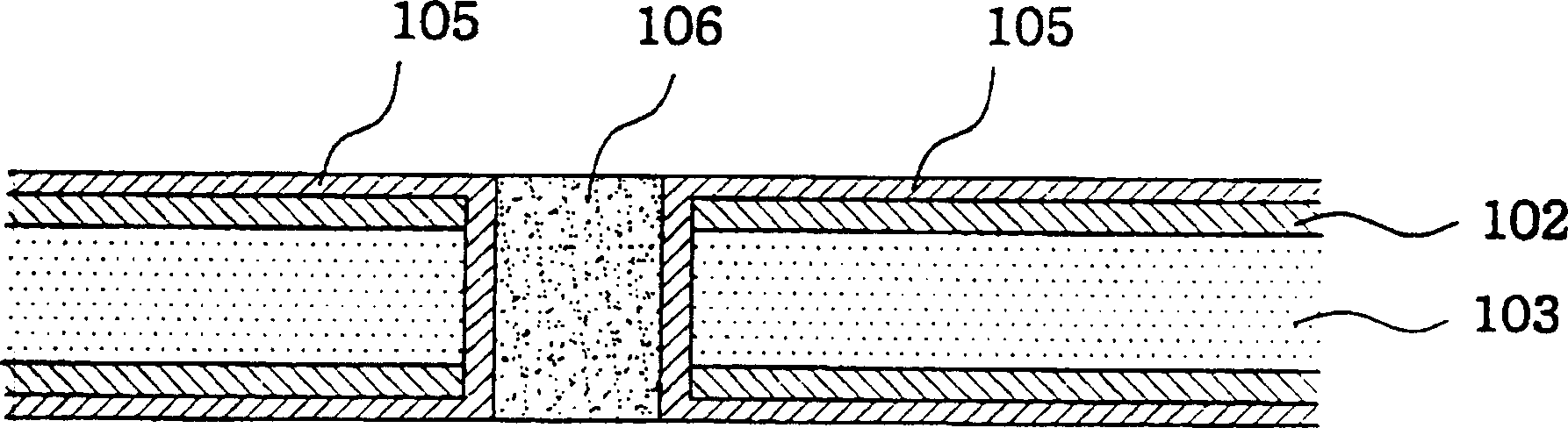

[0052] Reference is now made to the drawings, wherein the same reference numerals are used in different drawings to designate the same or like parts.

[0053] Figure 7 A lamination process of circuit layers and insulating layers is shown. The circuit layers 306a, 306b and 306c and the insulating layers 506a and 506b are respectively formed according to different processes, and they are arranged in a manner of alternately stacking the circuit layers and the insulating layers, such as Figure 7 shown, and then press them so that they touch each other in order to manufacture such as Figure 8 The six-layer PCB shown.

[0054] The different processes for making the circuit layer and insulating layer are now described.

[0055] 2A-2E are respectively cross-sectional views showing the fabrication of circuit layers constituting a multilayer PCB according to a first embodiment of the present invention, the fabrication process being performed according to a conventional technique. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More