Frame synchronous circuit and method for eliminating time frequency deviation effect of orthogonal FDM

A technology of multiplexing signals and time-frequency deviation, applied in the directions of orthogonal multiplexing system, multiplexing communication, synchronization device, etc., can solve the problems of carrier frequency deviation and sampling clock deviation, detection failure, etc., to achieve Strong anti-interference ability, simple algorithm and flexible structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

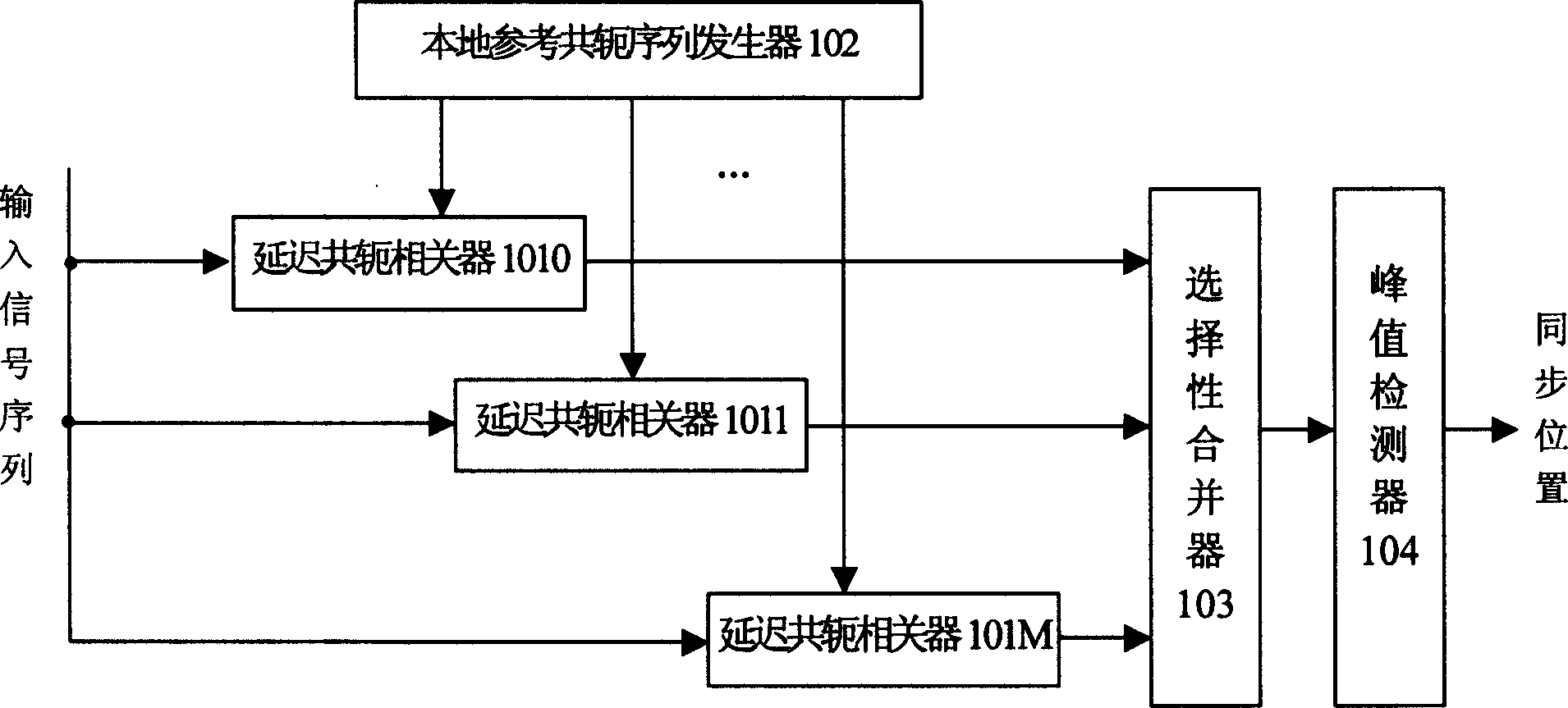

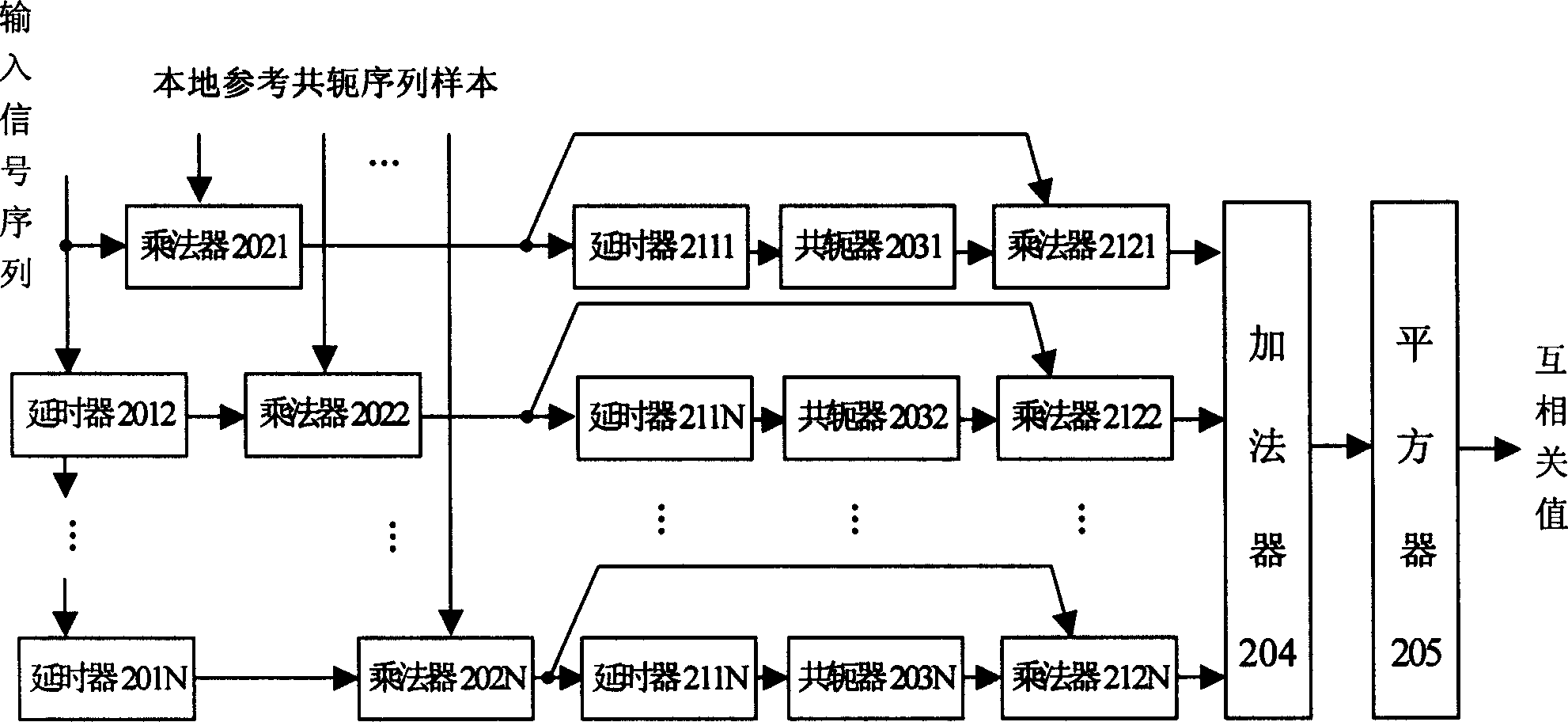

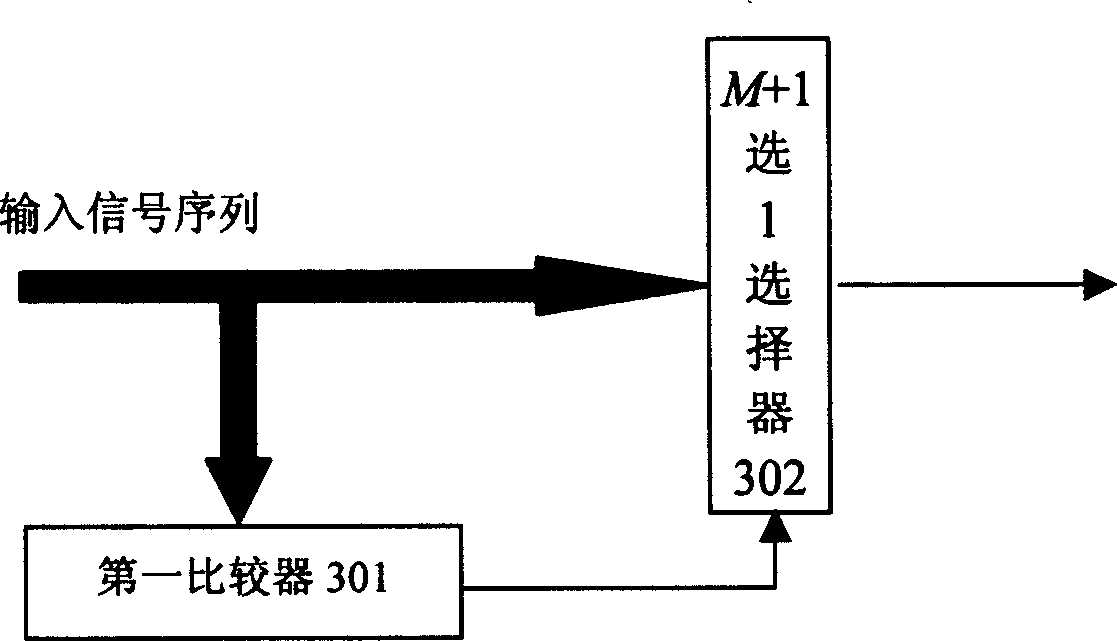

[0041] According to one aspect of the present invention, a kind of OFDM frame synchronous detection circuit based on delay conjugate correlation is provided (referring to appended figure 1 ), the number of parallel branches is M+1, and M is any positive integer. The M+1 parallel frame synchronization detection circuit includes: a local reference conjugate sequence generator, which is used to generate the conjugate values of the local reference sequence samples of different time delays of the training sequence; M+1 delay conjugate correlators, used It is used to calculate the delay conjugate correlation value between the local reference conjugate sequence sample value and the input signal sequence; a selective combiner is used to select the maximum value from the correlation values output by M+1 delay conjugate correlators; a A peak detector is used to perform peak detection on the selected maximum value, and output the peak position as the position of OFDM frame synchroniz...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More