Multiplier restructuring algorithm and circuit thereof

A technology for reconstructing algorithms and multipliers, which is applied in the field of microelectronics, and can solve the problems of multiplier computing power difficulty, speed, power consumption and area that cannot be satisfied

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

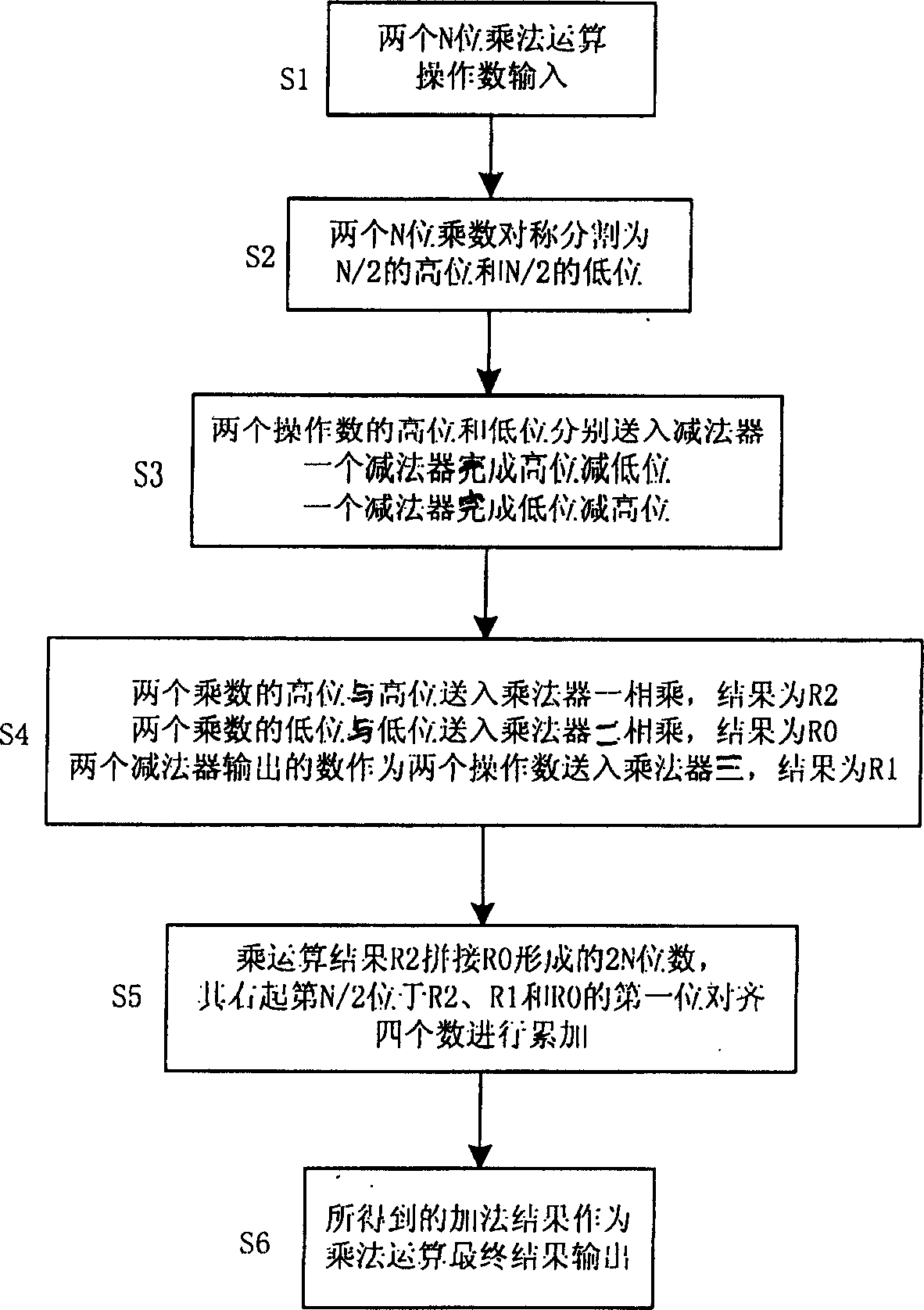

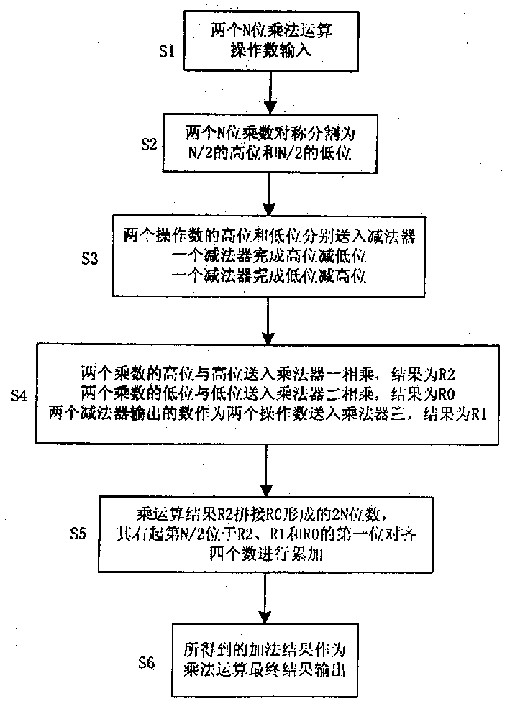

Method used

Image

Examples

Embodiment Construction

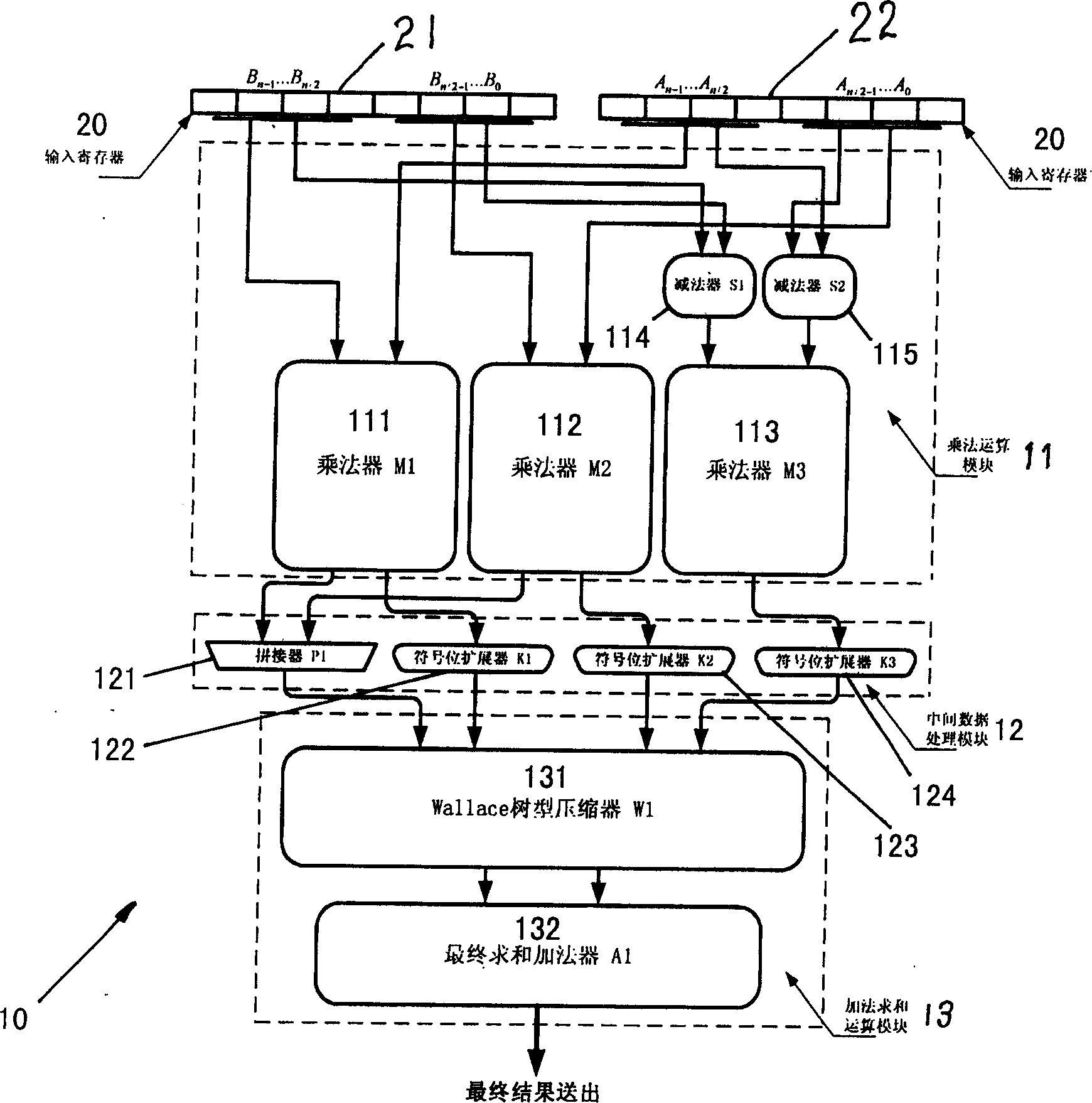

[0025] see figure 2 , a novel reconstruction algorithm multiplier circuit implementation structure of the present invention, including:

[0026] One input multiplication operand register 20, this register 20 preserves two N-bit multiplication operands of external input;

[0027] An N-bit novel reconstruction algorithm multiplier circuit 10, which is connected to the input multiplication operand register 20.

[0028] The N-bit novel reconstruction algorithm multiplier circuit 10 includes a multiplication operation module 11 , an intermediate data processing module 12 , and an addition and summation operation module 13 . The multiplication operation module 11, the intermediate data processing module 12 and the addition and summation operation module 13 are connected in sequence.

[0029] The first subtractor 114 of two N / 2 positions, the second subtractor 115 and the first multiplier 111 of three N / 2 positions, the second multiplier 112, and the third multiplier are arranged ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More