Regulator device and regulation method

A debugger and memory unit technology, applied in software testing/debugging, instrumentation, special data processing applications, etc., can solve problems such as inability to simulate instructions, failure to simulate, and increased area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

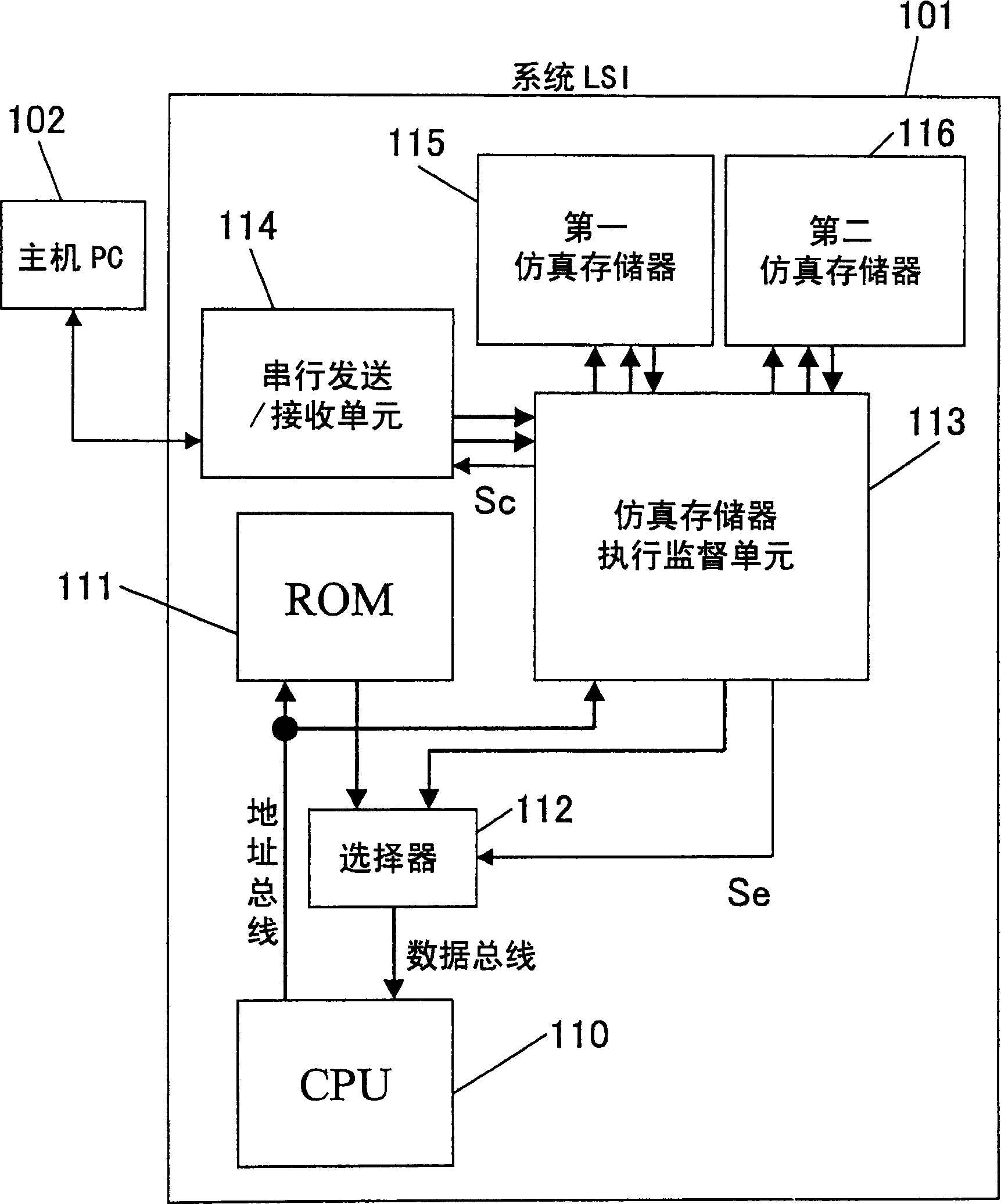

[0115] Such as figure 1 As shown, the system LSI 101 includes a CPU 110 , a ROM 111 , a selector 112 , an emulation memory execution supervision unit 113 , a serial transmission / reception unit 114 , a first emulation memory 115 , and a second emulation memory 116 . Hereinafter, the emulation memory execution supervisory unit will be abbreviated as execution supervisory unit, the serial transmission / reception unit will be abbreviated as transmission / reception unit, the first emulation memory will be abbreviated as first E-memory, and the second emulation memory will be abbreviated as first E-memory. Two E-memory. A host PC (hereinafter, abbreviated as PC) 102 is a computer in which debugger software capable of serial transmission and reception with respect to the transmission / reception unit 114 is installed.

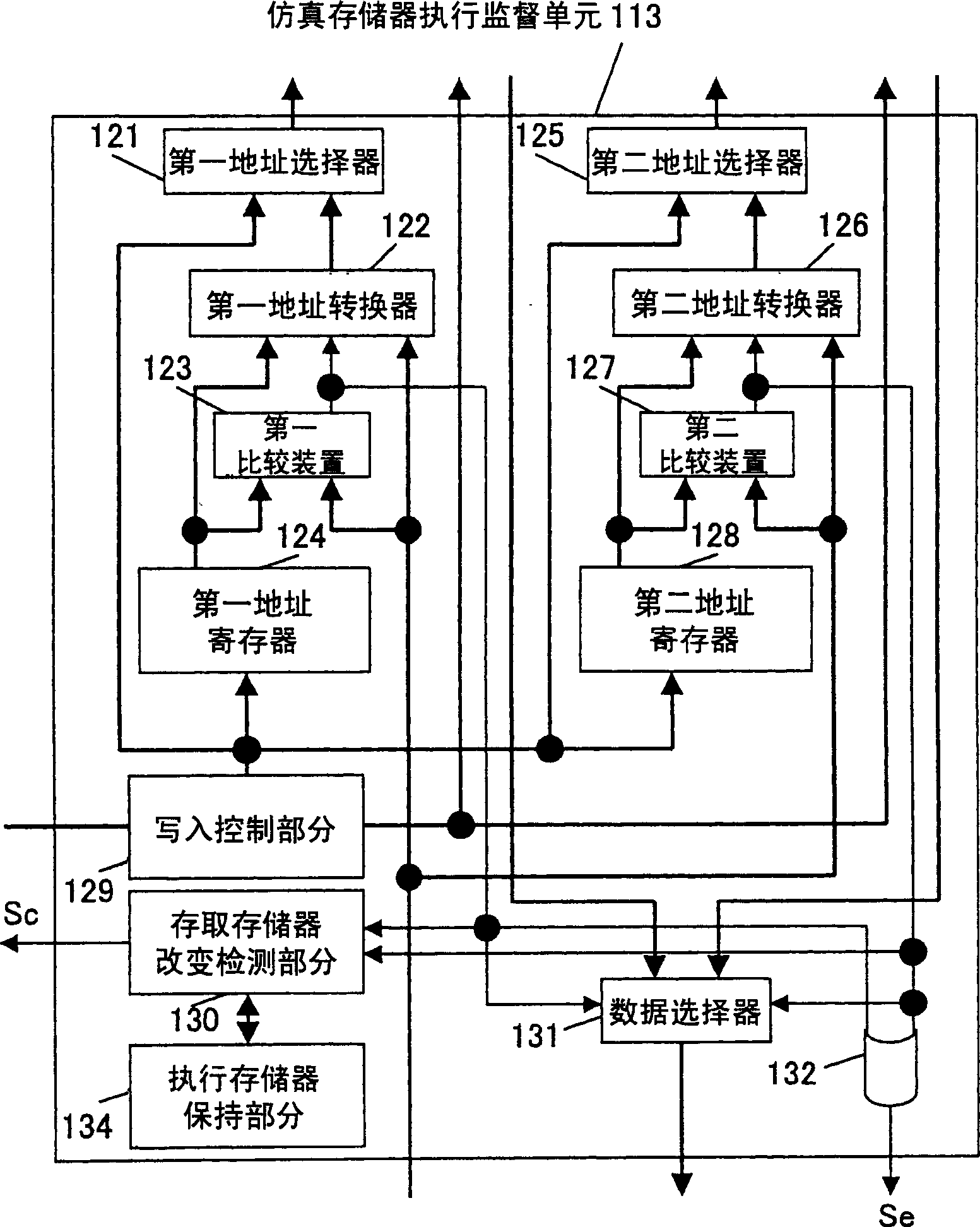

[0116] Such as figure 2 As shown, the execution supervision unit 113 includes a first address selector 121, a first address converter 122, a first comparison device 12...

Embodiment 2

[0148] In Embodiment 1, when there is an unconditional branch instruction before the bottom line of the storage capacity of the E-memory, the destination of the transferred instruction is switched to other E-memory without using all of the E-memory area. Therefore, additional overhead due to traffic during transfer of instructions is generated. Embodiment 2 of the present invention addresses this inconvenience. In Example 2, the figure 1 together as a reference.

[0149] Such as Figure 4 As shown, the E-memory execution supervisory unit 113a includes: a first address / byte number register 136, replacing Embodiment 1 ( figure 2 ) in the first register 124; and a second address / byte count register 138 in place of the second register 128 therein. In the following description, the first address / byte number register is abbreviated as the first register, and the second address / byte number register is abbreviated as the second register. The first and second registers 136 and 1...

Embodiment 3

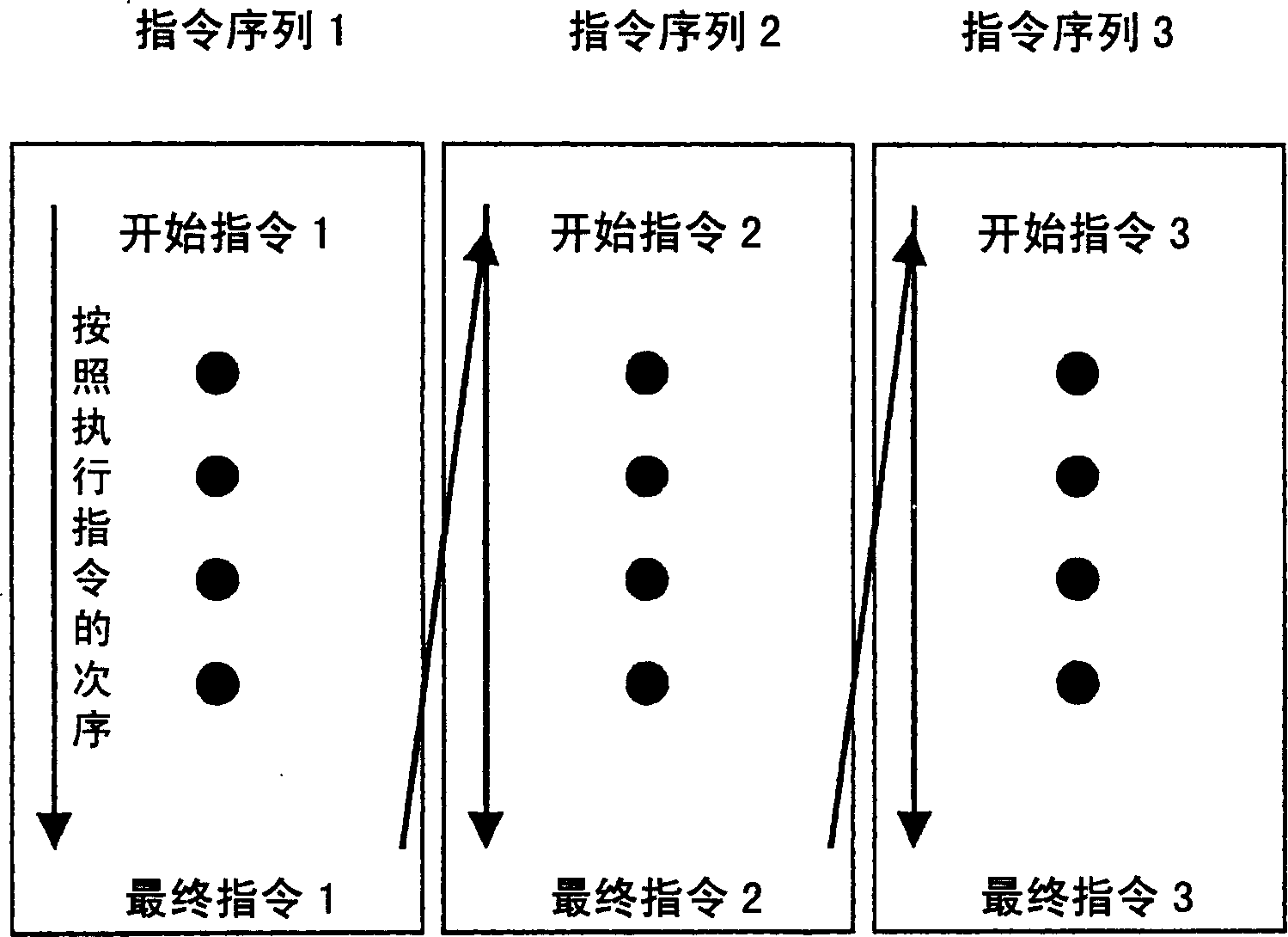

[0171] In Embodiment 2, even when the branch destination of the unconditional branch instruction of instruction sequence 1 fits in the same E-memory, the instruction preceding from the branch destination is written into other E-memory as instruction sequence 2. Therefore, additional overhead due to transferring traffic is increased. Embodiment 3 of the present invention addresses this inconvenience. In Example 3, the figure 1 and 4 together as a reference.

[0172] Figure 6 A sequence of instructions including an unconditional branch instruction whose branch destination occurs in E-memory is shown.

[0173] 1. Operation of writing instructions to E-memory

[0174] The host traces the instructions from the start instruction according to the execution sequence, so as to determine whether the branch destination corresponds to the memory area of the first E-memory 115 where the unconditional branch instruction appears. When corresponding to this, the host computer does no...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More