Data transfer memory

A data transmission and memory technology, applied in static memory, memory system, read-only memory, etc., can solve the problem of inability to reduce the number of components constituting a module, and achieve the effect of reducing the number of components

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

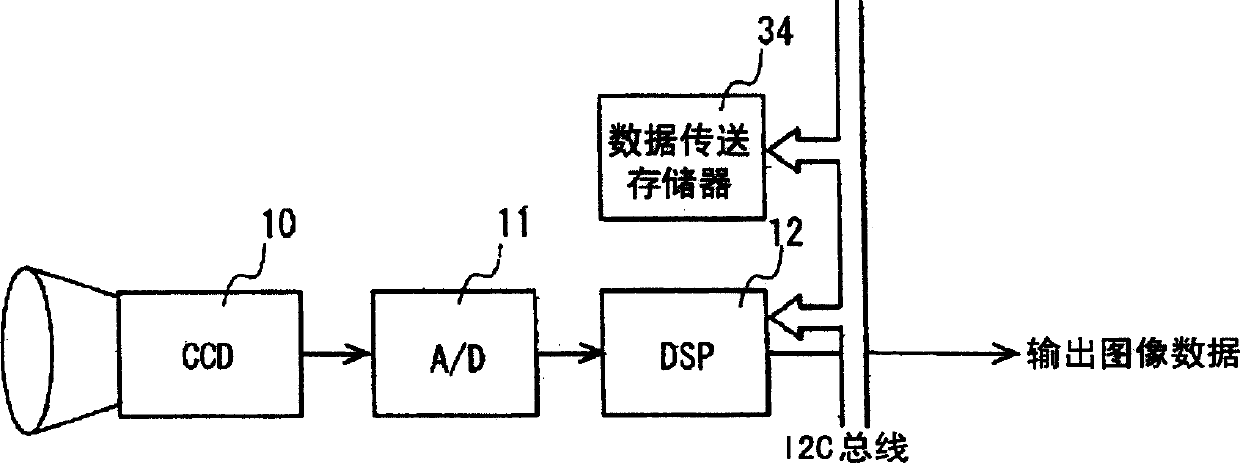

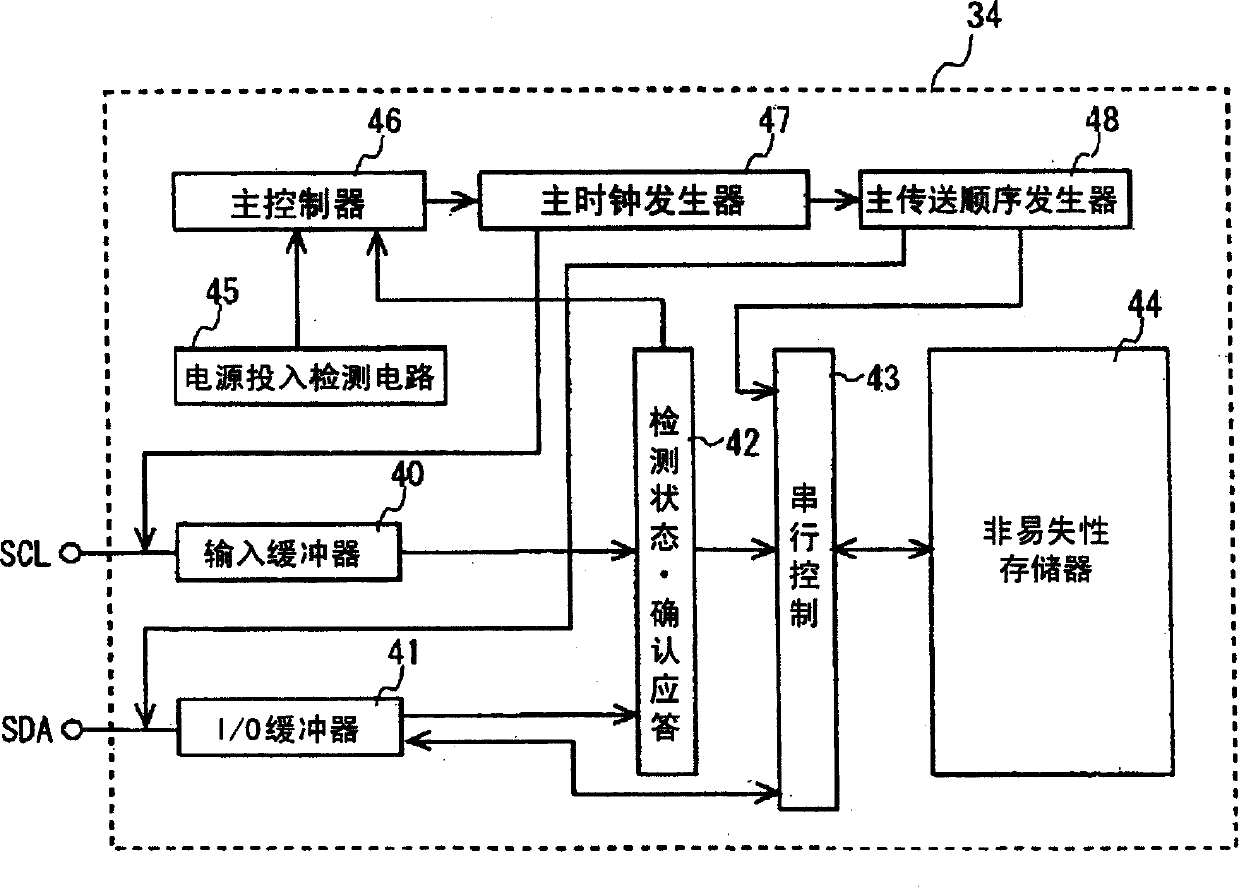

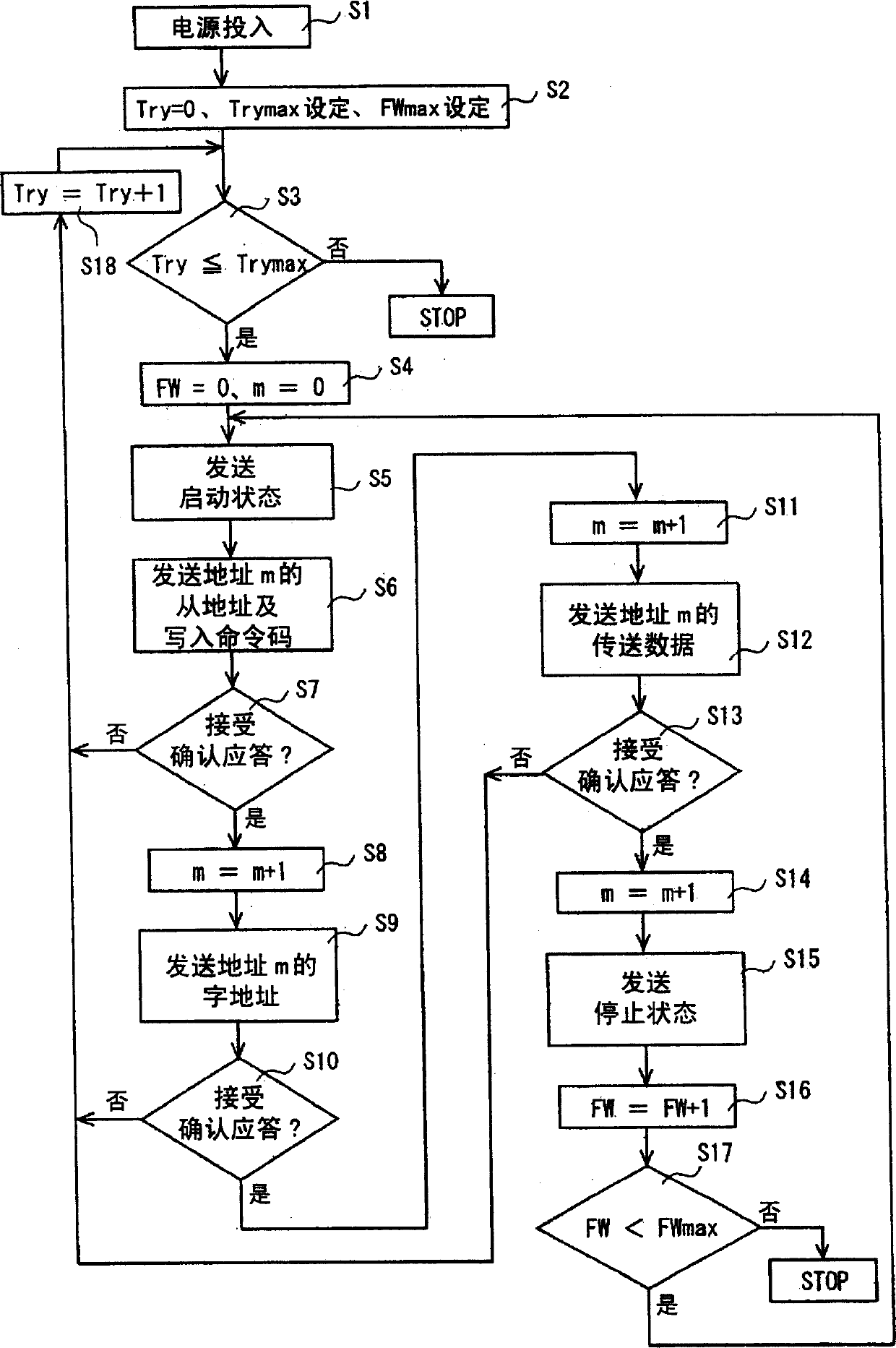

[0038] FIG. 1 is a block diagram showing the configuration of a module for a CCD camera according to an embodiment of the present invention. The camera module is composed of CCD10, A / D conversion circuit 11, and DSP12. These are the same as the conventional camera module shown in FIG. 11 . In this embodiment, the data transfer memory 34 is connected via an I2C bus. In the data transfer memory 34, a DSP control program and camera adjustment data (including, for example, white balance characteristics of the CCD 10, dispersion correction data of the mechanical shutter, etc.) and the like are stored.

[0039] The data transfer memory 34 acts as a master device when the power is turned on or the CCD10 is activated, and writes the DSP control program and camera adjustment data (such as white balance characteristics) into the slave device DSP12 through the I2C bus. Thereby, the DSP 12 becomes capable of performing predetermined image signal processing and camera adjustment (for exa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More