Minitype EEPROM matrix structure

A technology of read-only memory and matrix structure, which is applied in read-only memory, static memory, information storage, etc., can solve the problems that the effective bit unit of EEPROM cannot be reduced, and the area is large, so as to improve the integration The effect of reducing the size, reducing the area and reducing the width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

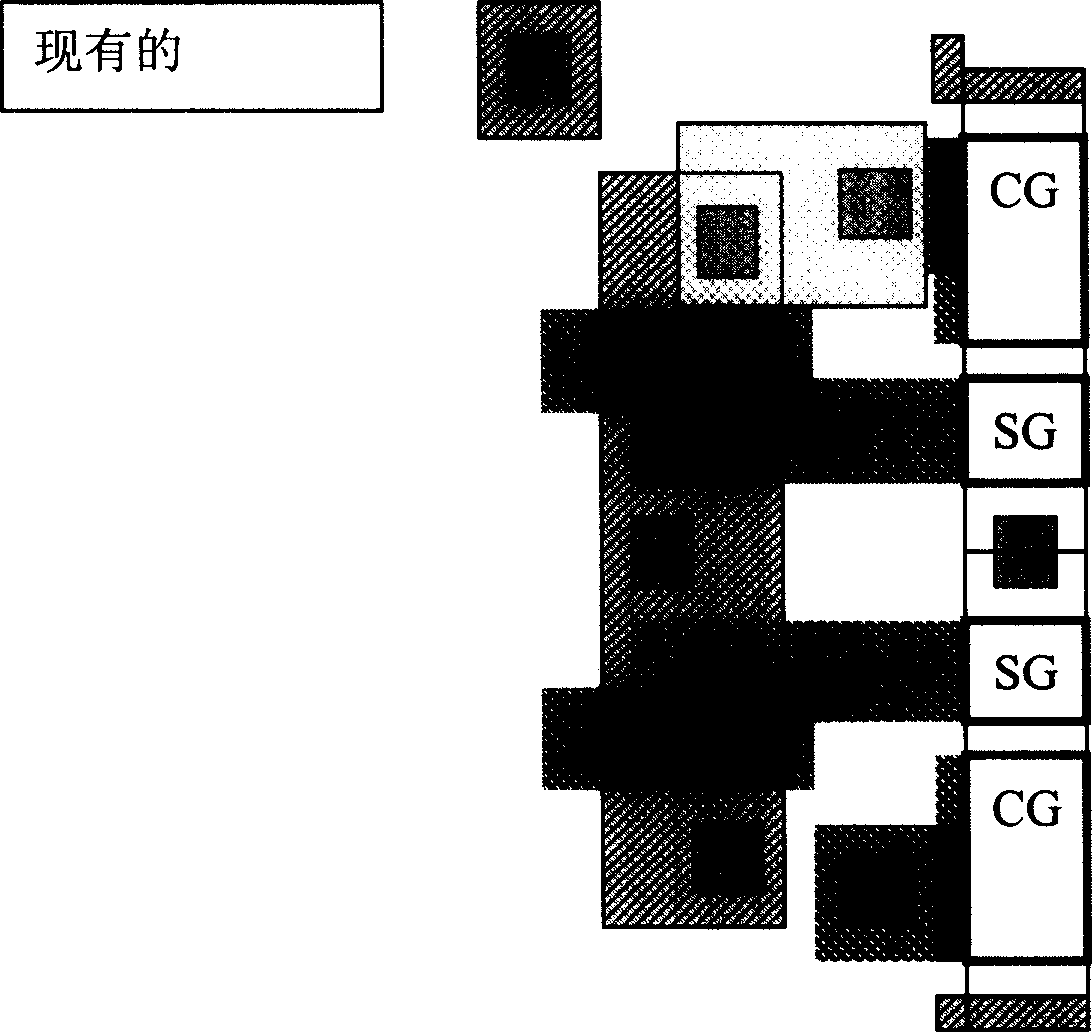

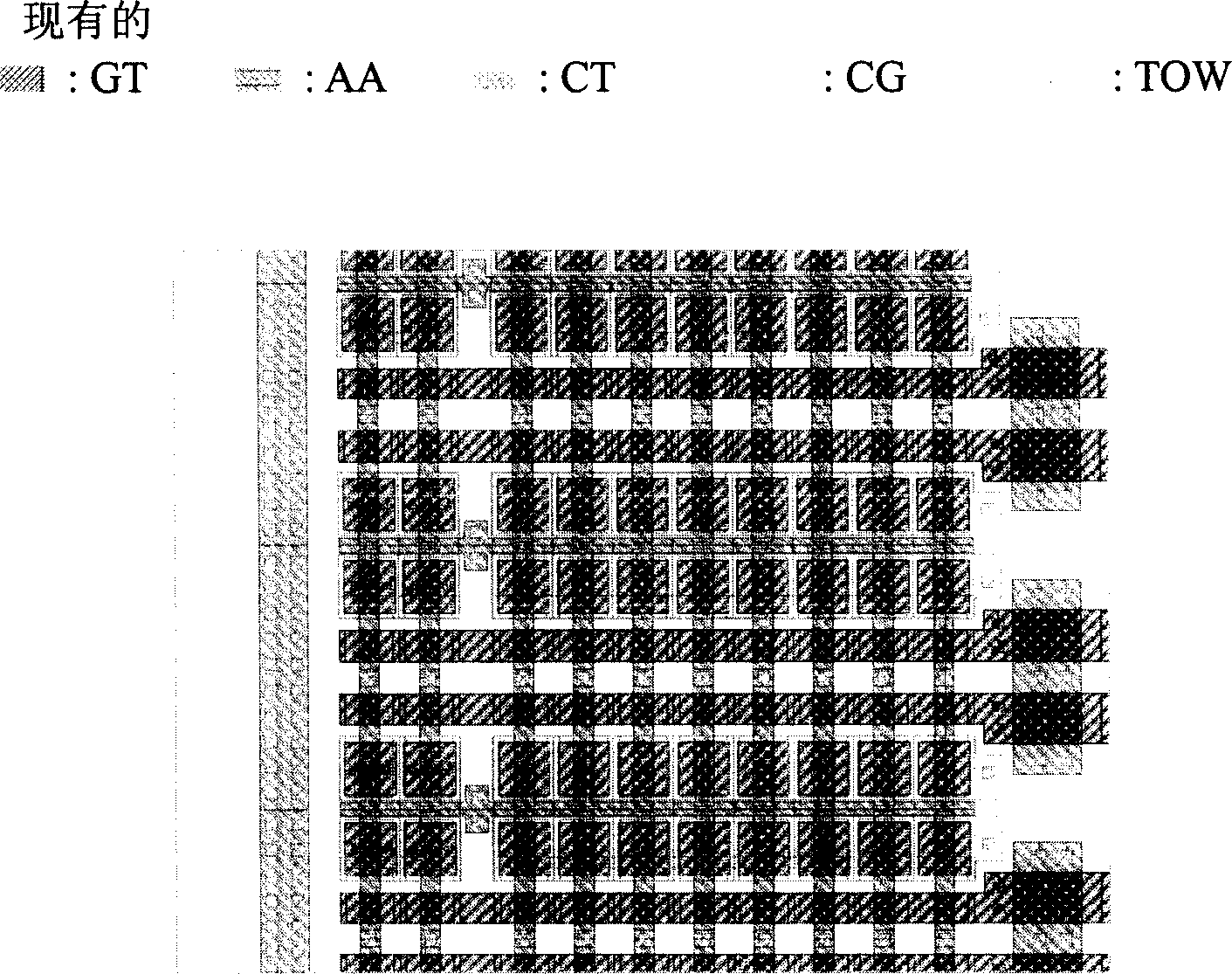

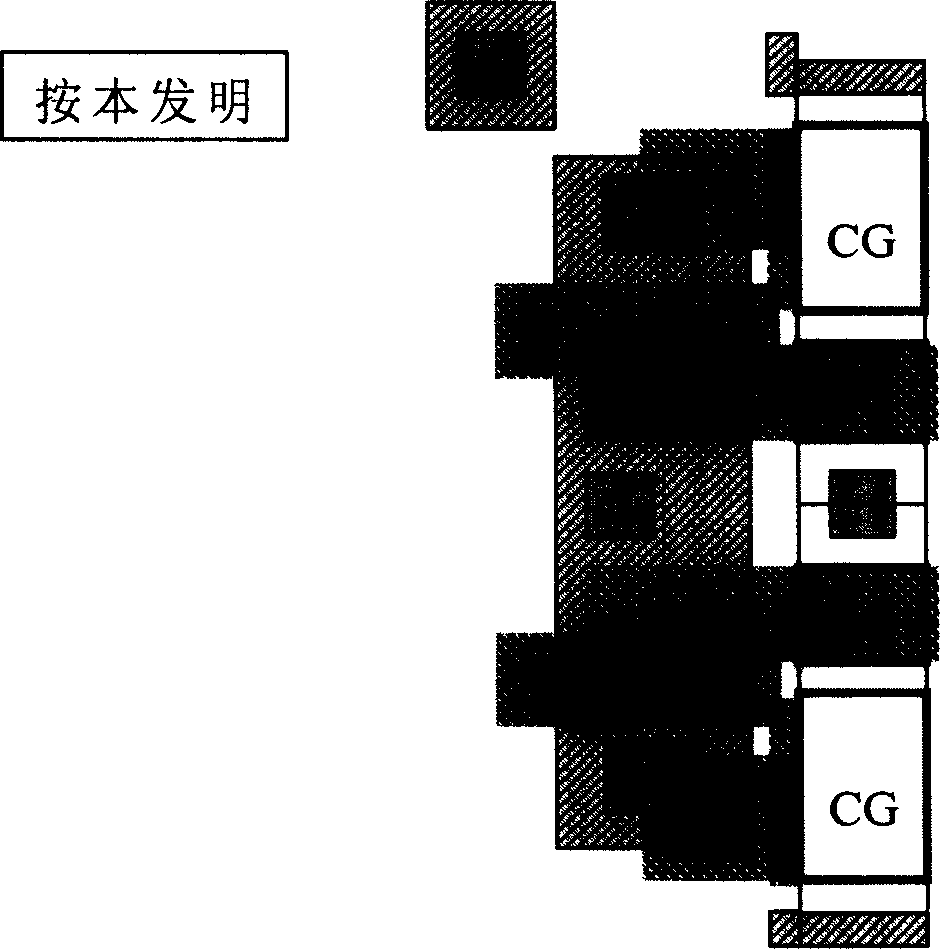

[0015] figure 1 It is a schematic diagram illustrating the matrix structure of the existing electrically erasable programmable read-only memory. figure 2 It is a schematic diagram illustrating the layout of signal gate-signal gate contacts in the existing EEPROM matrix structure. image 3 Is to illustrate the electrical erasable programmable read-only memory matrix structure according to the present invention pair Signal Grid Layout- pair Schematic diagram of a junction with enlarged signal bars. Figure 4 It is a partially enlarged schematic diagram illustrating the dual signal gate layout-enlarged dual signal gate contacts in the EEPROM matrix structure of the present invention. and Figure 5 It is a schematic diagram illustrating the dual signal gate layout-double signal gate enlarged contacts in the EEPROM matrix structure of the present invention.

[0016] Referring now to the accompanying drawings, describe in detail the matrix structure of the small electrically...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com