Image compression chip based on image block dynamic division vector quantization algorithm

An image compression and vector quantization technology, applied in image communication, television, electrical components, etc., can solve problems such as large computational load and high complexity restricting applications, and achieve the effect of improving the compression ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

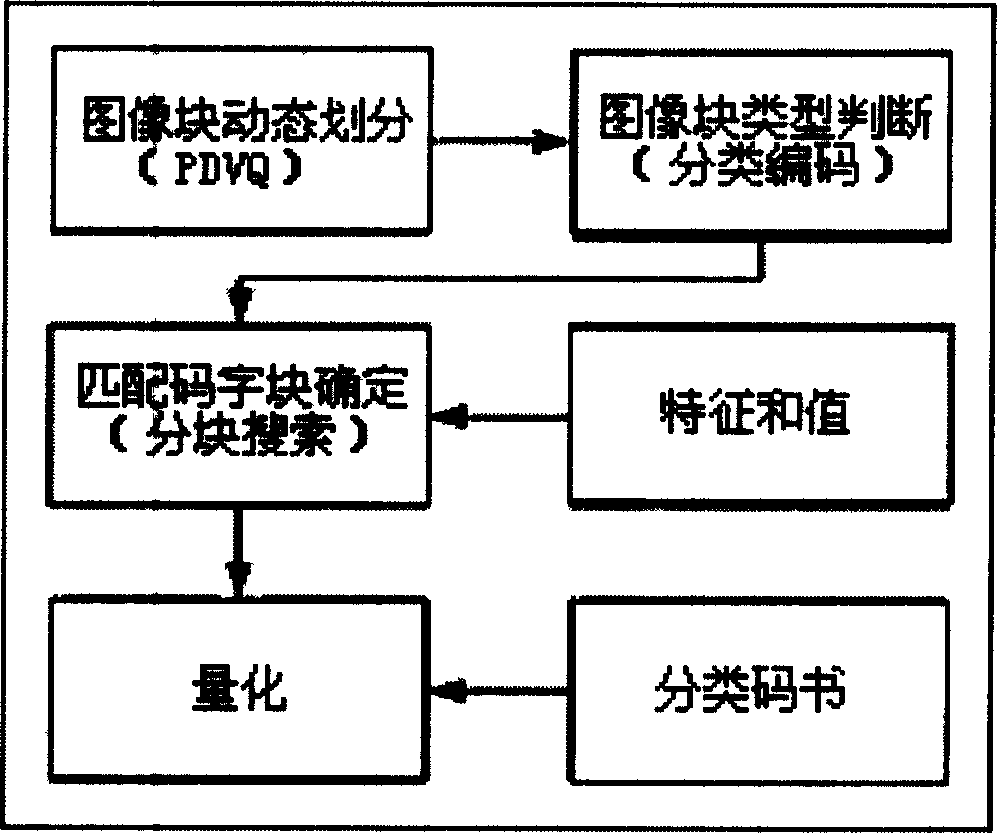

Method used

Image

Examples

Embodiment Construction

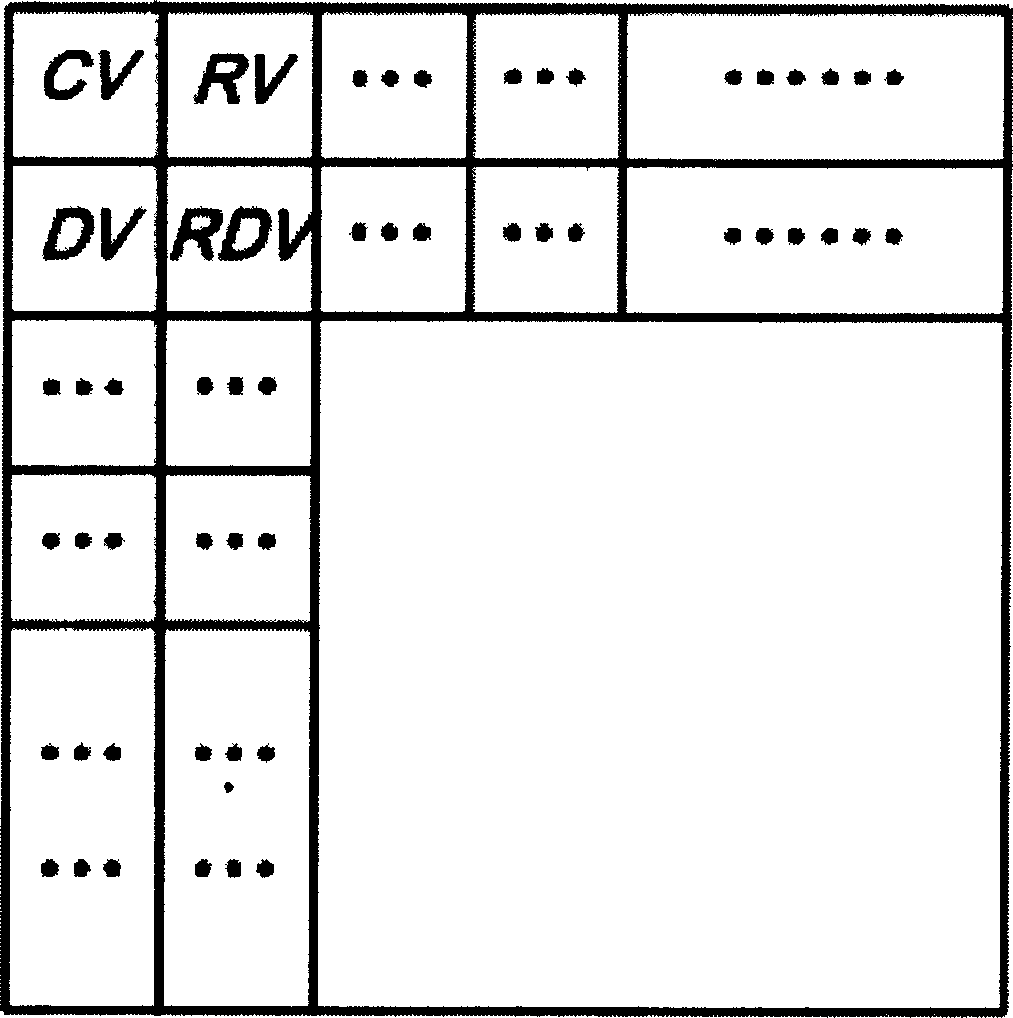

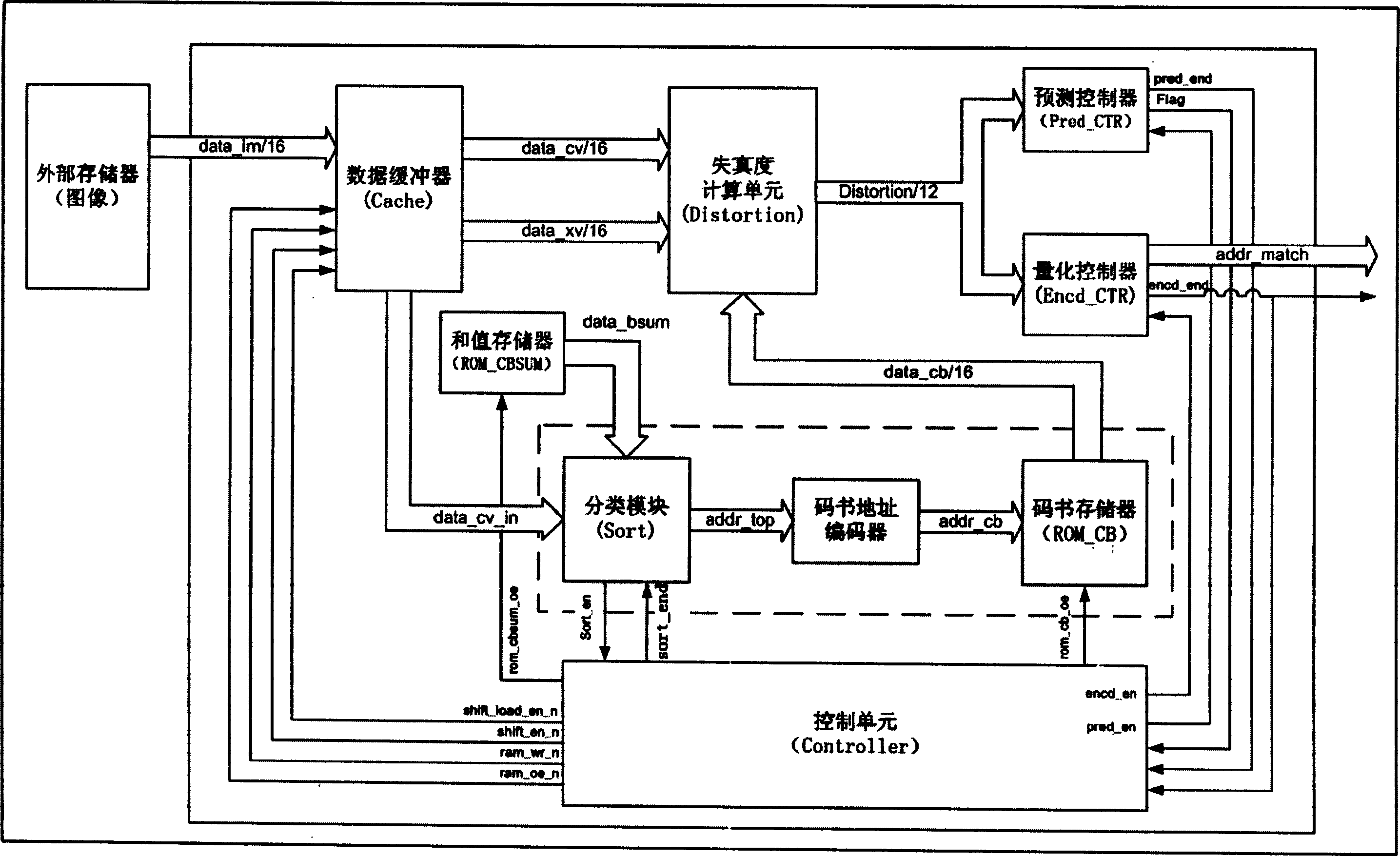

[0039] The specific structure of the image compression chip based on the image block dynamic division vector quantization algorithm of the present invention can be found in image 3 , the chip includes an external memory, a control unit, a data buffer, a classification module, a codebook address encoder, a codebook memory, a distortion calculation unit, a prediction controller, a quantization controller, and a value memory; the image to be encoded is stored in an external In the memory, a buffer (Cache) stores data of an 8×8 image block (including the current sub-image block CV and adjacent sub-image blocks DV, RV, and RDV). The data buffer (Cache) is connected to the external memory through the 16-bit data line data_im. Under the control of the signal shift_load_n, shift_en_n, ram_wr_n, ram_oe_n from the control unit (Controller), it outputs the pixel value to the distortion calculation unit (distortion) and classification Module (Sort).

[0040] The connection between the dat...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap