Semiconductor device and method for manufacturing the same

A manufacturing method and semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve the problems of reduced protection performance, reduced controllability of plasma damage, difficulty in efficiently releasing plasma current, etc., to prevent Plasma current destruction, the effect of avoiding the rise of withstand voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

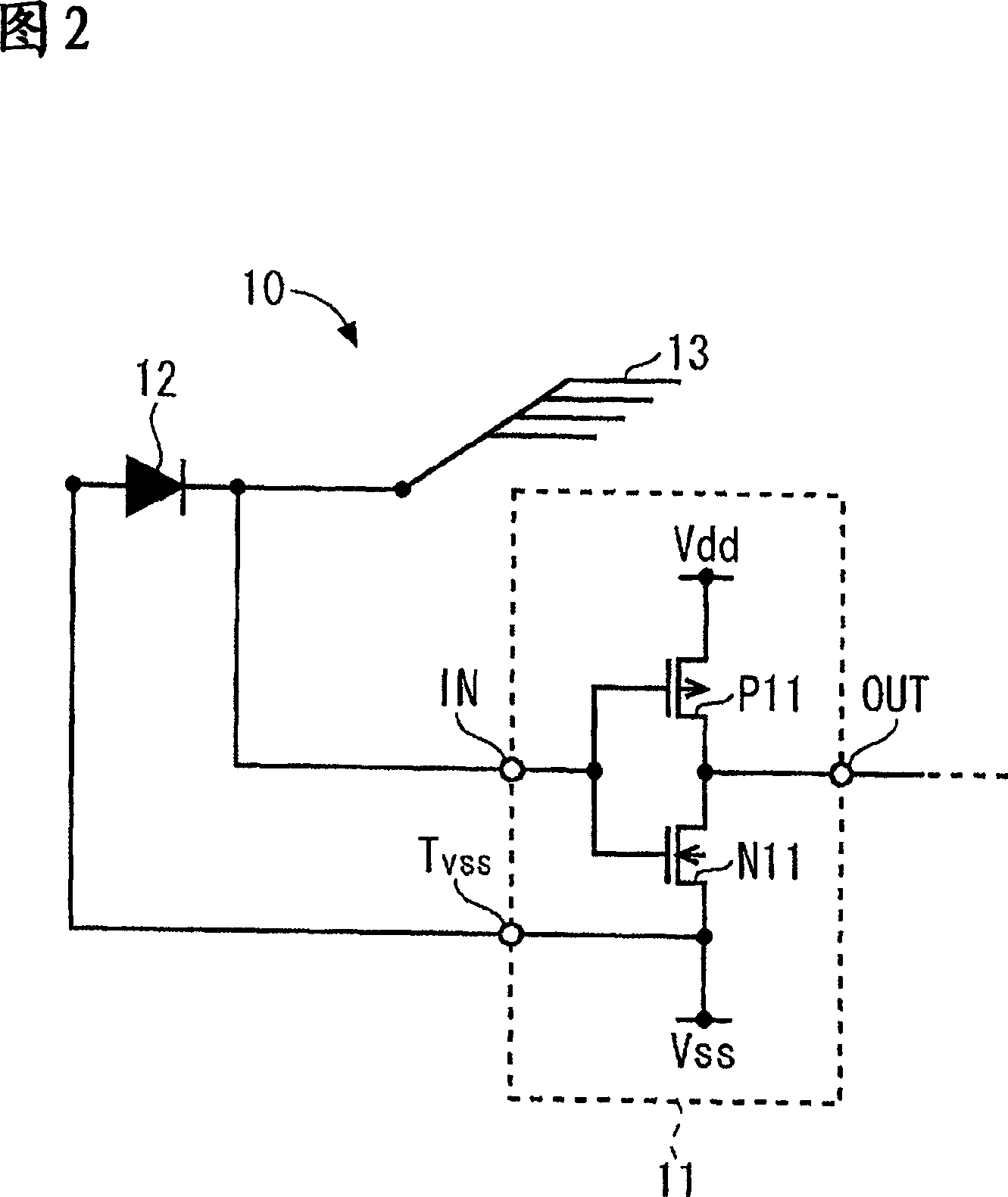

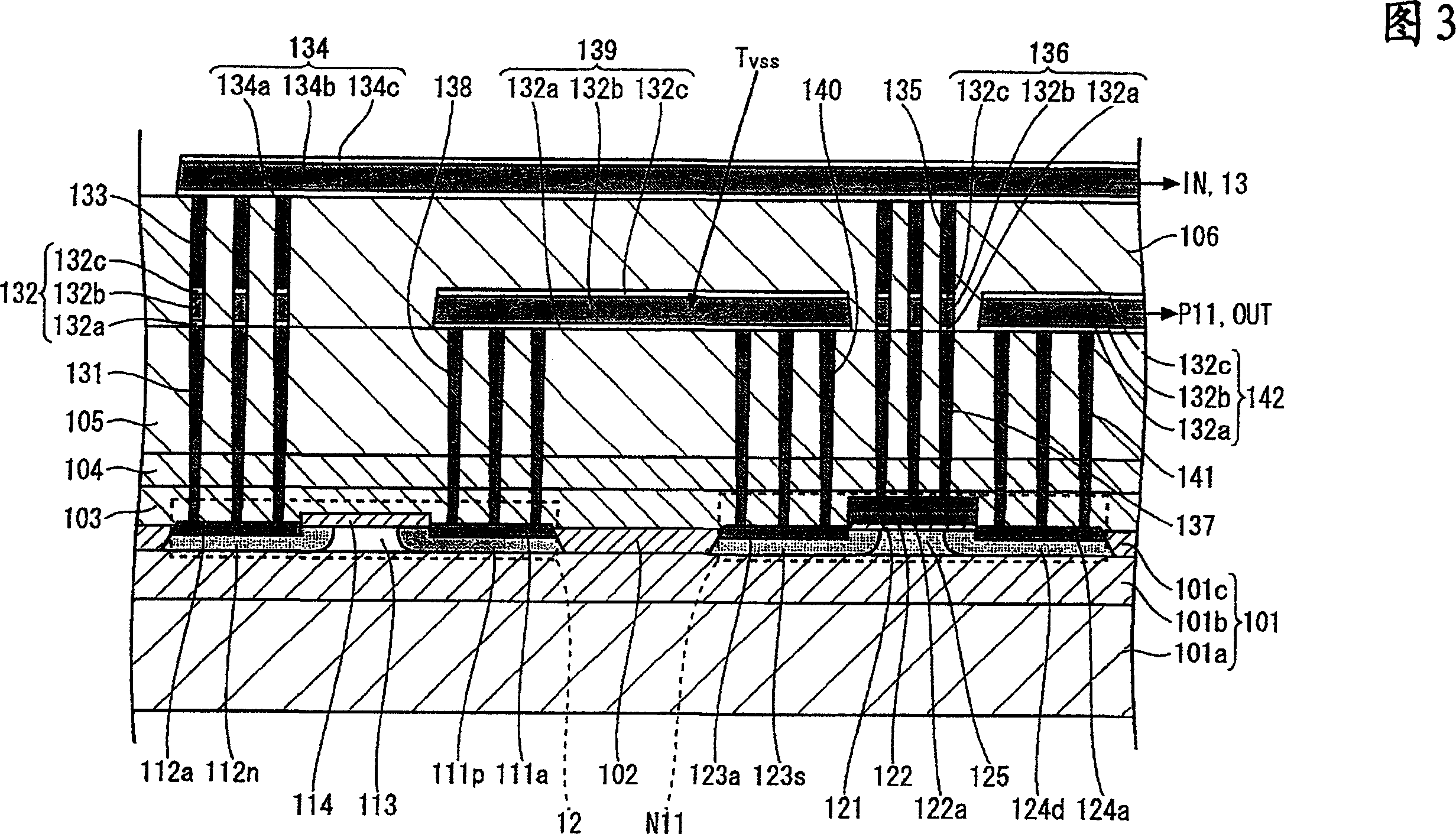

[0038] First, Embodiment 1 of the present invention will be described in detail with reference to the drawings. Furthermore, in this embodiment, the semiconductor element formed on the SOI substrate is used as an inverter as an example for description.

[0039] · Overall composition

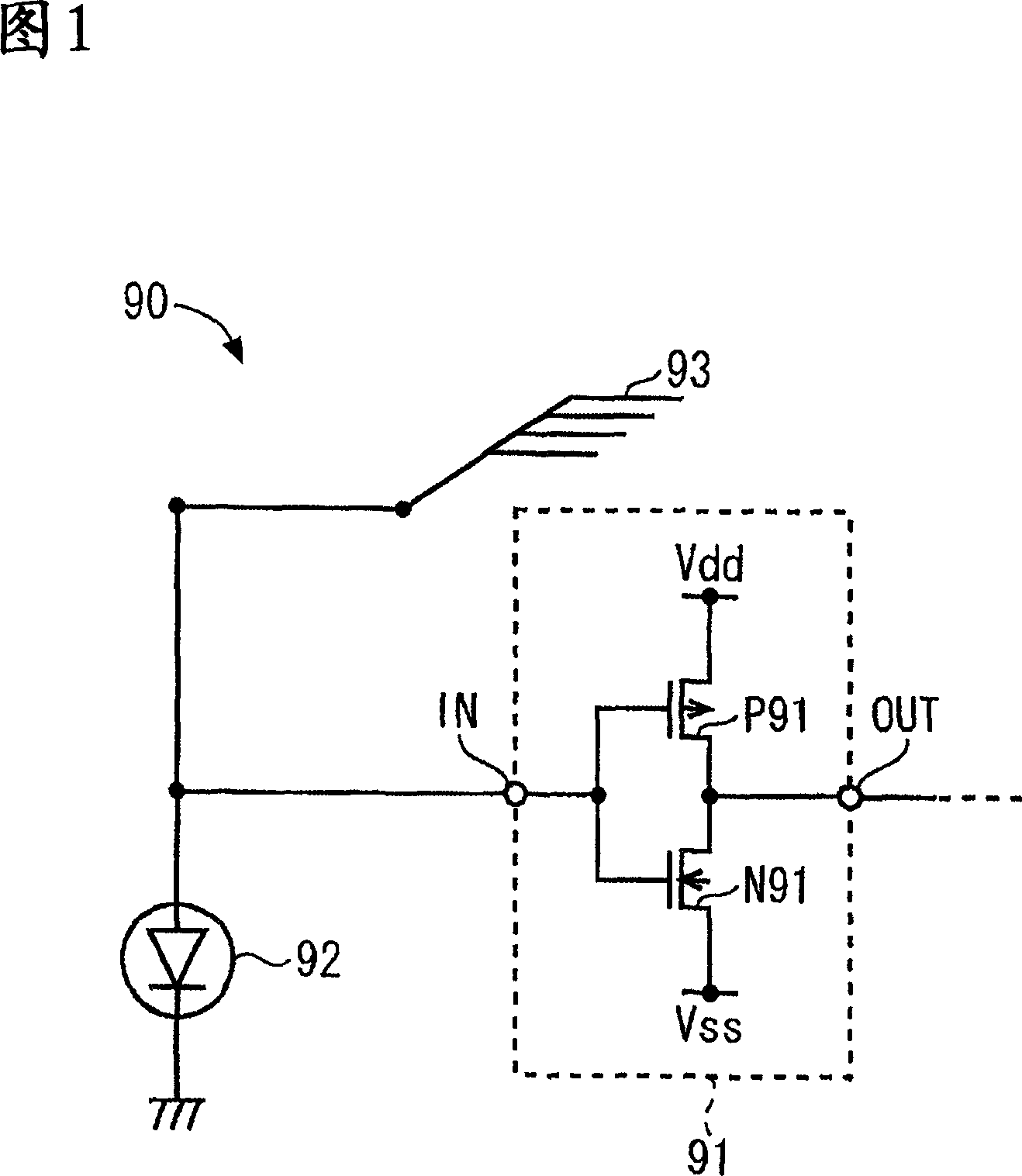

[0040]FIG. 2 is a circuit diagram showing the configuration of the semiconductor device 10 of the present embodiment. As shown in FIG. 2 , the semiconductor device 10 has a PMOS transistor P11 and an NMOS transistor N11 connected in series between a power supply line Vdd and a power supply line Vss. The drains of the PMOS transistor P11 and the NMOS transistor N11 are connected in common and connected to the output terminal OUT. The source of the PMOS transistor P11 is connected to the power supply line Vdd. The source of the NMOS transistor N11 is connected to the power supply line Vss and also connected to the Vss terminal Tvss (second terminal). The gates of the PMOS transistor P11 and the...

Embodiment 2

[0090] Next, Embodiment 2 of the present invention will be described in detail with reference to the drawings. In addition, in the following description, the same code|symbol is attached|subjected to the same structure as Example 1, and the detailed description is abbreviate|omitted. In addition, about the structure which is not specifically described, it is the same as Example 1. In addition, in this embodiment, as in the first embodiment, a semiconductor element formed on an SOI substrate is used as an example for an inverter.

[0091] · Overall composition

[0092] FIG. 10 is a circuit diagram showing the configuration of the semiconductor device 20 of this embodiment. As shown in FIG. 10 , the semiconductor device 20 has the same configuration as the semiconductor device 10 of the first embodiment (see FIG. 2 ), and has a structure in which a wiring connecting the anode of the protection diode 12 and the Vss terminal Tvss is connected to the substrate. . Note that othe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More