Housing for electronic components

A shell and semiconductor technology, applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problems of poor storage conditions of semiconductor chips, semiconductor chip position deviation, position deviation, etc., to prevent position deviation and realize compactness Size, the effect of reducing the total space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The present invention will be described in detail by way of examples with reference to the accompanying drawings.

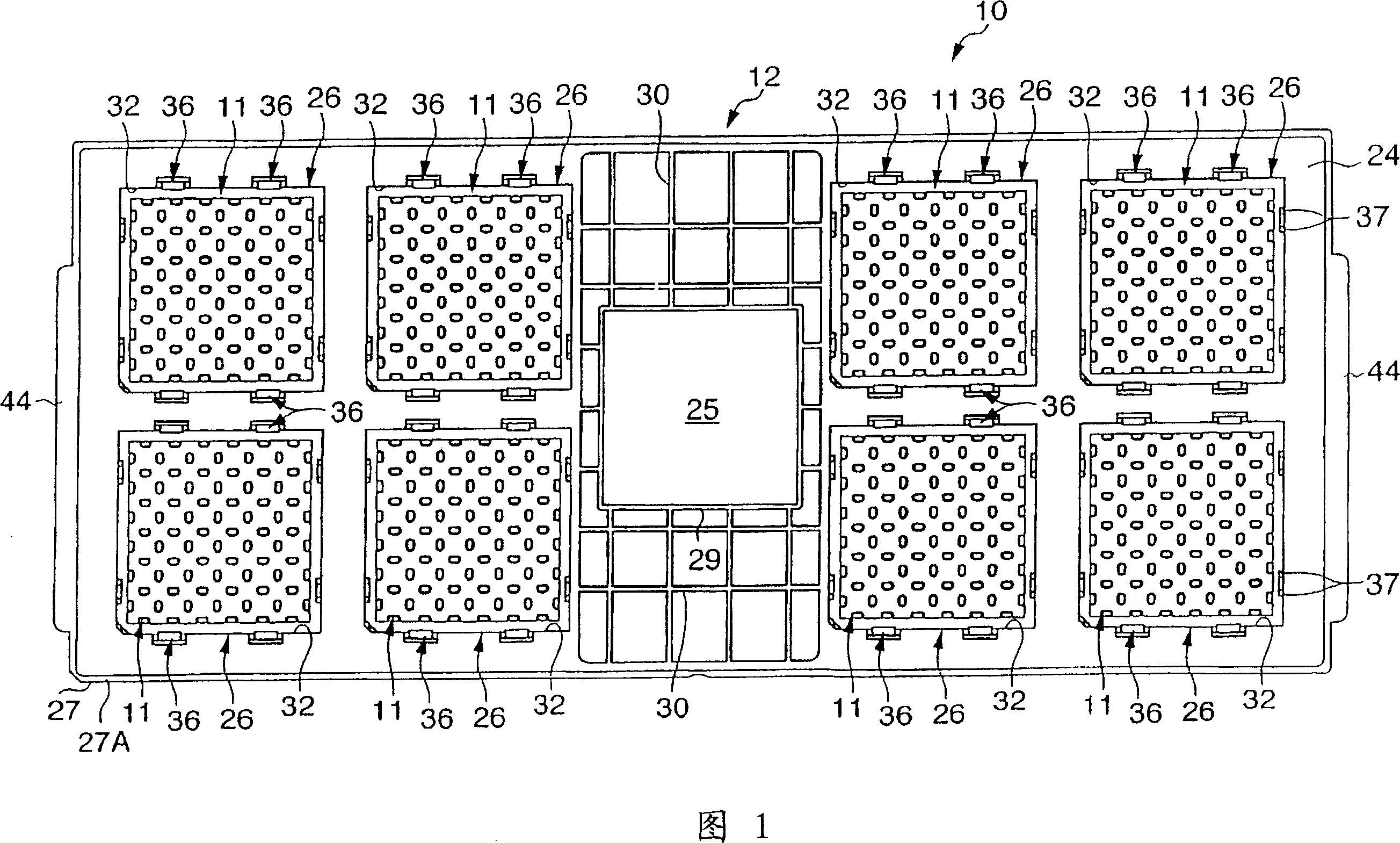

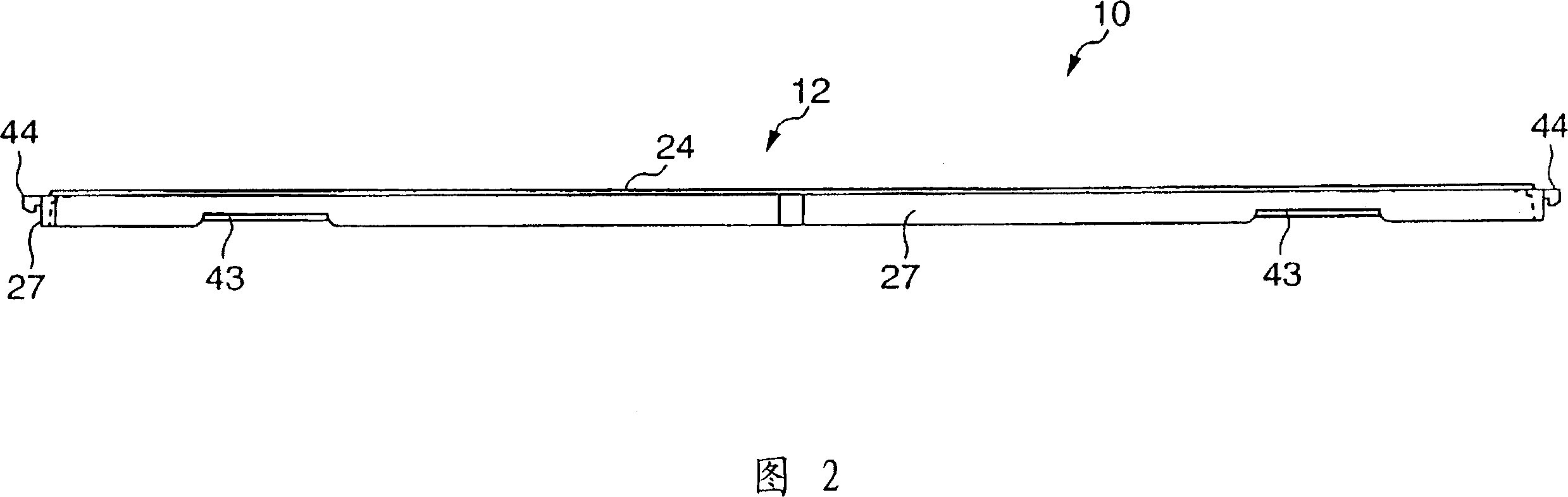

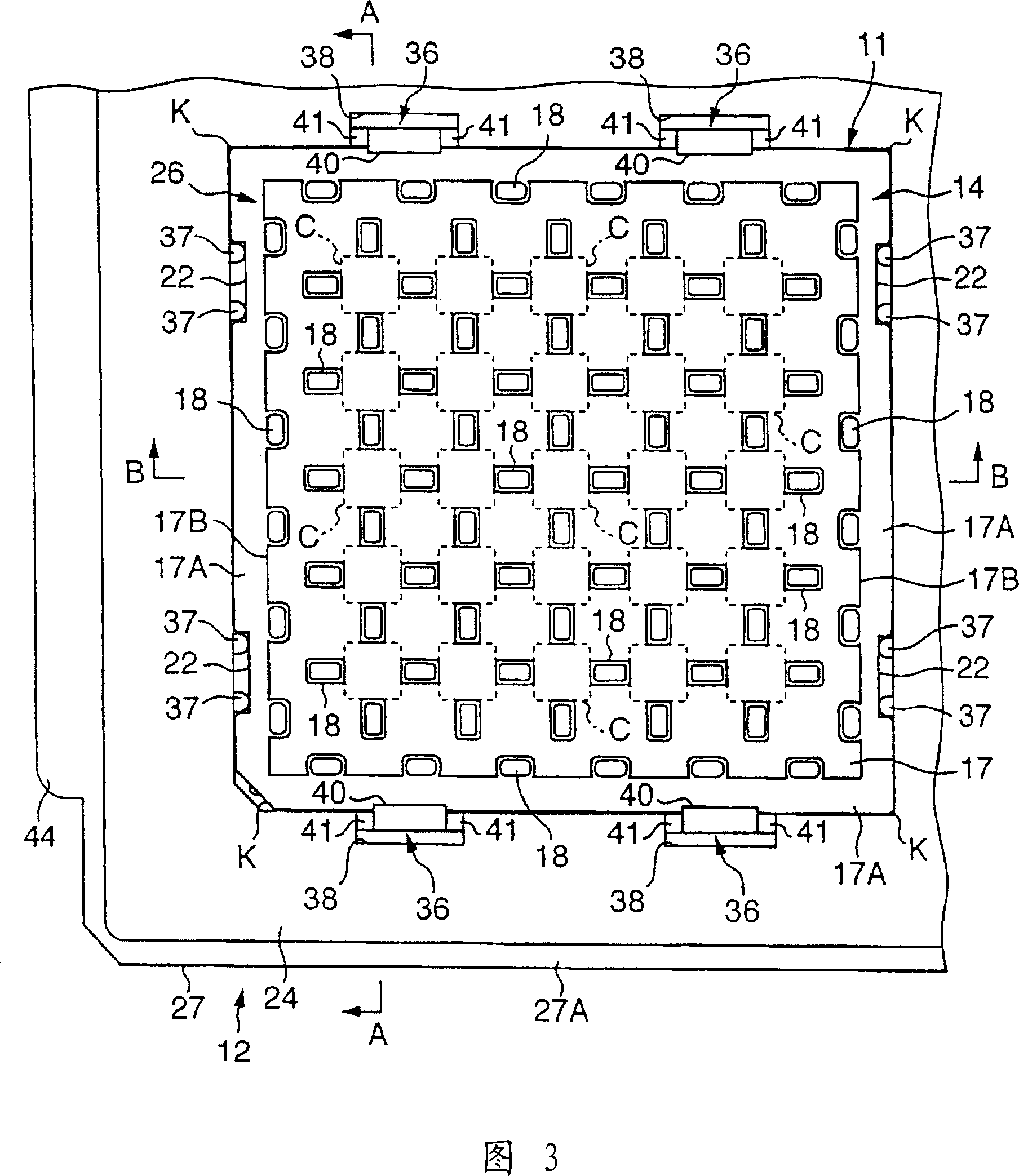

[0030] 1 is a plan view showing a housing including a chip tray and a storage tray according to a preferred embodiment of the present invention; FIG. 2 is a front view of the housing; FIG. 3 is an enlarged view showing basic components of a chip tray; 4C is an enlarged perspective view showing the main part of the casing.

[0031] The housing 10 includes a plurality of chip trays 11 each storing a plurality of chips C and a storage tray 12 storing the chip trays 11 . The present embodiment does not particularly limit the type of chip C; however, the drawings show that the chip C is packaged in a surface mount chip package, such as a BGA (Ball Grid Array) package and a CSP (Chip Scale Package), wherein each chip C Has a two-dimensional square size in which a plurality of terminals are arranged, for example, along one side thereof.

[0032] As shown in FIG...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More