Nanoscale patterning for the formation of extensive wires

a technology of nanoscale and extensive wires, applied in the direction of photomechanical equipment, instruments, and semiconductor/solid-state device details, can solve the problems of limiting the advancement of lithographically defined patterning, affecting the placement of free-standing wires, and affecting the effect of lithographic accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

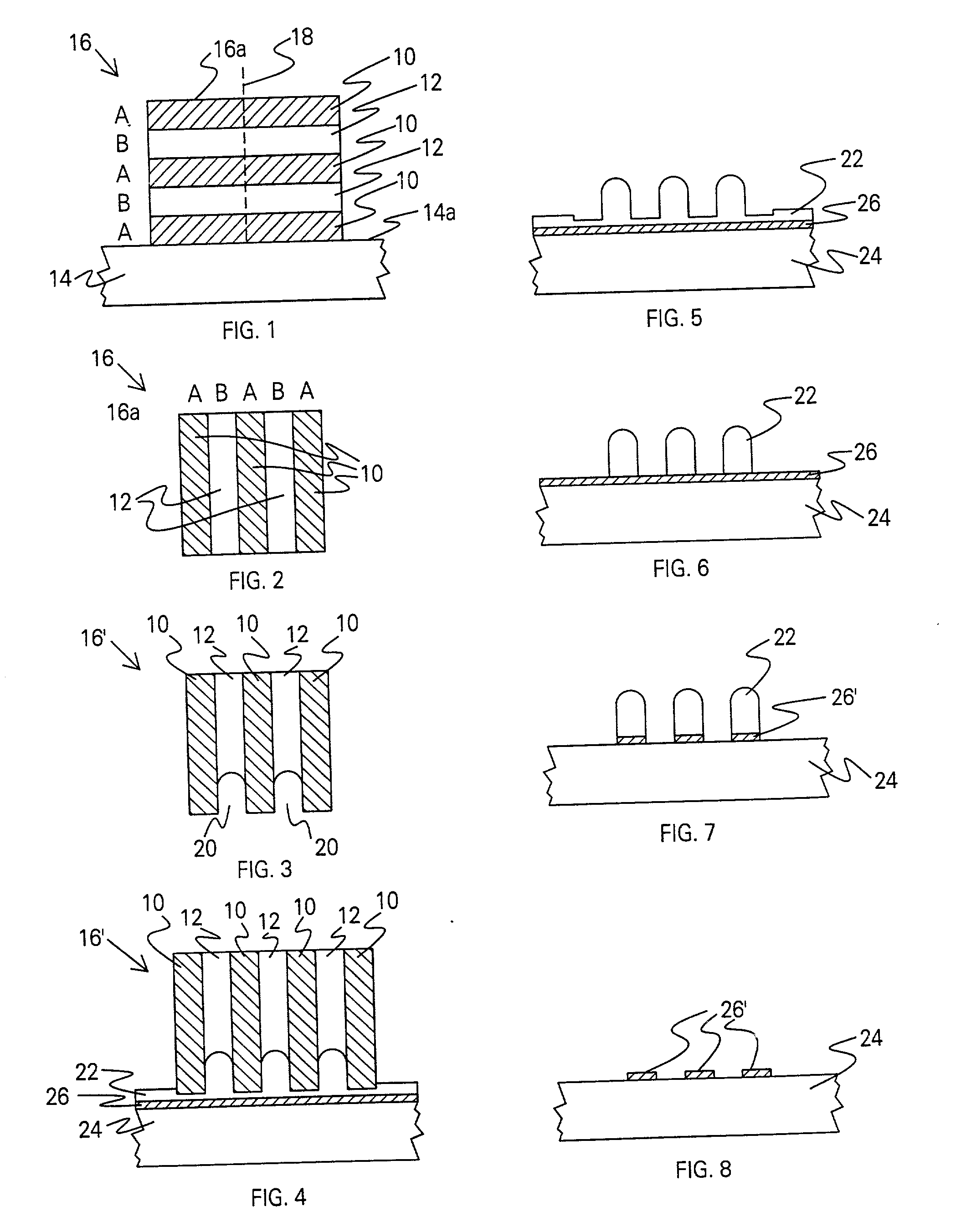

[0024] Nanoscale strips for device applications are fabricated by depositing composite thin films with different materials A and B, as illustrated in FIG. 1. Essentially, as described in greater detail below, a plurality of alternating layers of A material 10 and B material 12 are deposited on a major surface 14a of a substrate 14 to form a stack 16, also having a major surface 16a, parallel to the major surface of the substrate. Preferably, the material having the least lattice mis-match with the substrate 14 is deposited in order to keep a smooth growth surface and flat, sharp interfaces between materials 10 and 12.

[0025] The layers 10, 12 are then cleaved along a line 18 normal to the major surface 16a of the stack 16 to expose the cross-section, as shown in FIG. 2. Cleaving is performed by any conventional technique useful in cleaving a plurality of alternating layers of dissimilar materials. Such techniques are well-known in the art for the materials used for layers A and B, wh...

PUM

| Property | Measurement | Unit |

|---|---|---|

| depth | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More