Enhanced die-up ball grid array and method for making the same

a grid array and die-up ball technology, applied in semiconductor devices, semiconductor/solid-state device details, electrical devices, etc., can solve the problems of reducing the thermal connection between the ic die and the edge of the stiffener, reducing the reliability requirements of die sizes larger than 9 mm, and high thermal stress of conventional bga packages

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] Overview

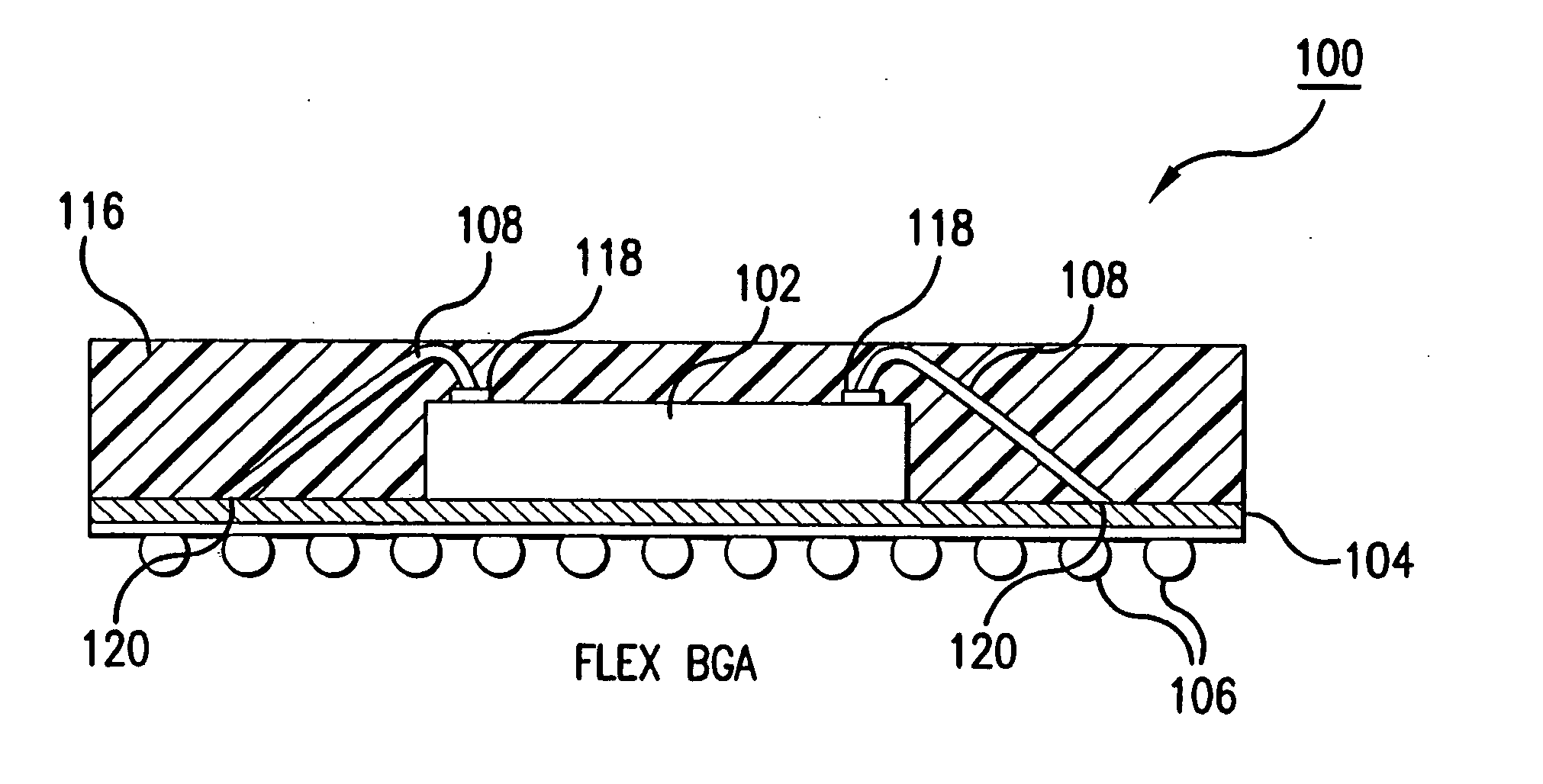

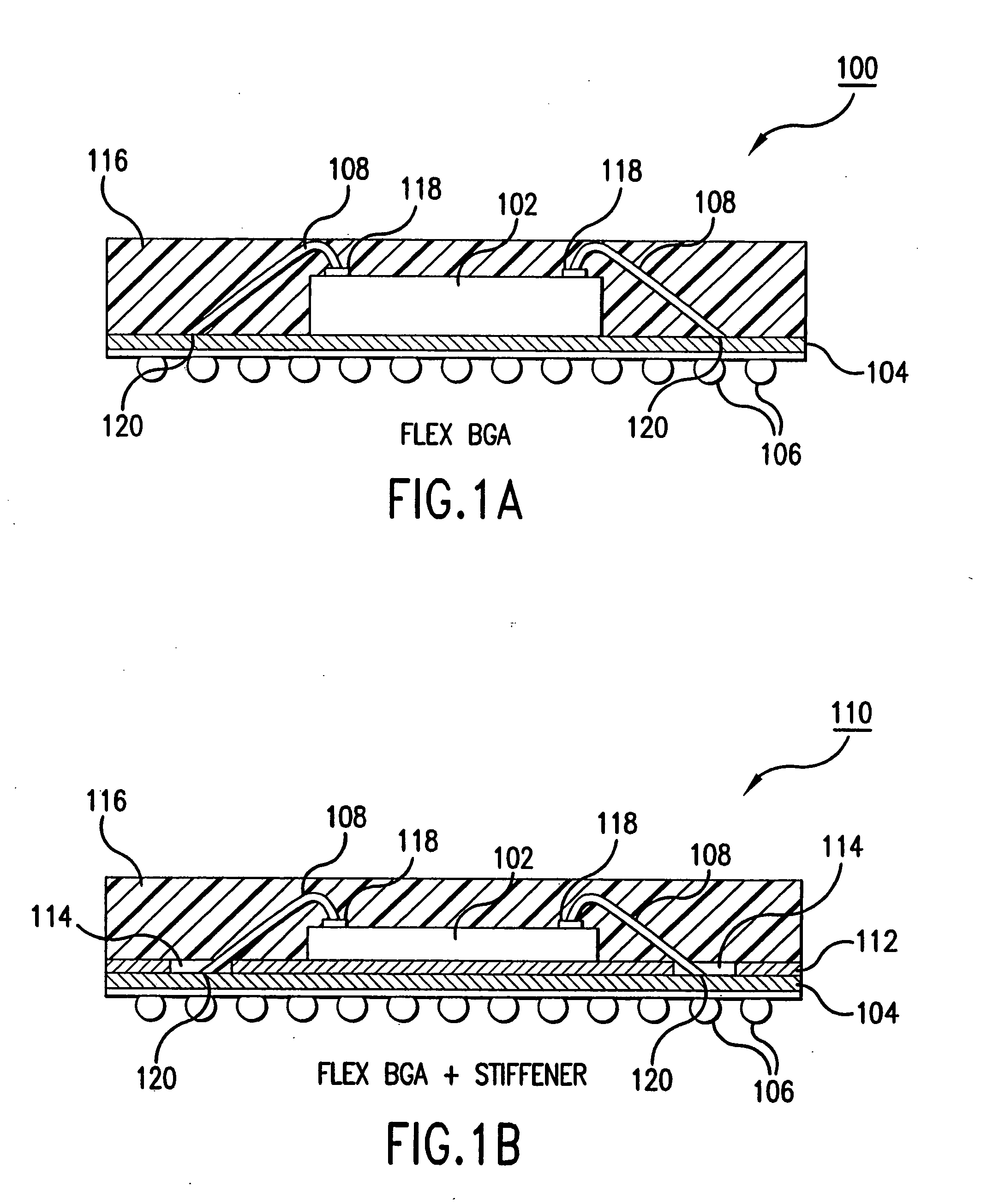

[0050] The present invention is directed to a method and system for improving the mechanical, thermal, and electrical performance of BGA packages. The present invention is applicable to all types of BGA substrates, including ceramic, plastic, and tape (flex) BGA packages. Furthermore the present invention is applicable to die-up (cavity-up) and die-down (cavity-down) orientations.

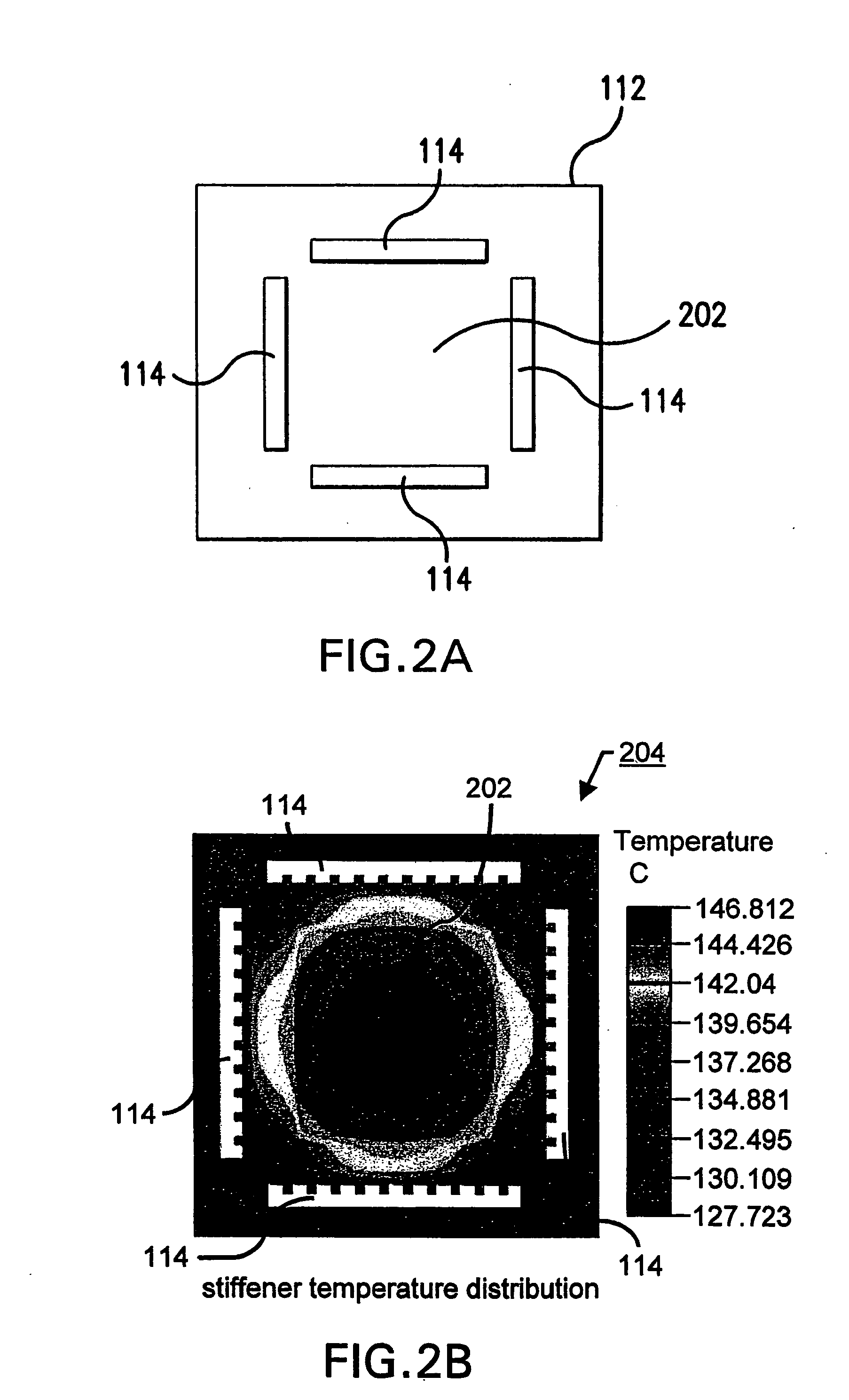

[0051] Numerous embodiments of the present invention are presented herein. In a first embodiment, BGA package thermal stress at the IC die / stiffener interface is released or altered with the introduction of a heat spreader on the top surface of the IC die, enabling large size dies with high input and output (I / O) counts to be packaged using BGA technology. In a second embodiment, BGA package thermal resistance and the length of the current return path are reduced by introducing thermal / ground balls underneath or within close proximity of the IC die. In a third embodiment, the package therma...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More