Device and method for protecting gate terminal and lead

a technology of gate terminals and lead, applied in the direction of basic electric elements, electrical equipment, semiconductor devices, etc., can solve problems such as failure of display panels, and achieve the effect of not increasing the tft fabrication cycle tim

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] Some sample embodiments of the present invention will now be described in greater detail. Nevertheless, it should be recognized that the present invention can be practiced in a wide range of other embodiments besides those explicitly described, and the scope of the present invention is expressly not limited except as specified in the accompanying claims.

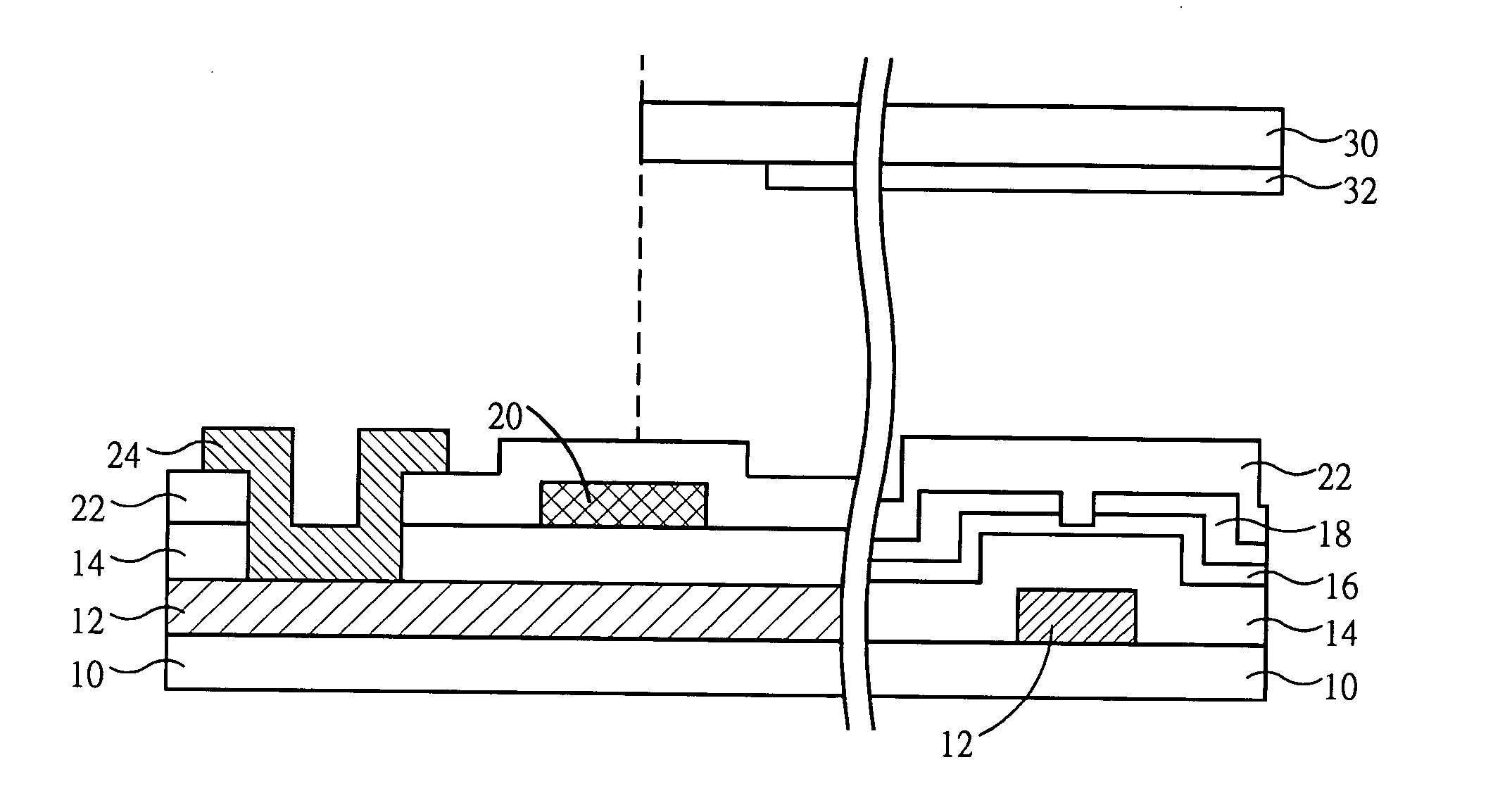

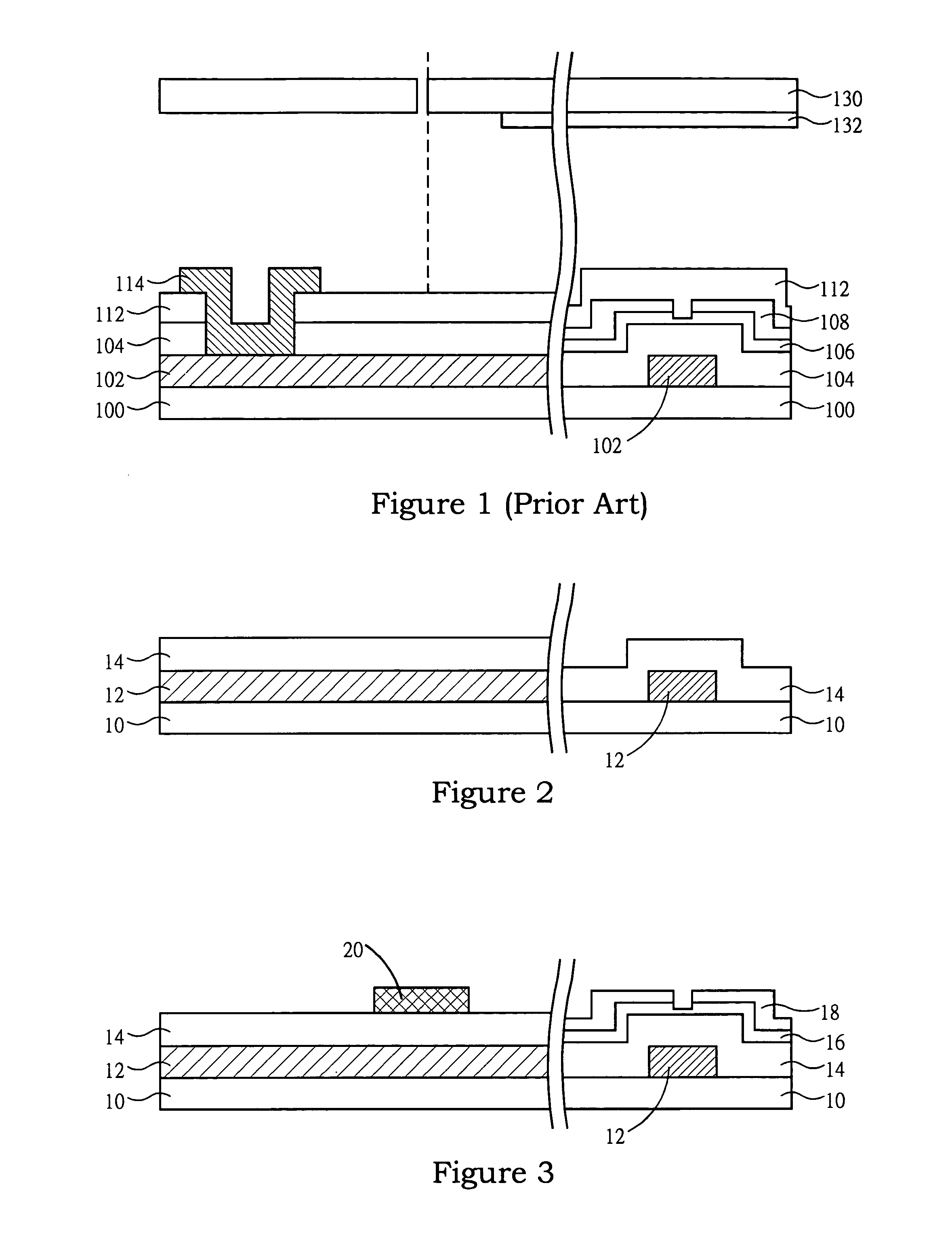

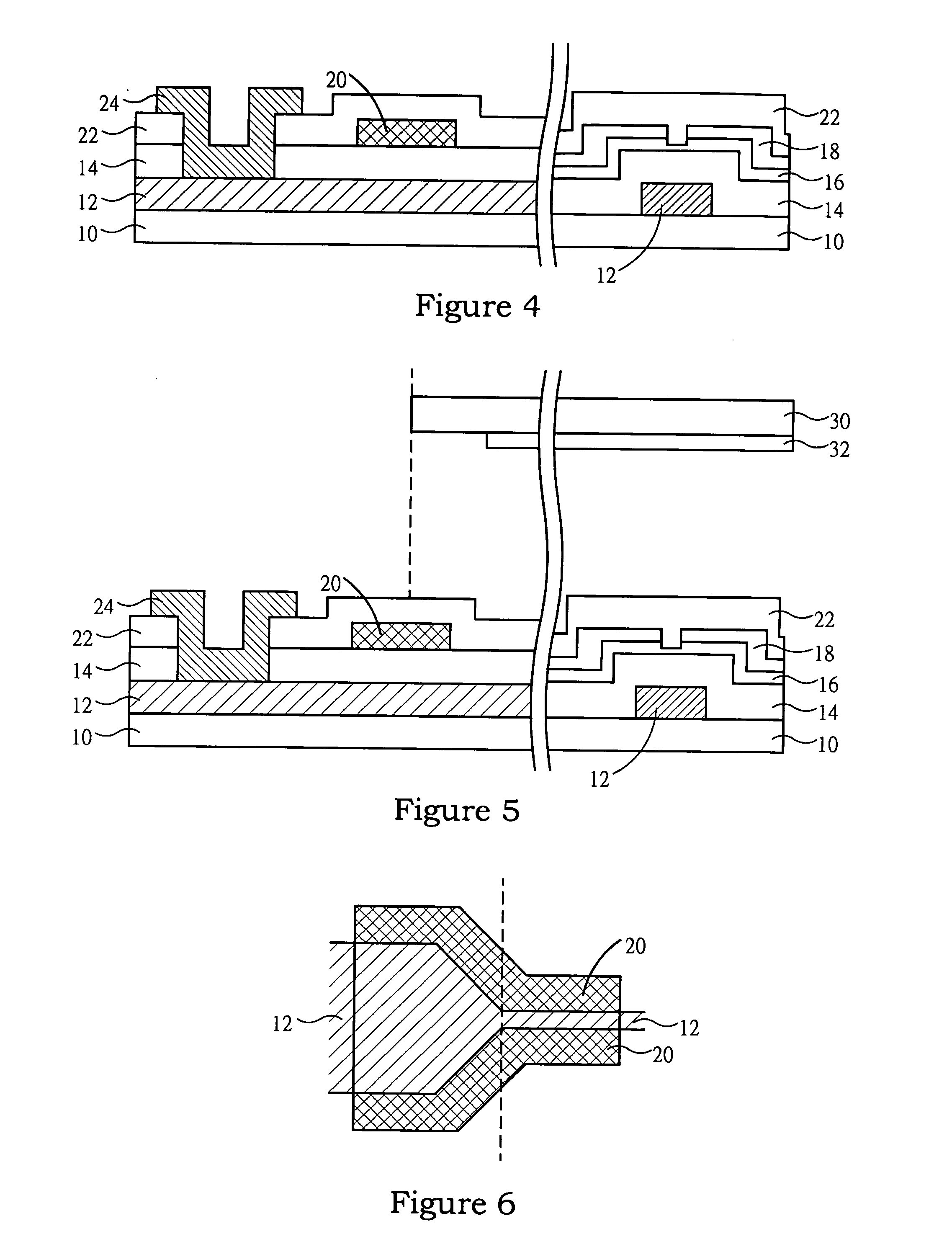

[0021] This invention provides a device for protecting a gate terminal and lead at stage of scribing and spalling a LCD panel, wherein the LCD panel comprises a first substrate with thin film transistor array thereon and a second substrate thereon within color filter opposite to the thin film transistor array. The device comprises a resist region covering the gate terminal and lead of gate electrode line and between a passivation layer and a gate insulating layer, and located at a scribing line on margin of the second substrate of the panel, thereby the resist region can protect the passivation layer and the gate insulating l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More