Patents

Literature

102results about How to "Reduce equipment capacity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

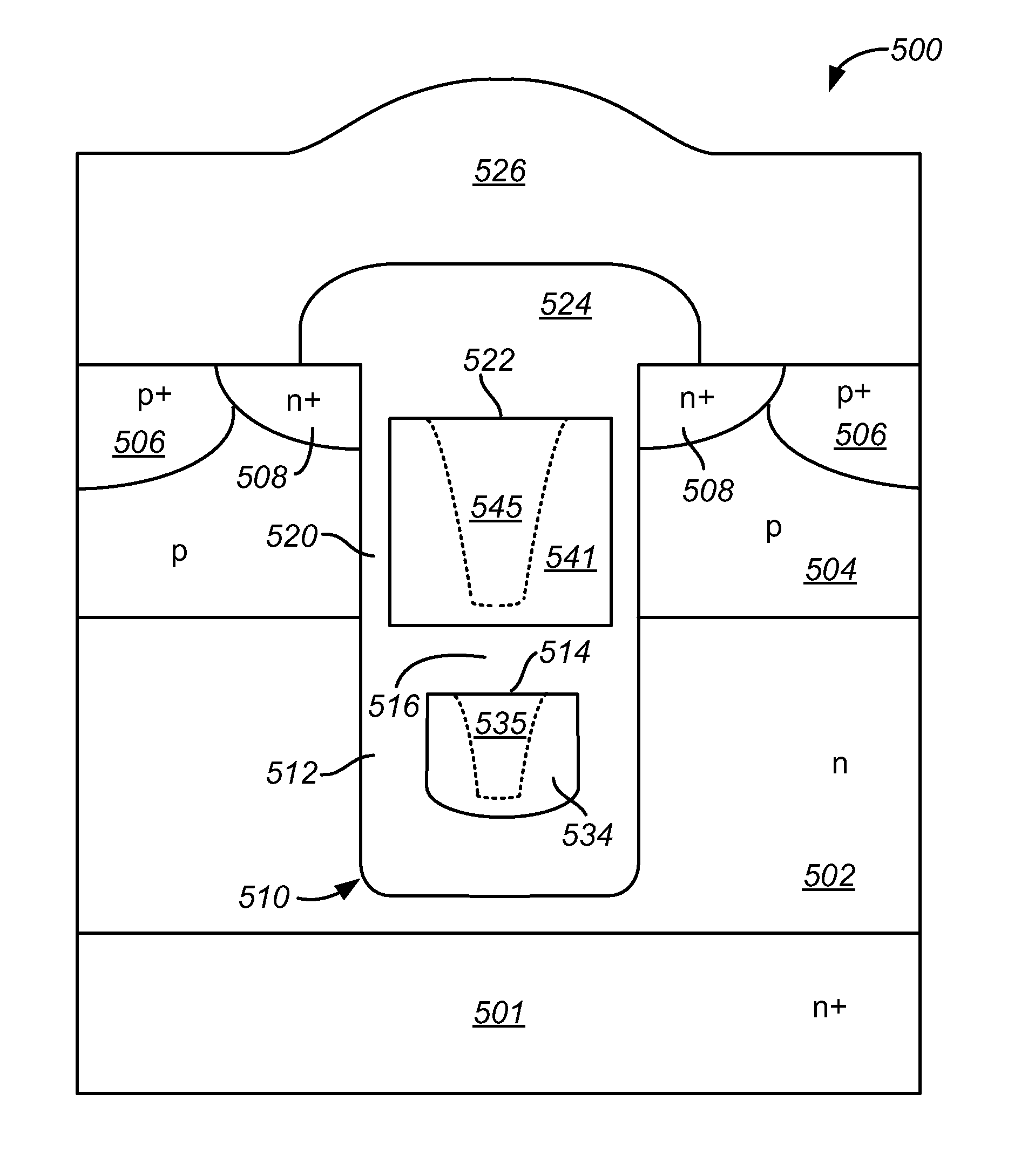

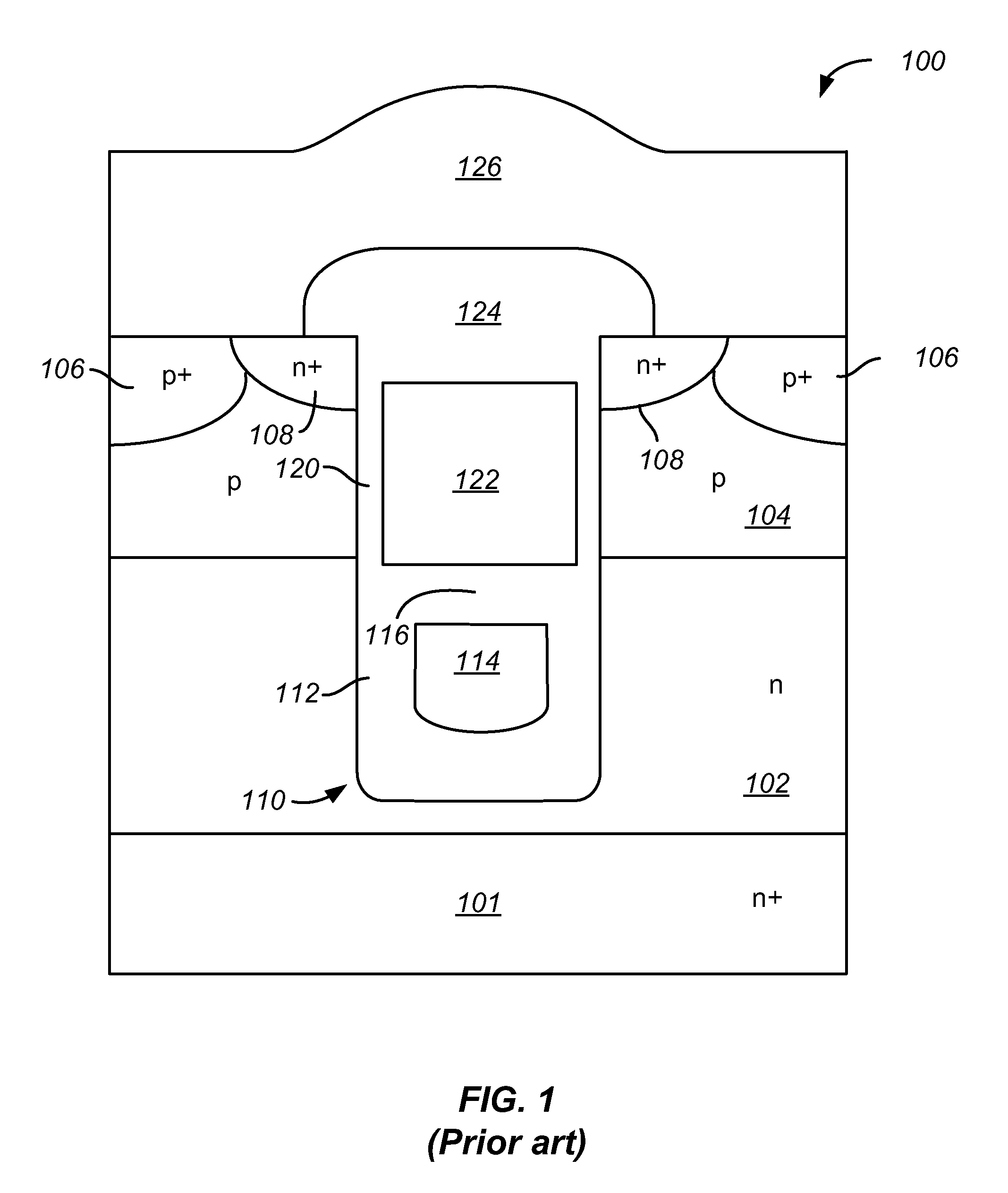

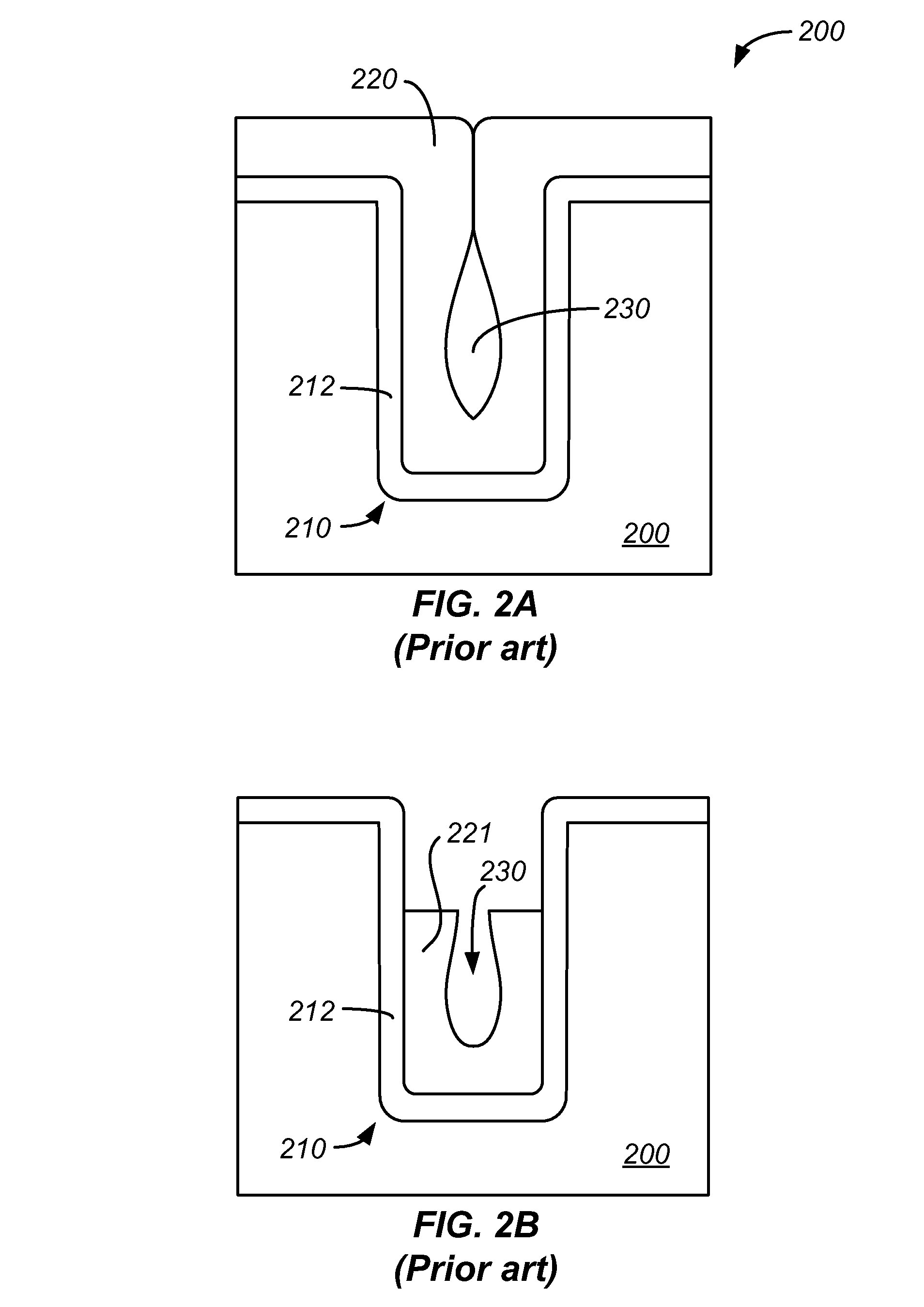

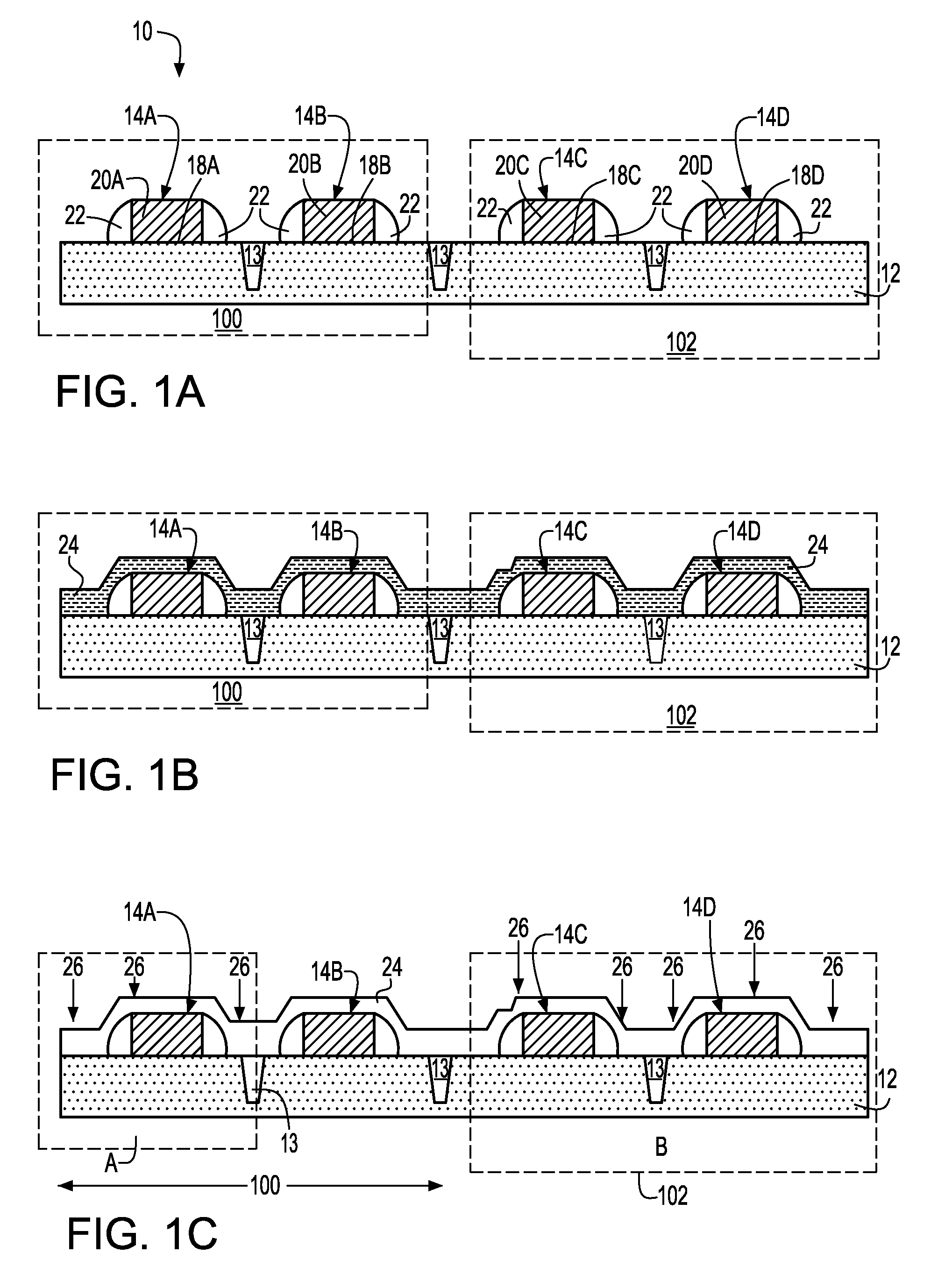

High aspect ratio trench structures with void-free fill material

ActiveUS20100044785A1Improve the immunitySpeed maximizationSemiconductor/solid-state device manufacturingSemiconductor devicesFilling materialsBody region

A field effect transistor (FET) includes a trench extending into a semiconductor region. A conductive electrode is disposed in the trench, and the conductive electrode is insulated from the semiconductor region by a dielectric layer. The conductive electrode includes a conductive liner lining the dielectric layer along opposite sidewalls of the trench. The conductive liner has tapered edges such that a thickness of the conductive liner gradually increases from a top surface of the conductive electrode to a point in lower half of the conductive electrode. The conductive electrode further includes a conductive fill material sandwiched by the conductive liner. The FET further includes a drift region of a first conductivity type in the semiconductor region, and a body region of a second conductivity type extending over the drift region. Source regions of the first conductivity type extend in the body region adjacent the trench.

Owner:SEMICON COMPONENTS IND LLC

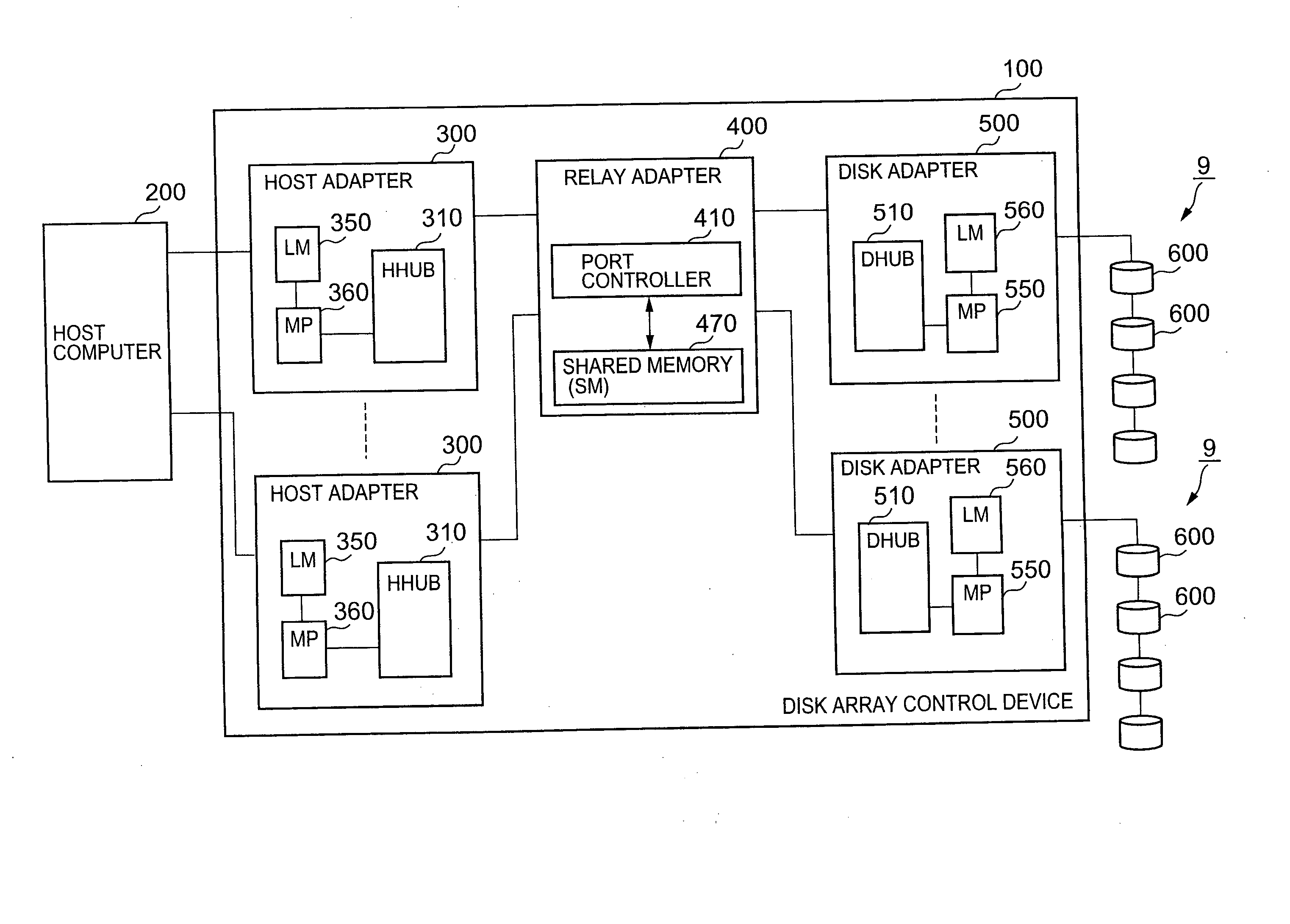

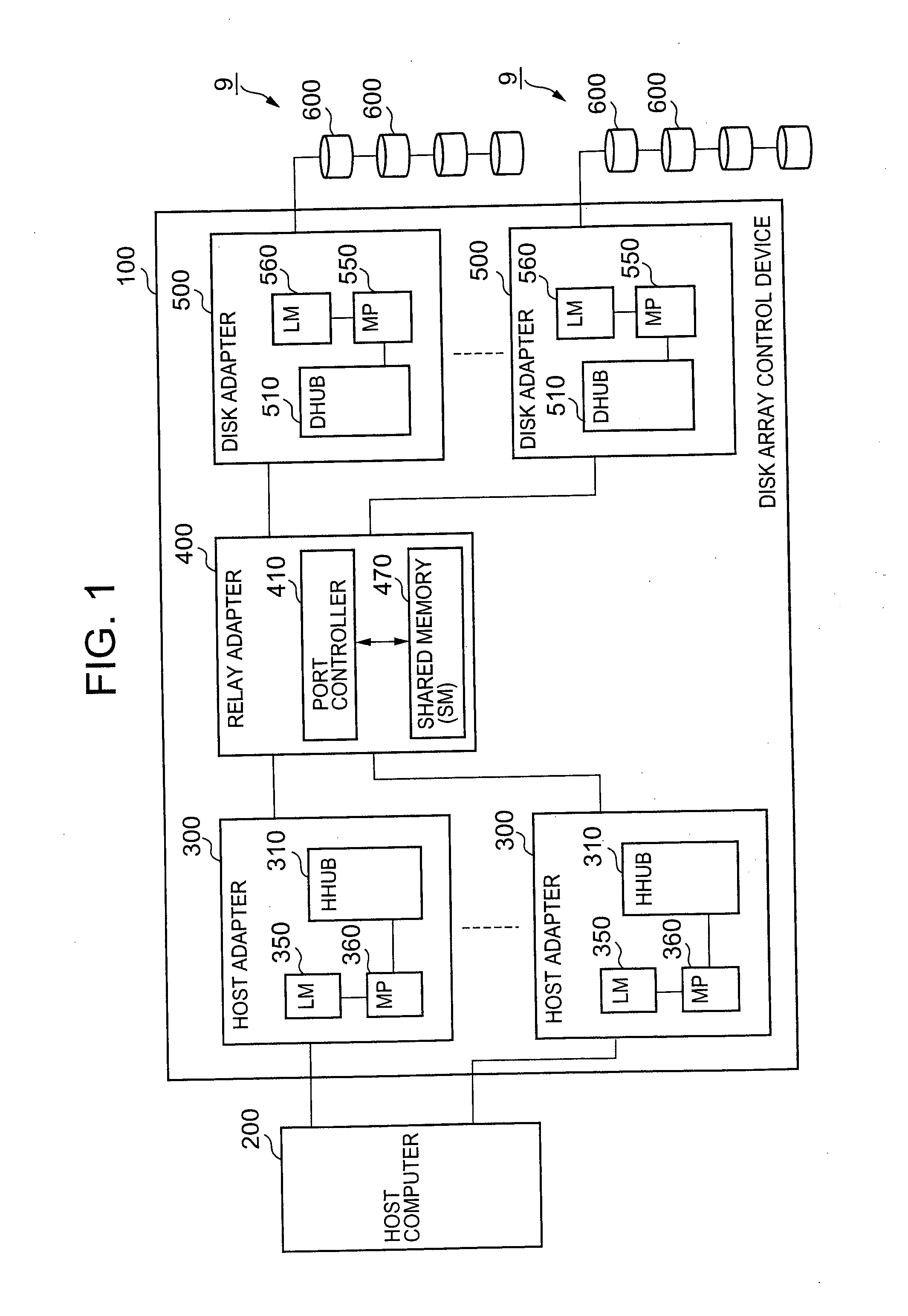

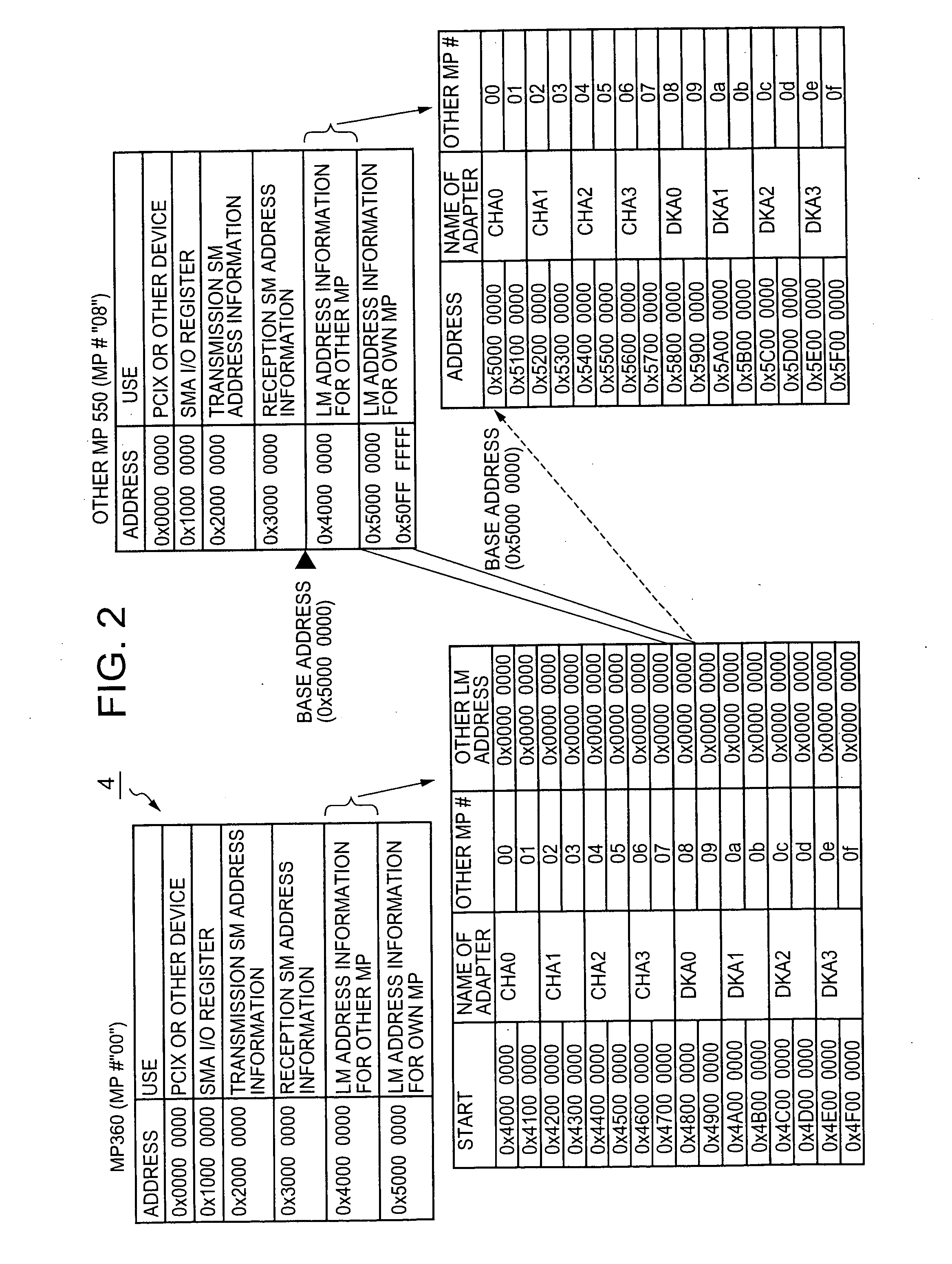

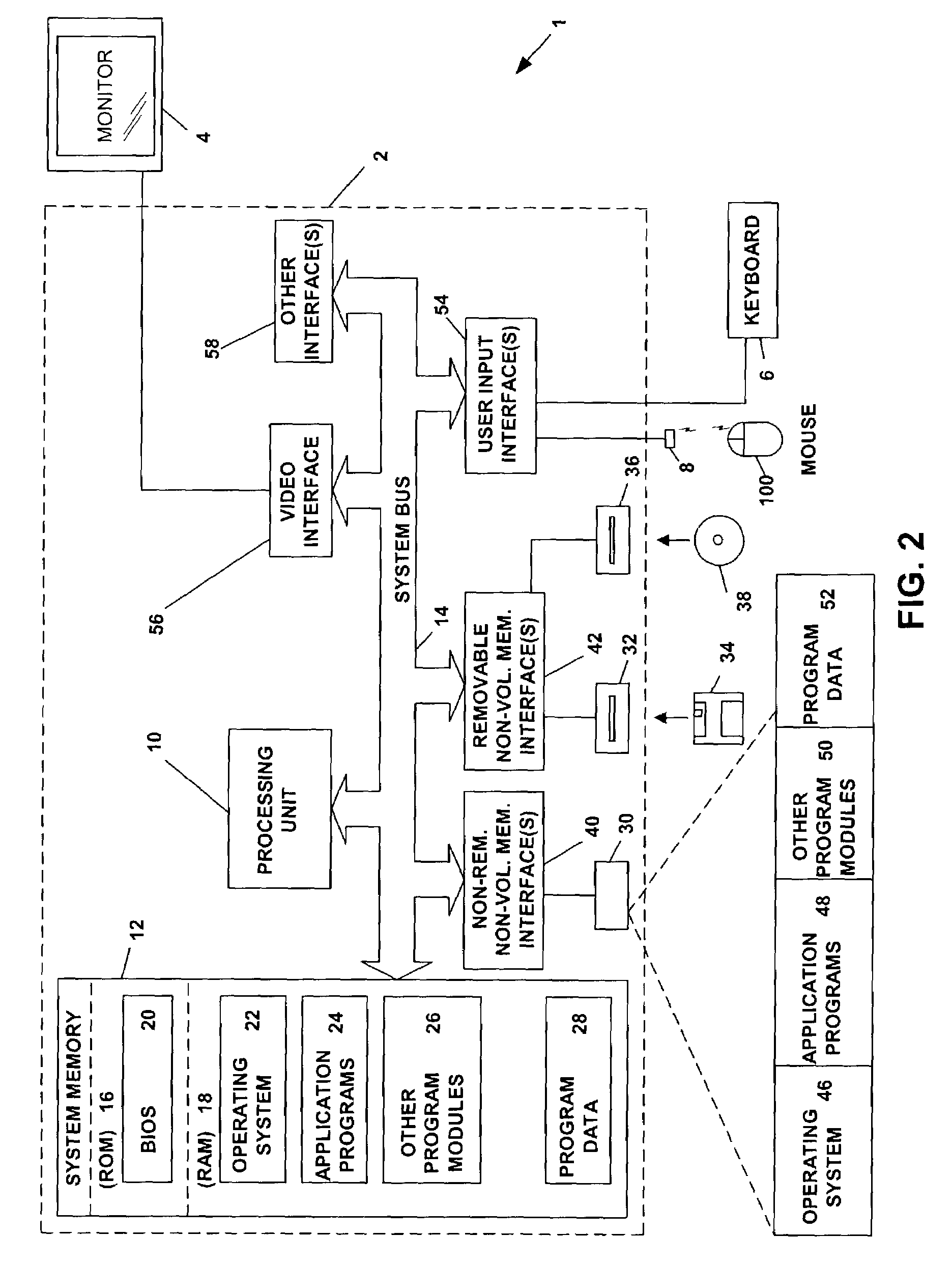

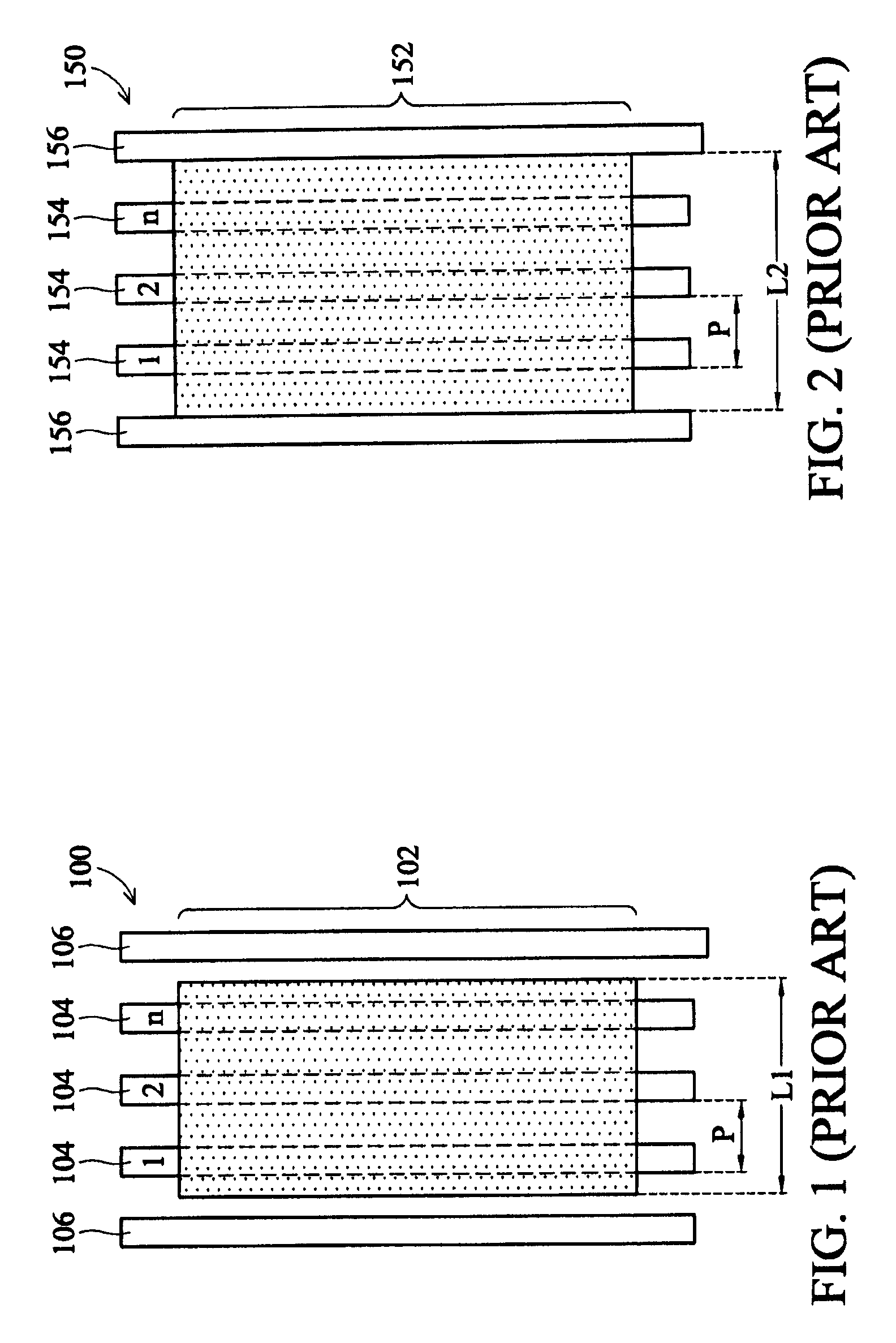

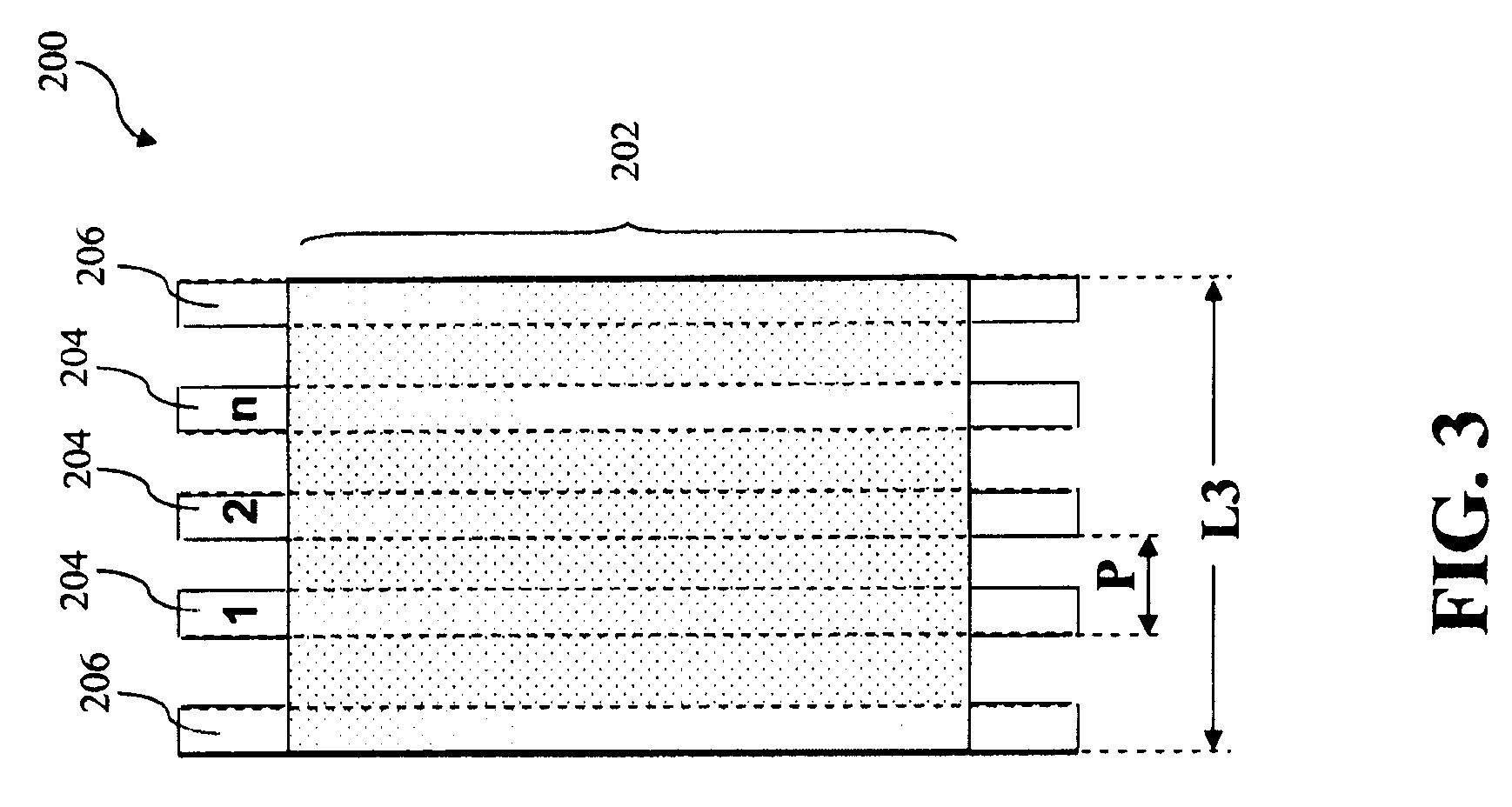

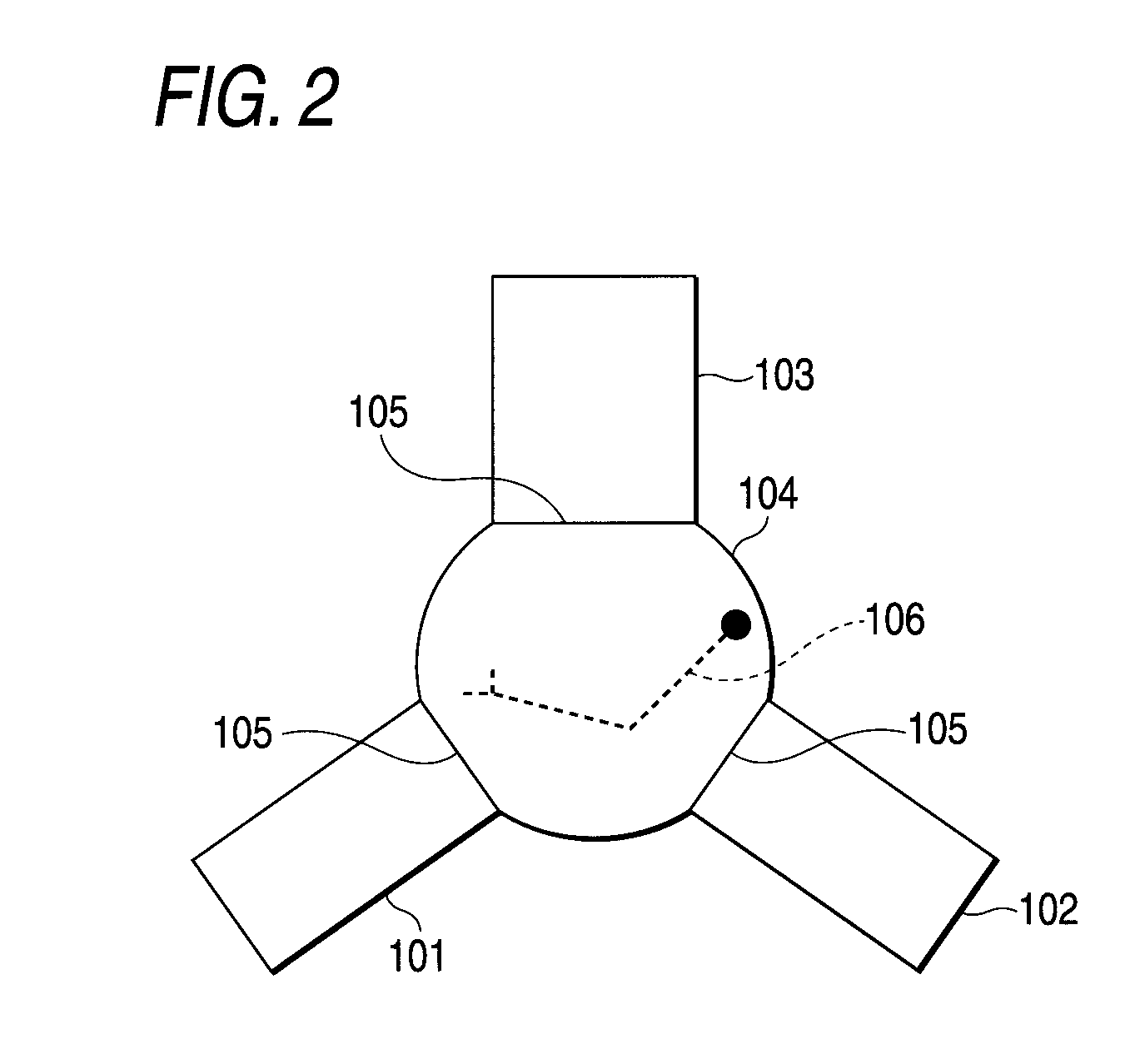

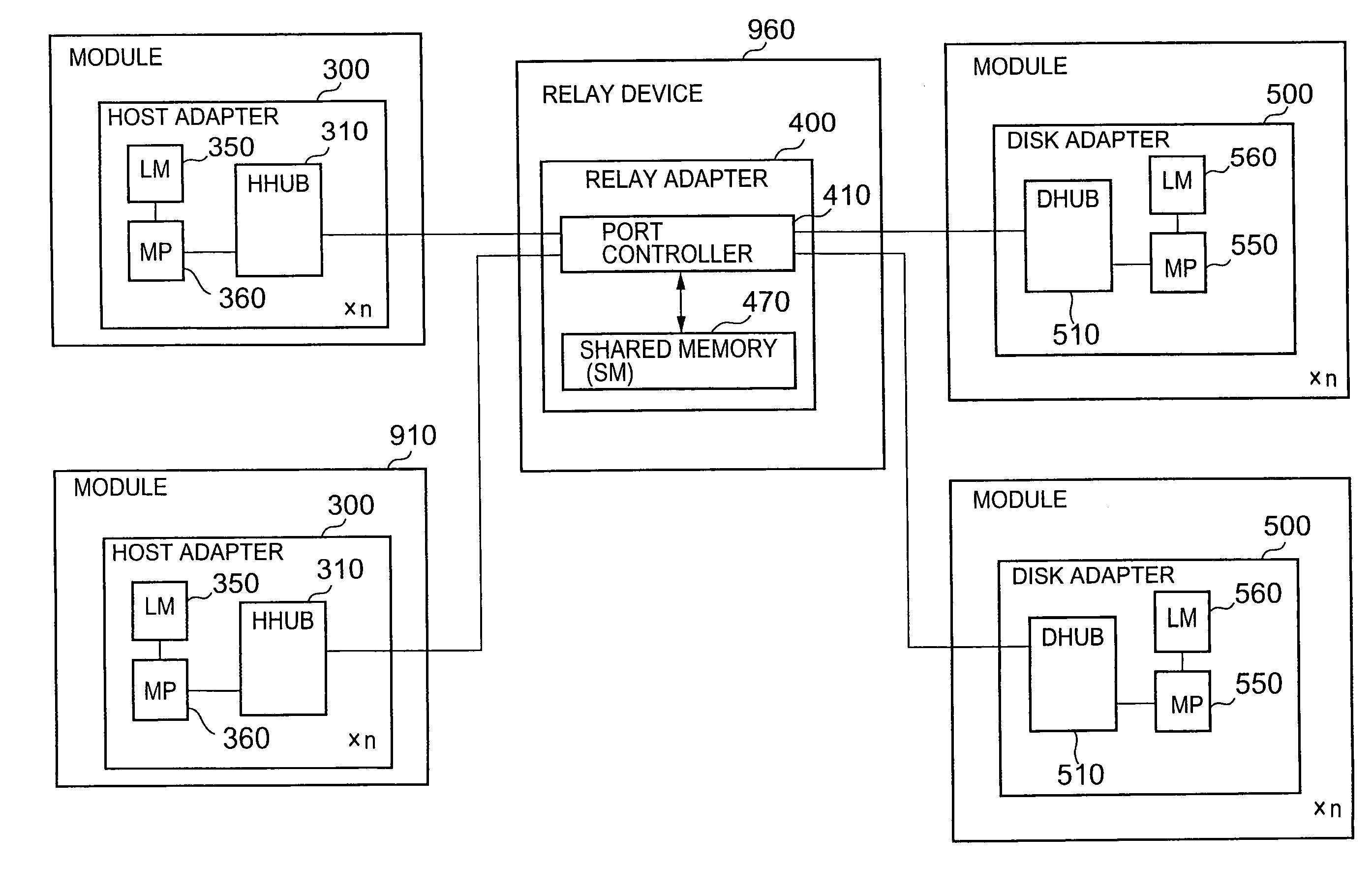

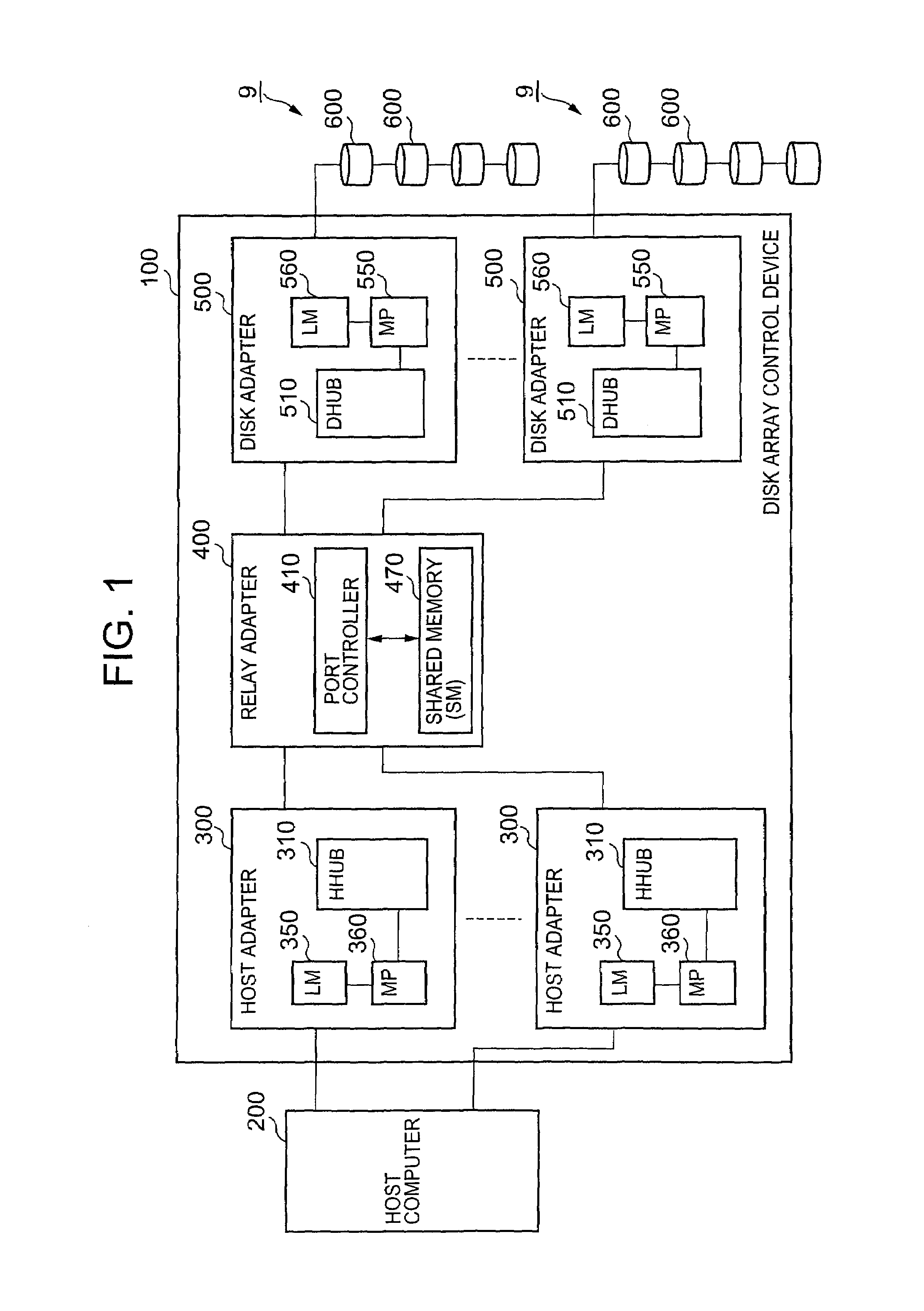

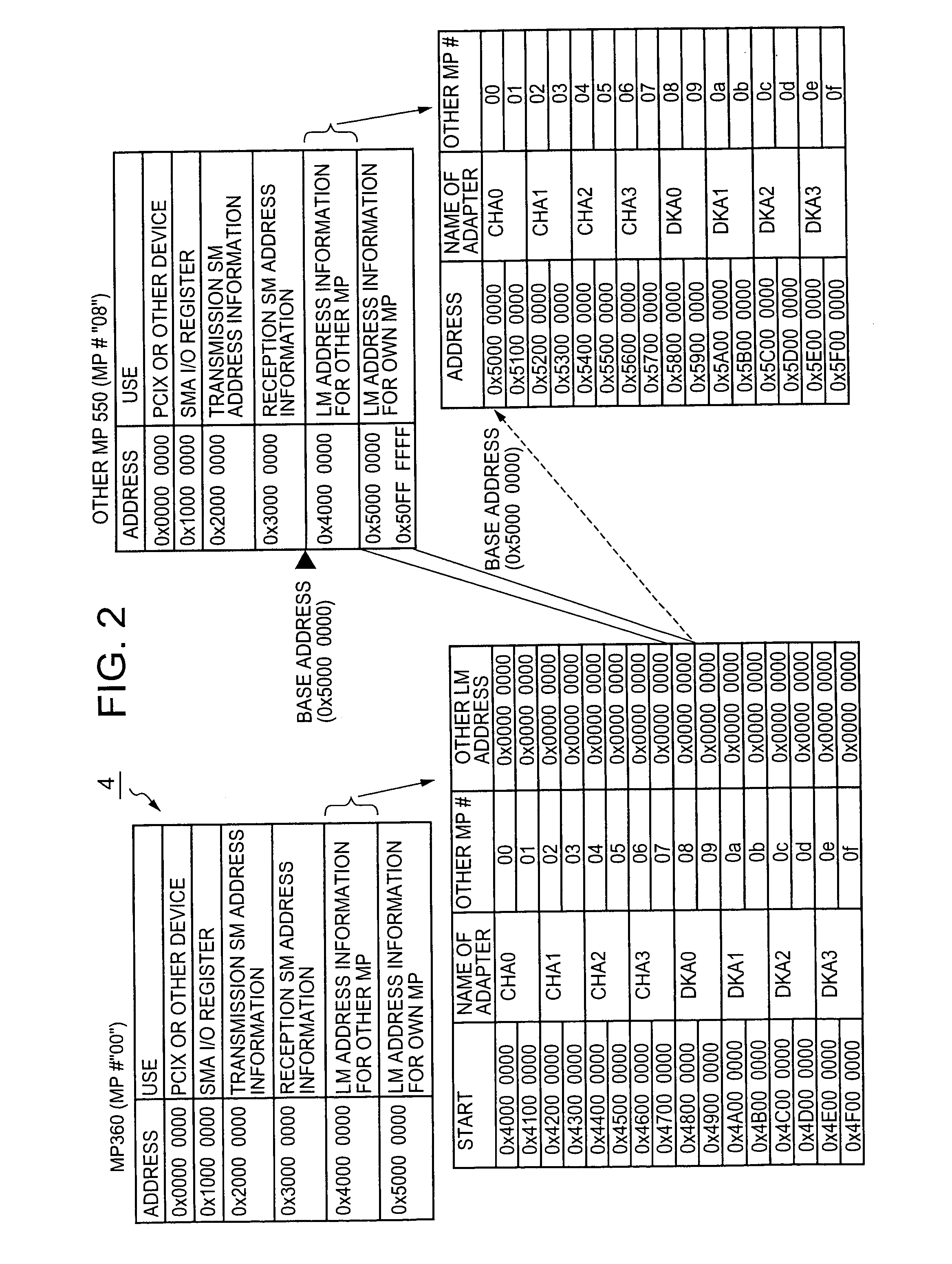

Device and method for performing information processing using plurality of processors

InactiveUS20050120173A1Increase the number ofReduce equipment capacityInput/output to record carriersMemory adressing/allocation/relocationLocal memoriesAddress mapping

The present invention makes it possible to transfer information between processors by a method that places little burden on the reception side processors. The information processing device is a device that processes information using a plurality of processors, comprising one or more first processors that have one or a plurality of local memories, and one or more second processors that write write information directly into the local memory that the target first processor has. The second processors store address maps in which local memory addresses for the first processors are recorded; these second processors acquire local memory addresses from these address maps, and write write information into the acquired local memory addresses.

Owner:HITACHI LTD

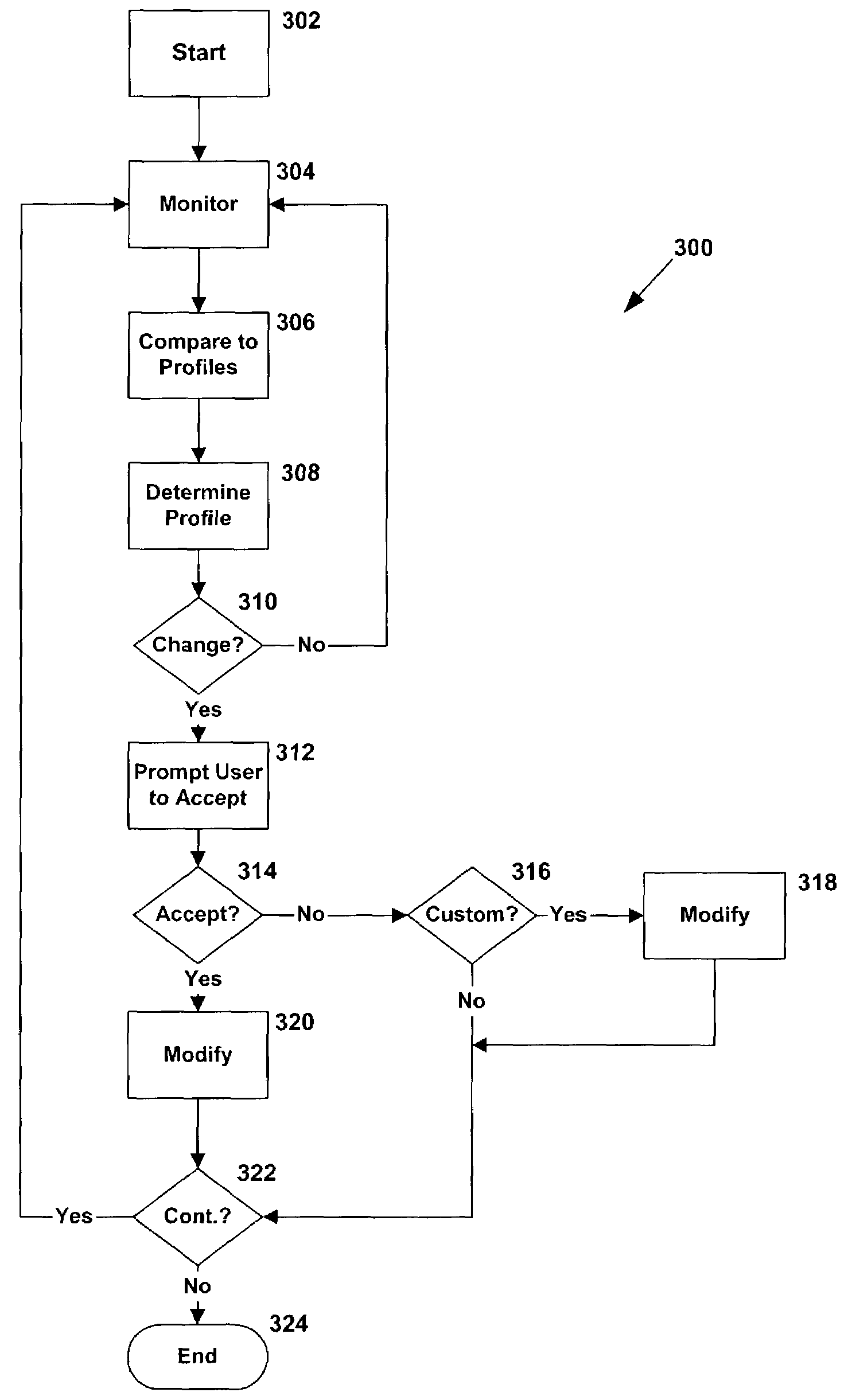

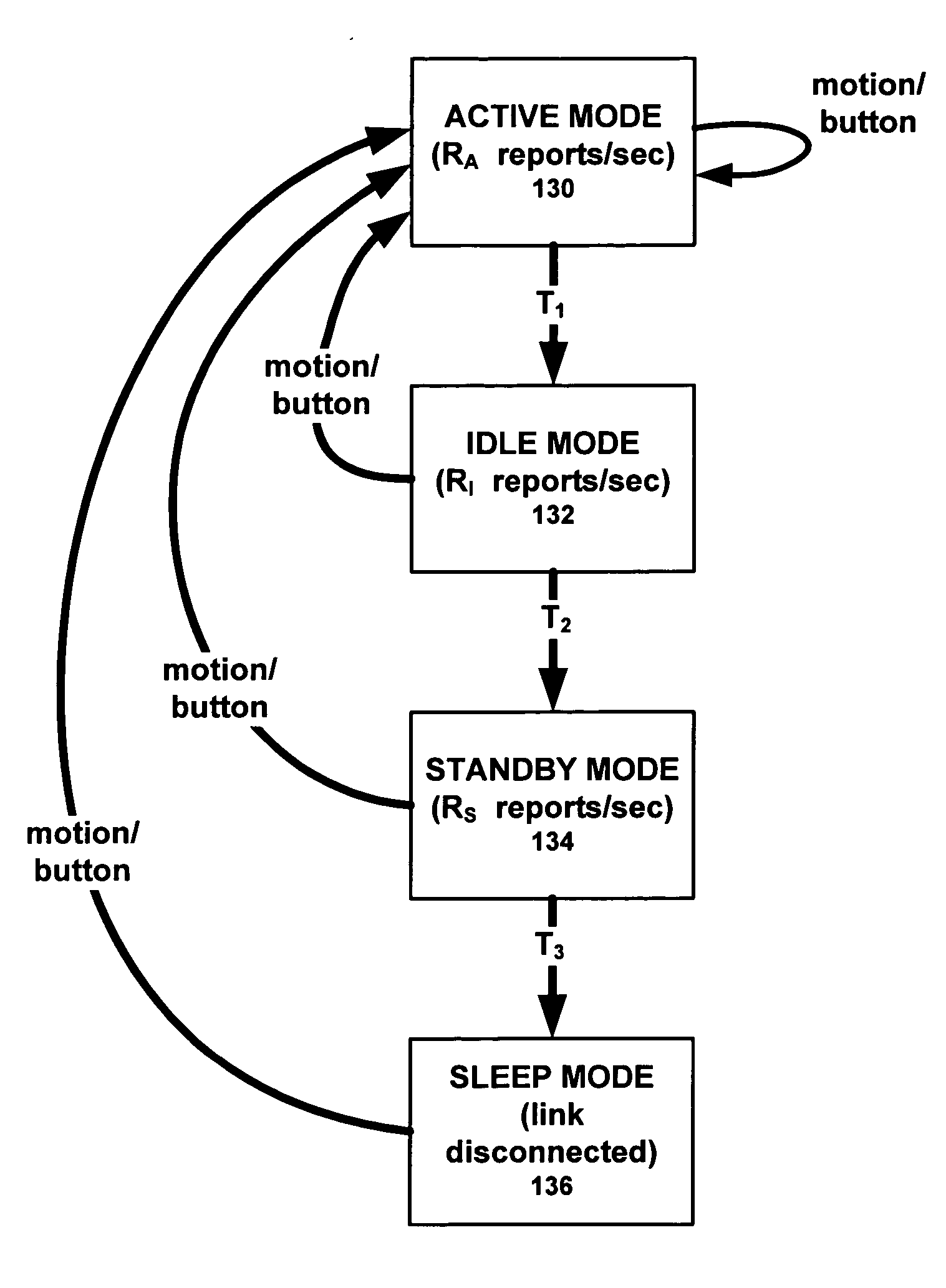

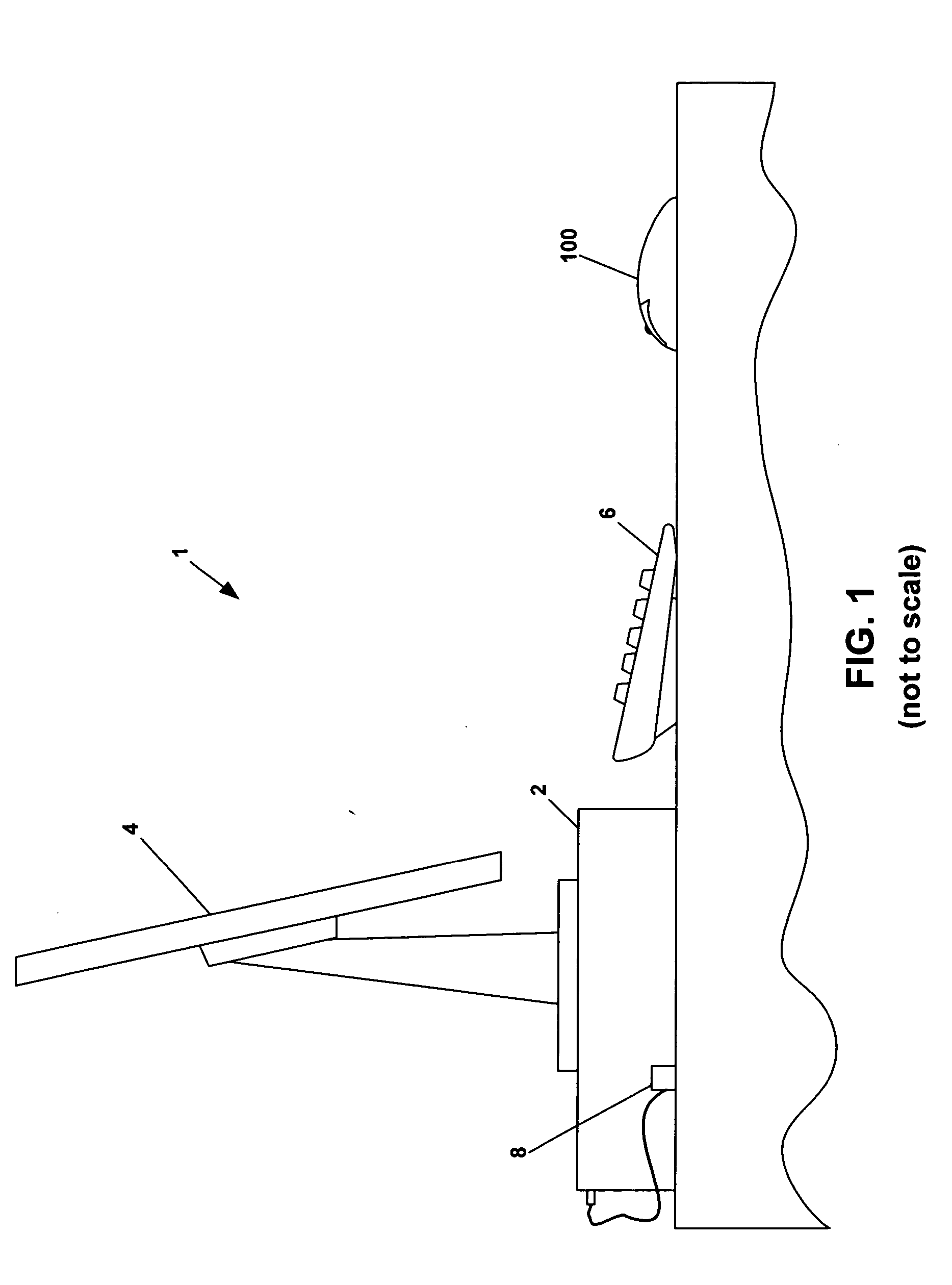

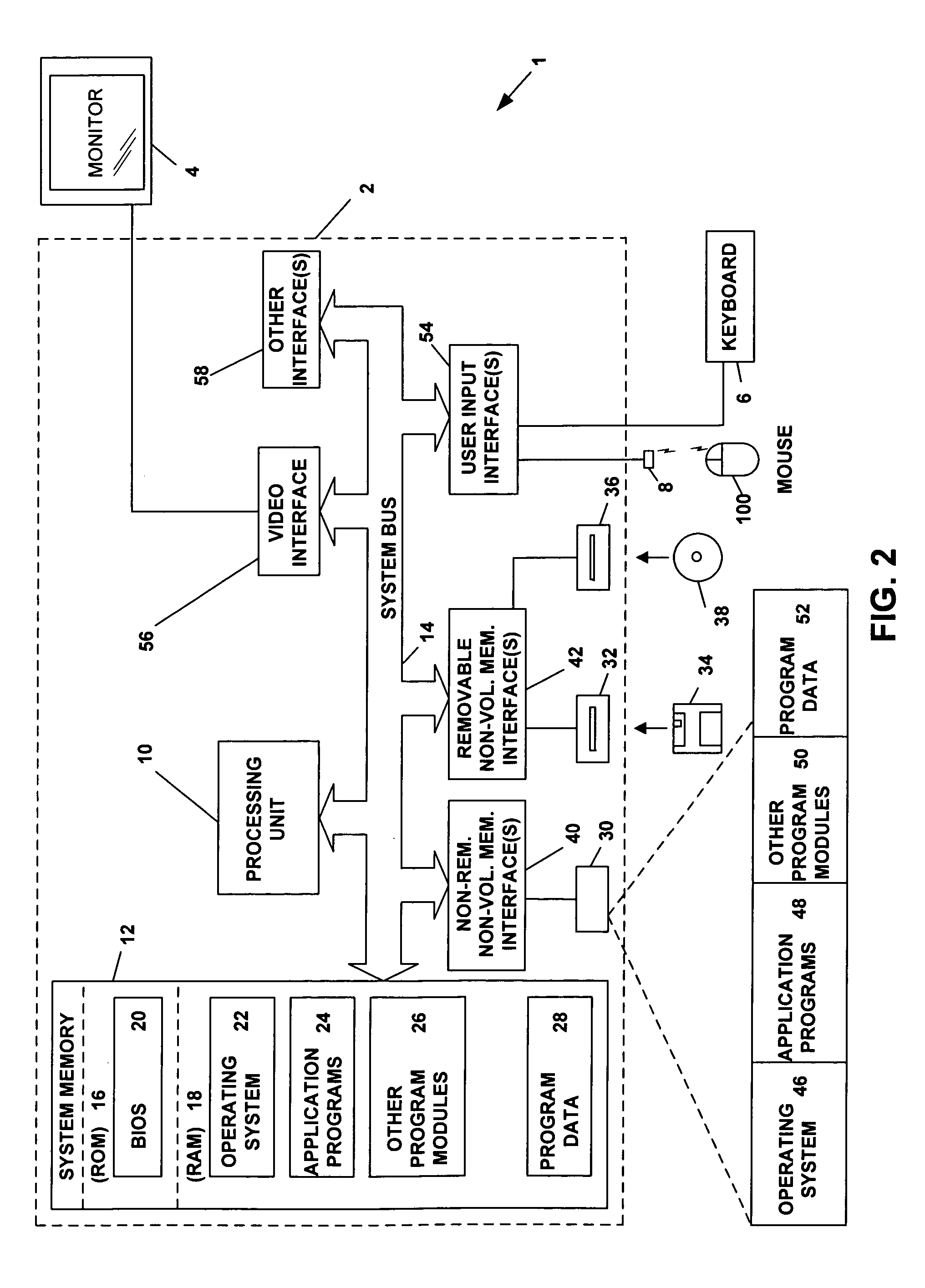

Input device with user-balanced performance and power consumption

ActiveUS7050798B2Improve device performanceIncreased power consumptionEnergy efficient ICTCathode-ray tube indicatorsBalance performancePower management

Owner:MICROSOFT TECH LICENSING LLC

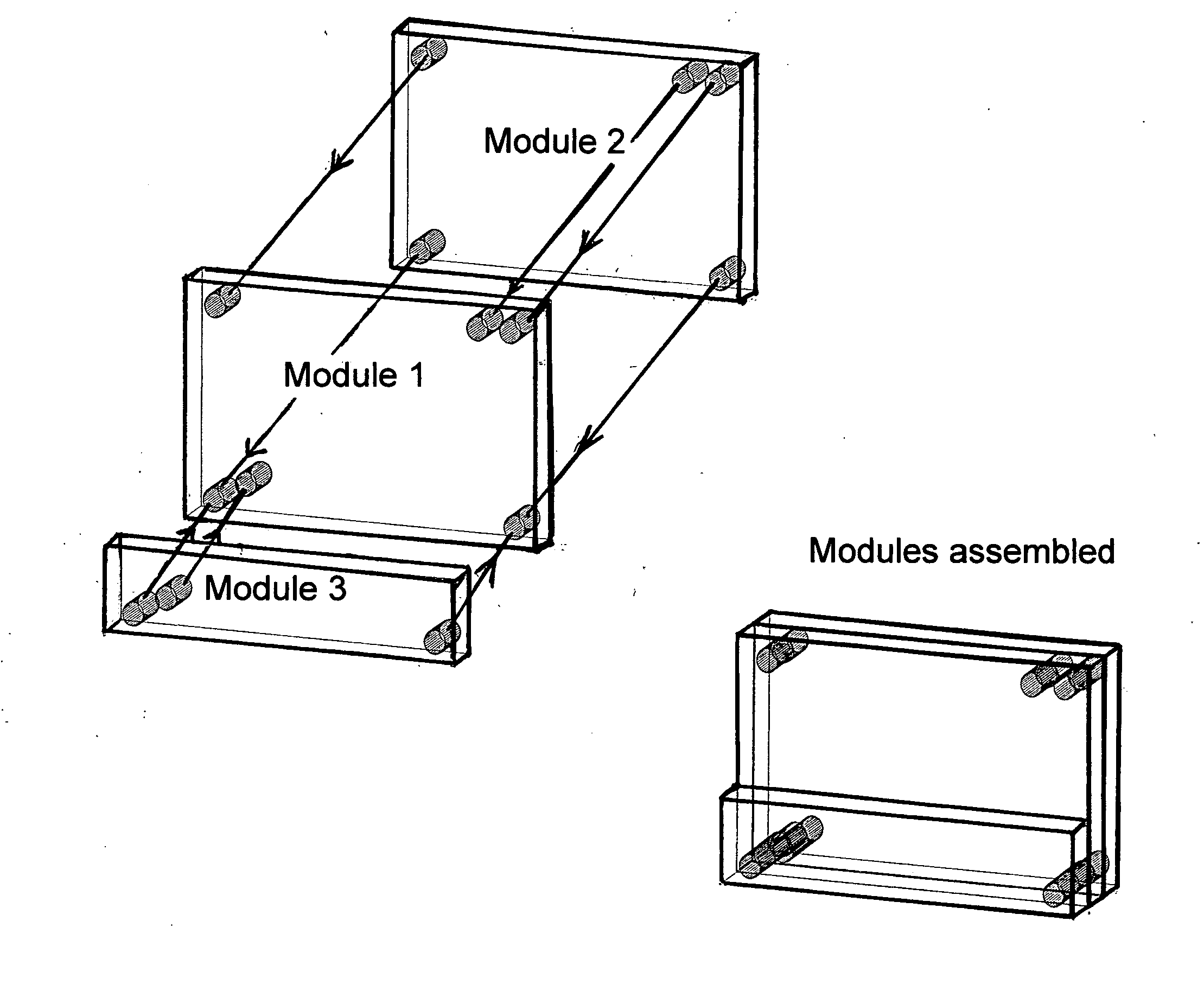

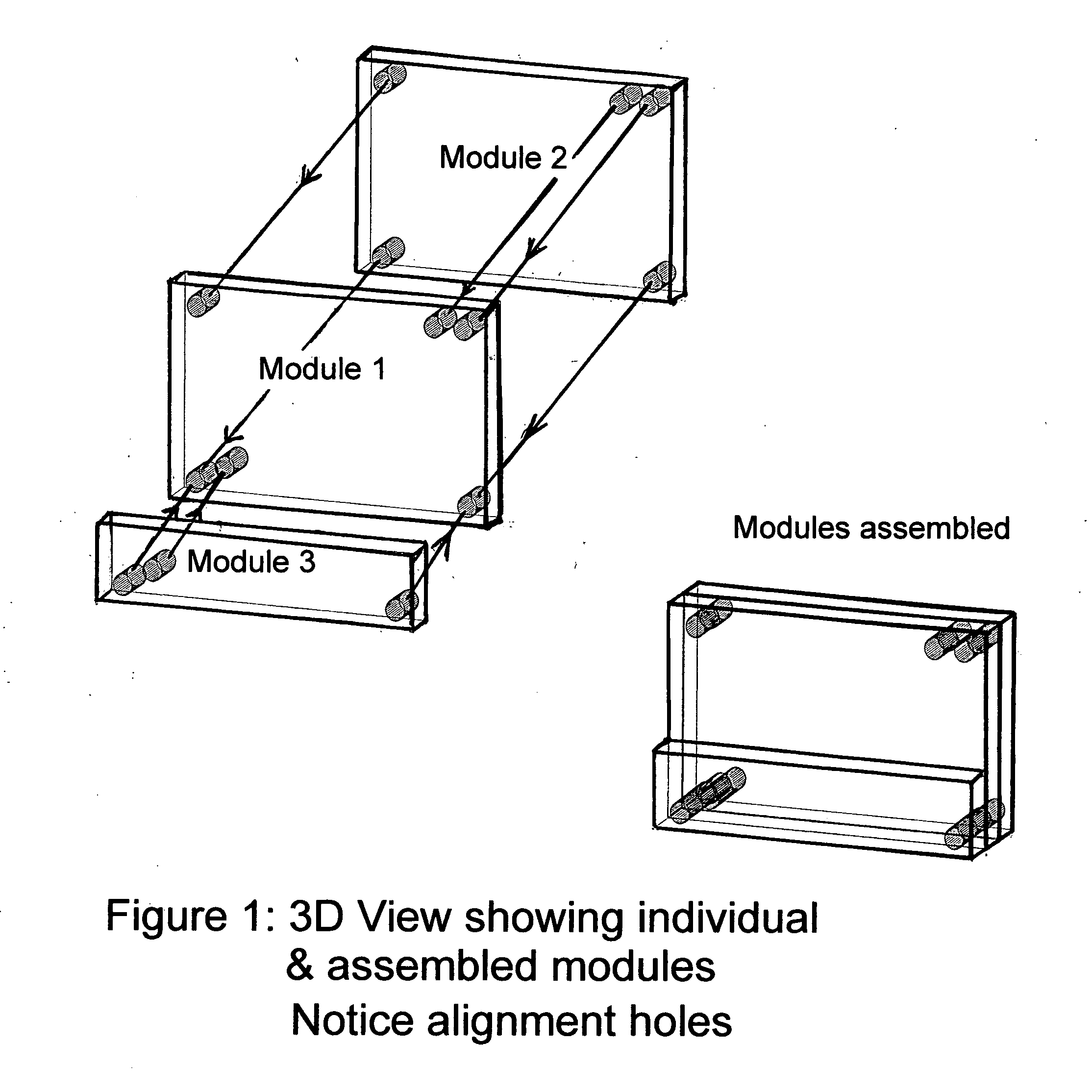

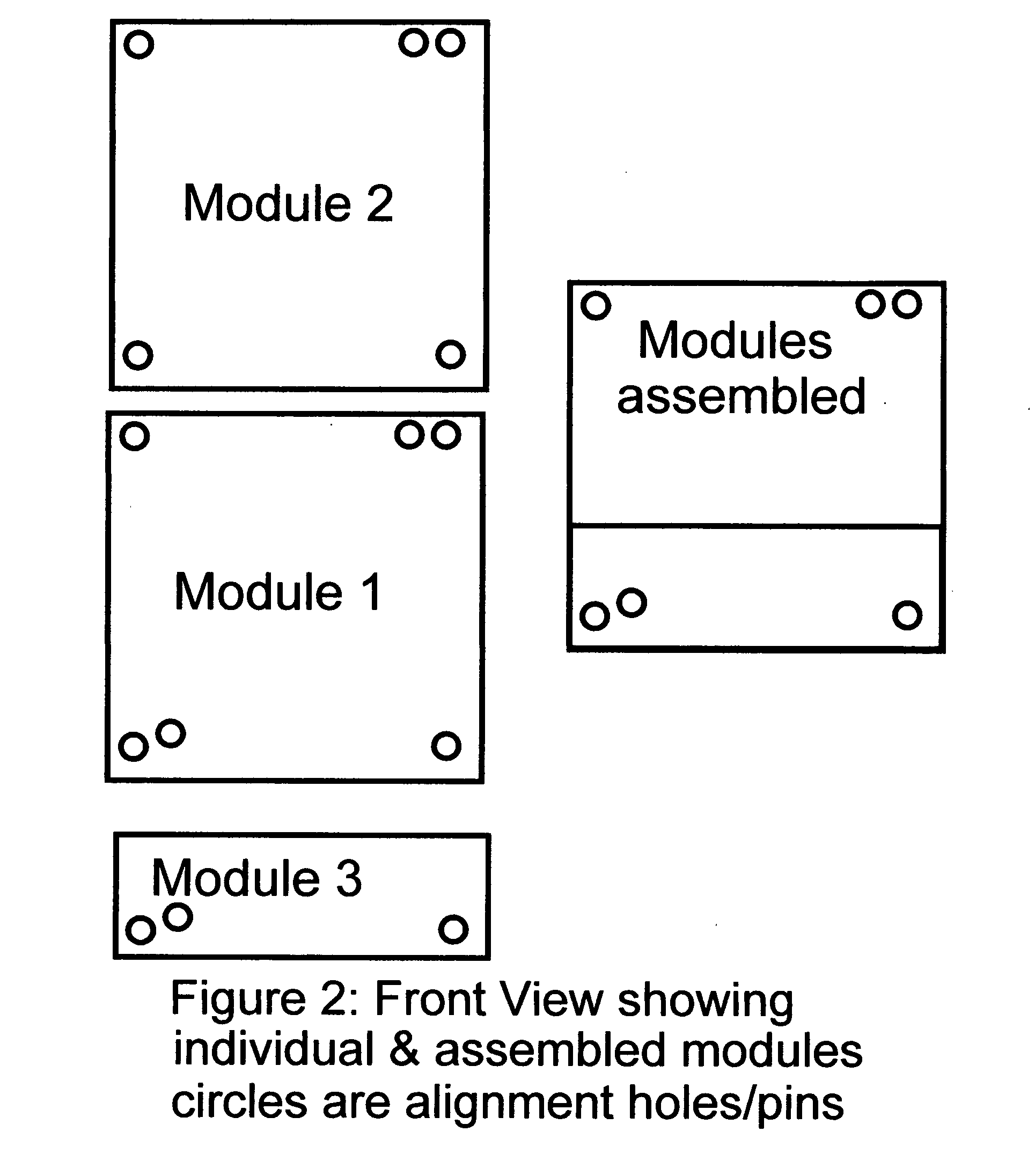

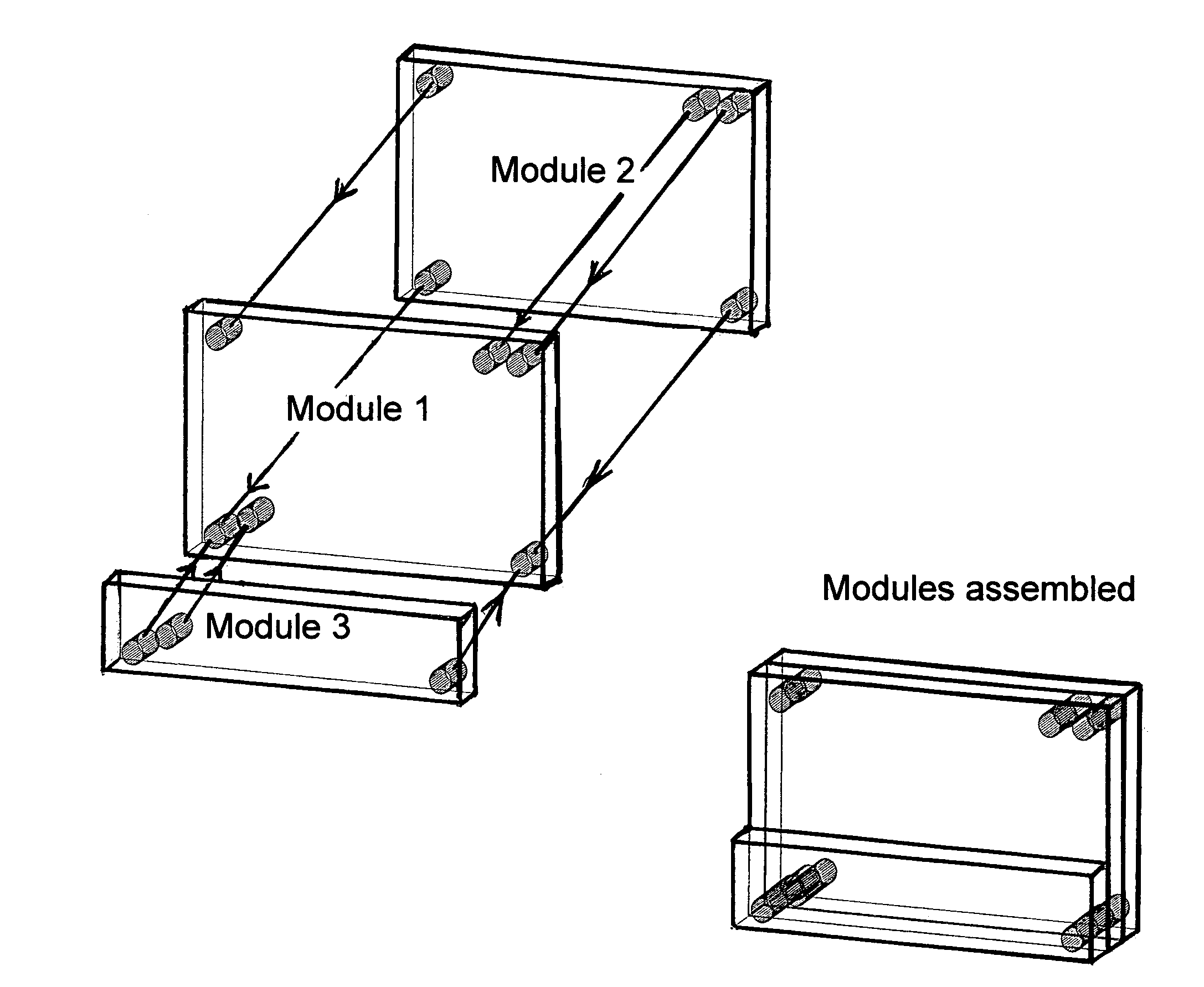

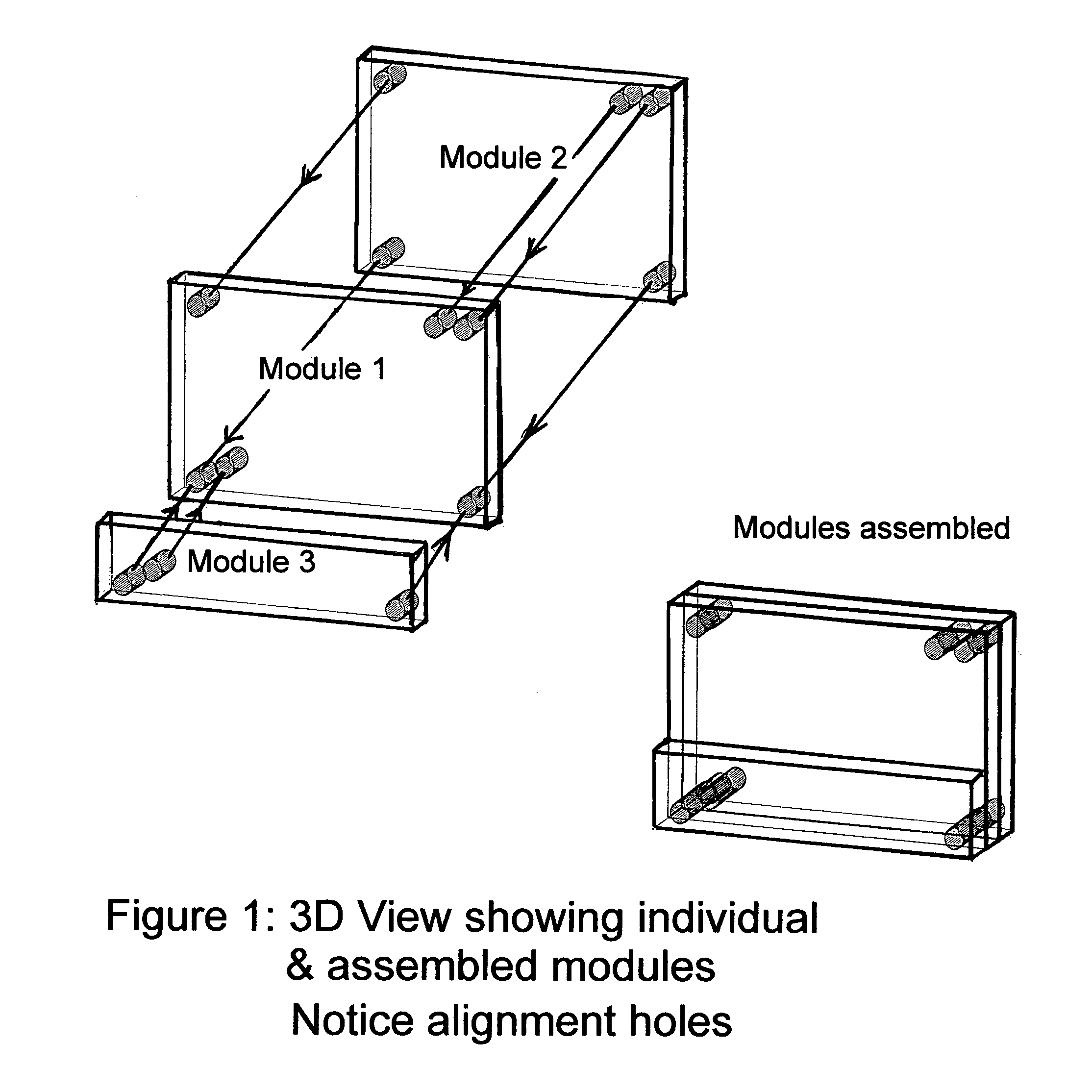

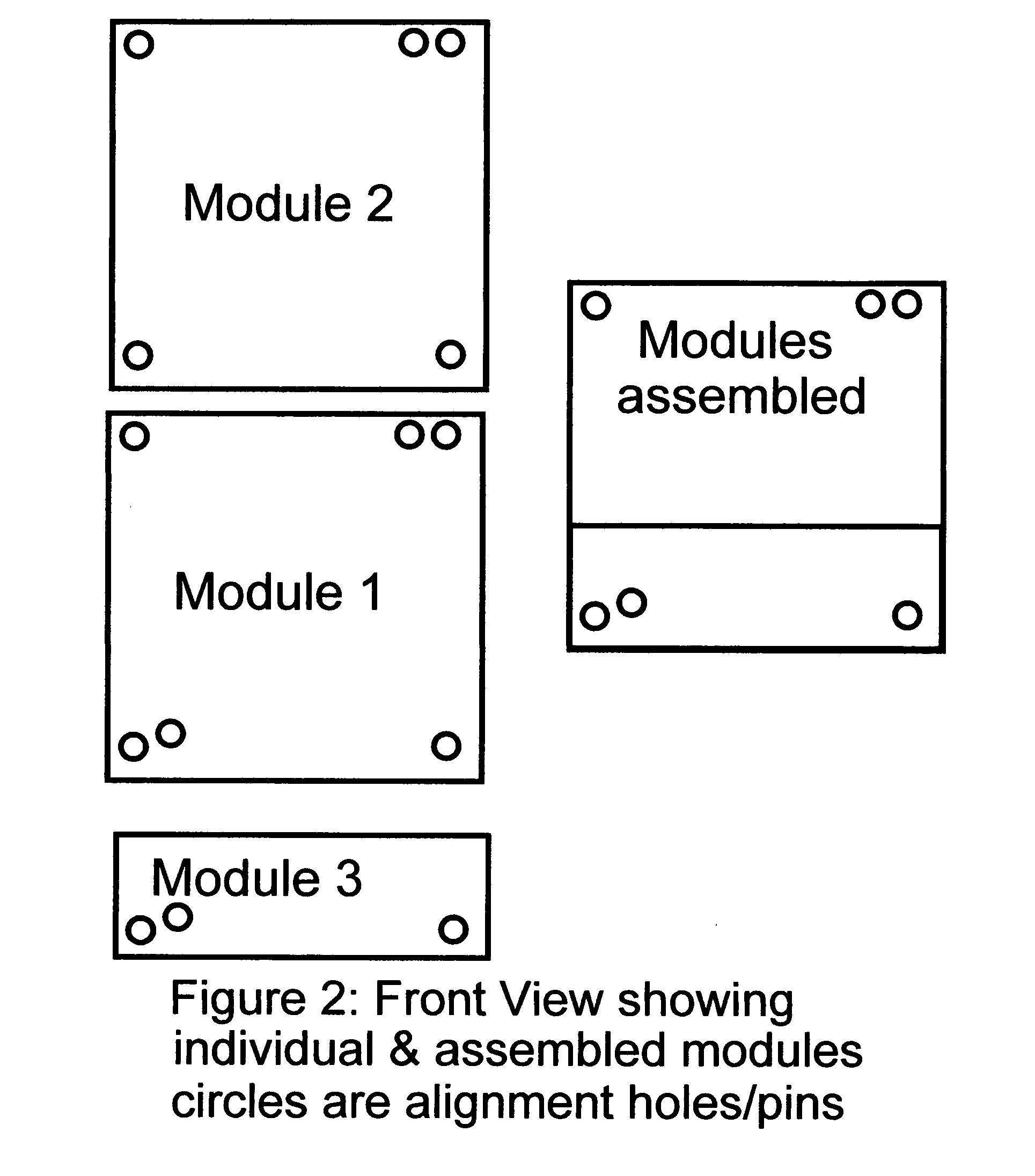

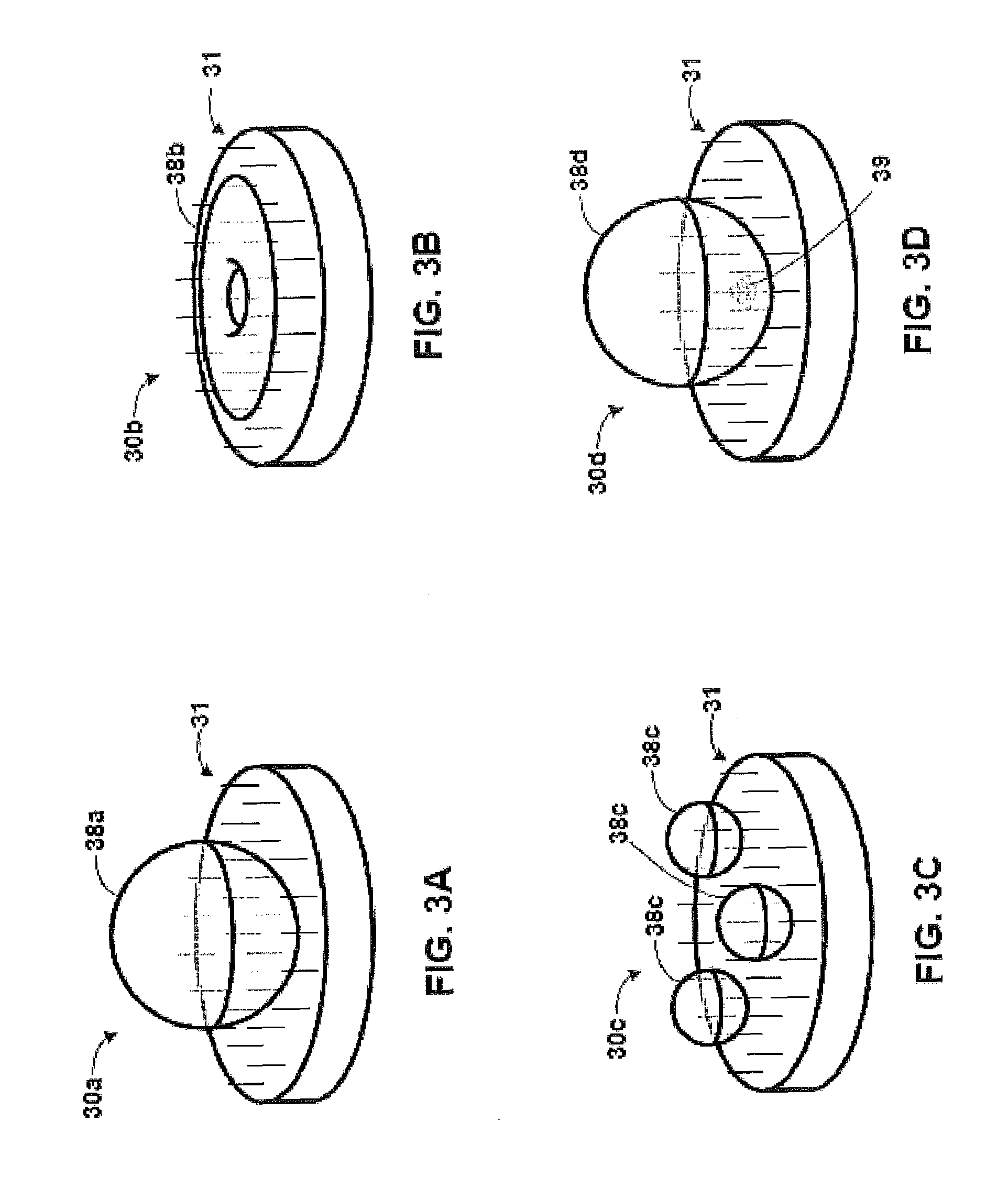

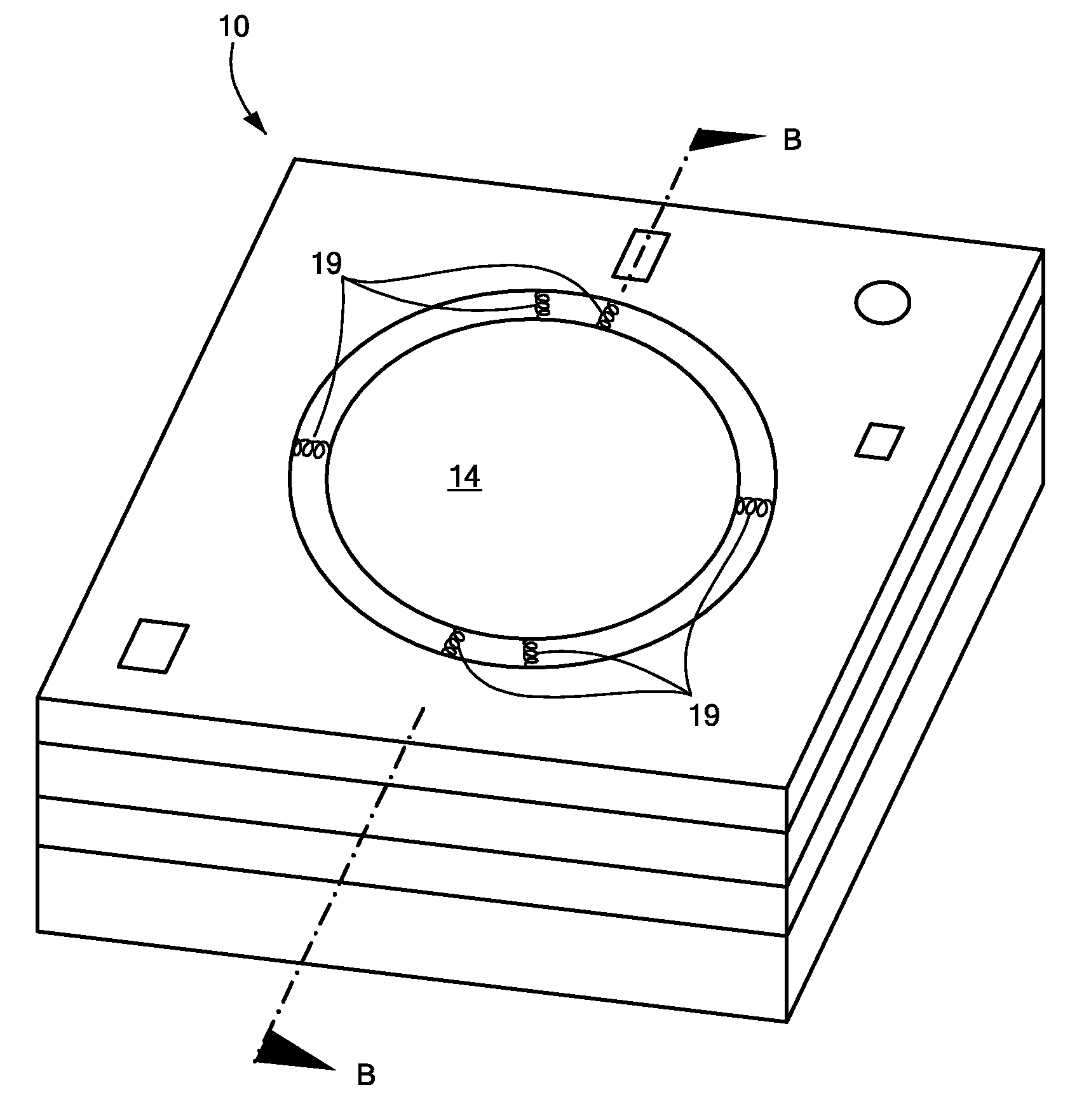

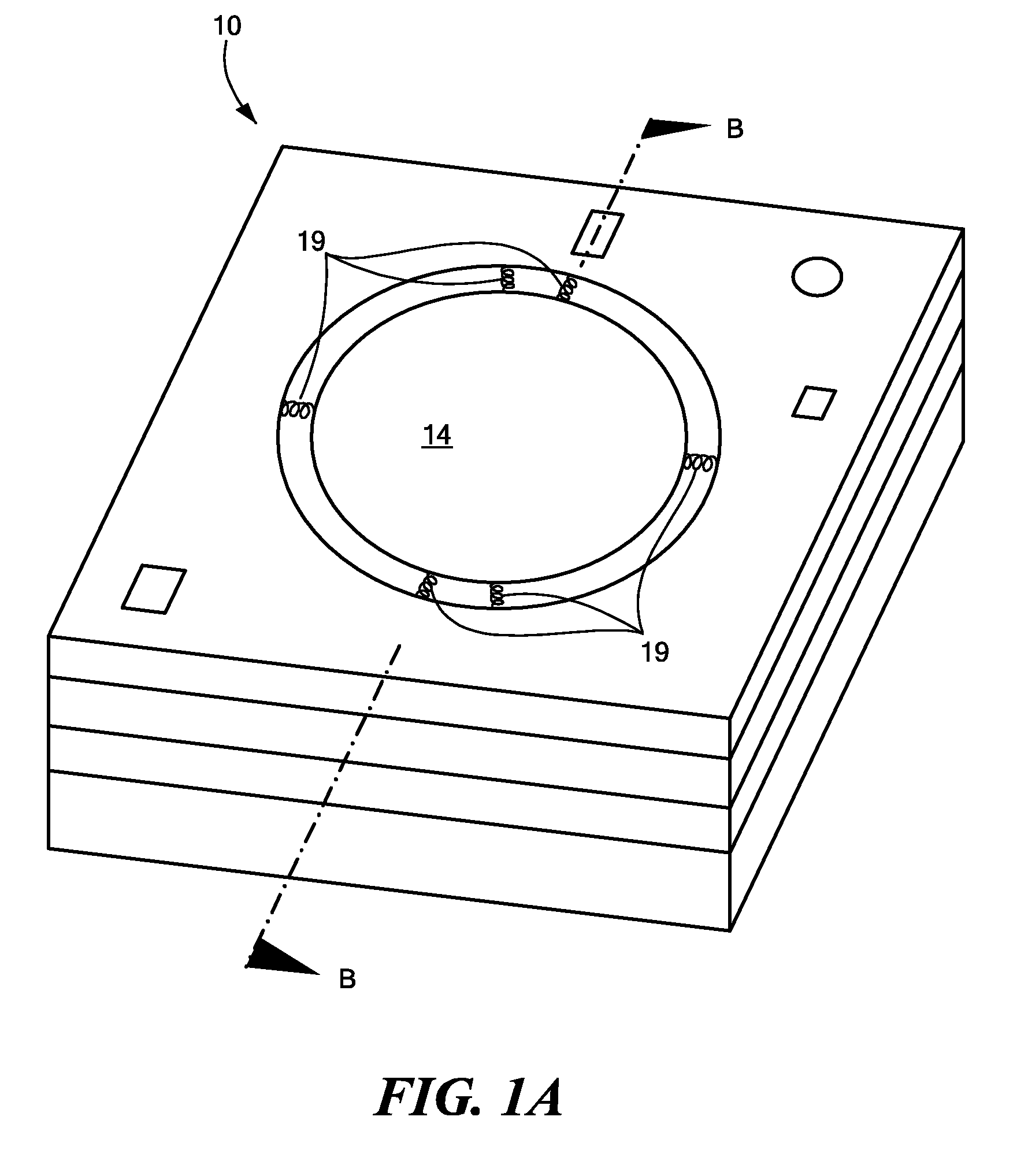

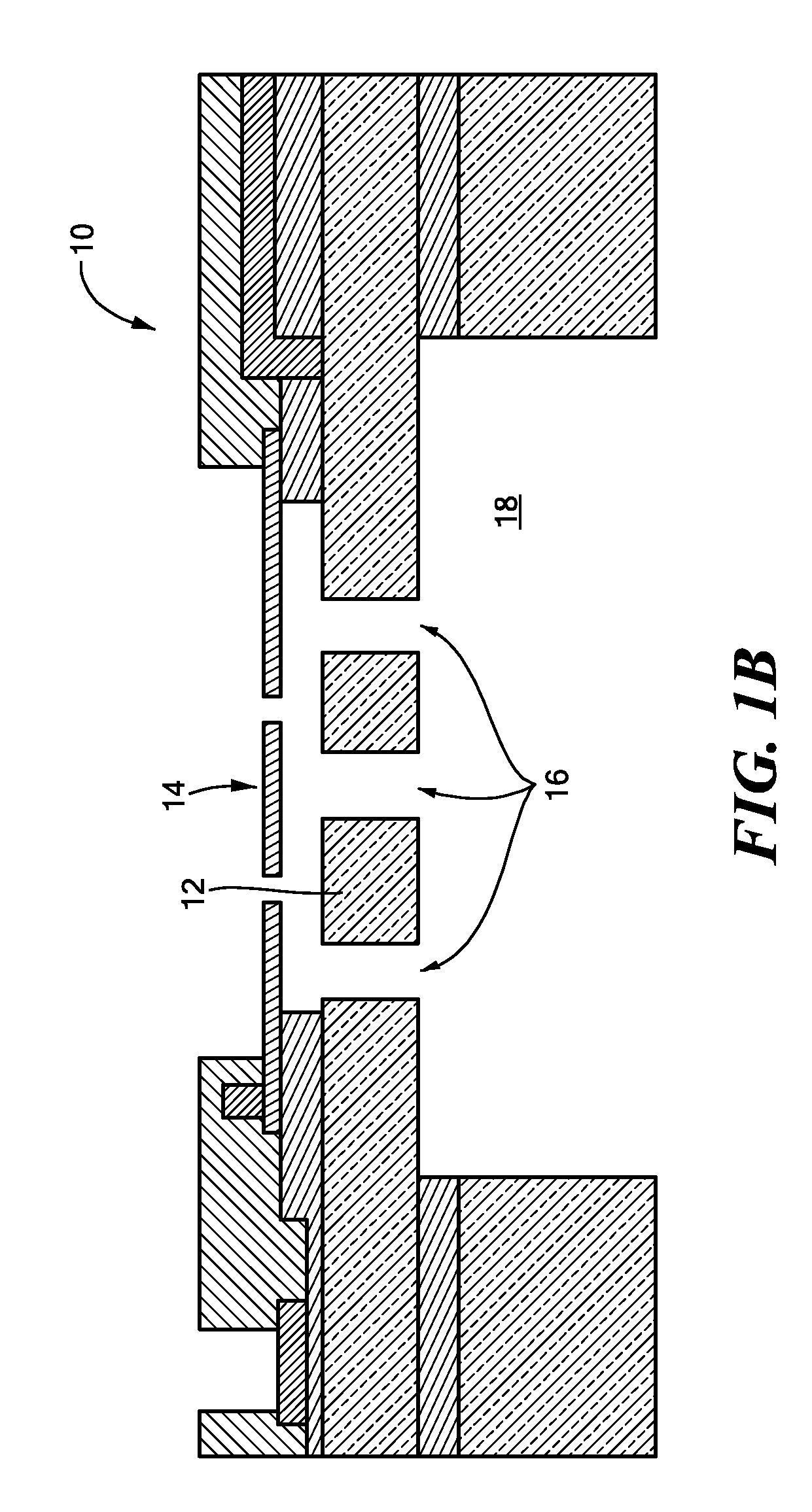

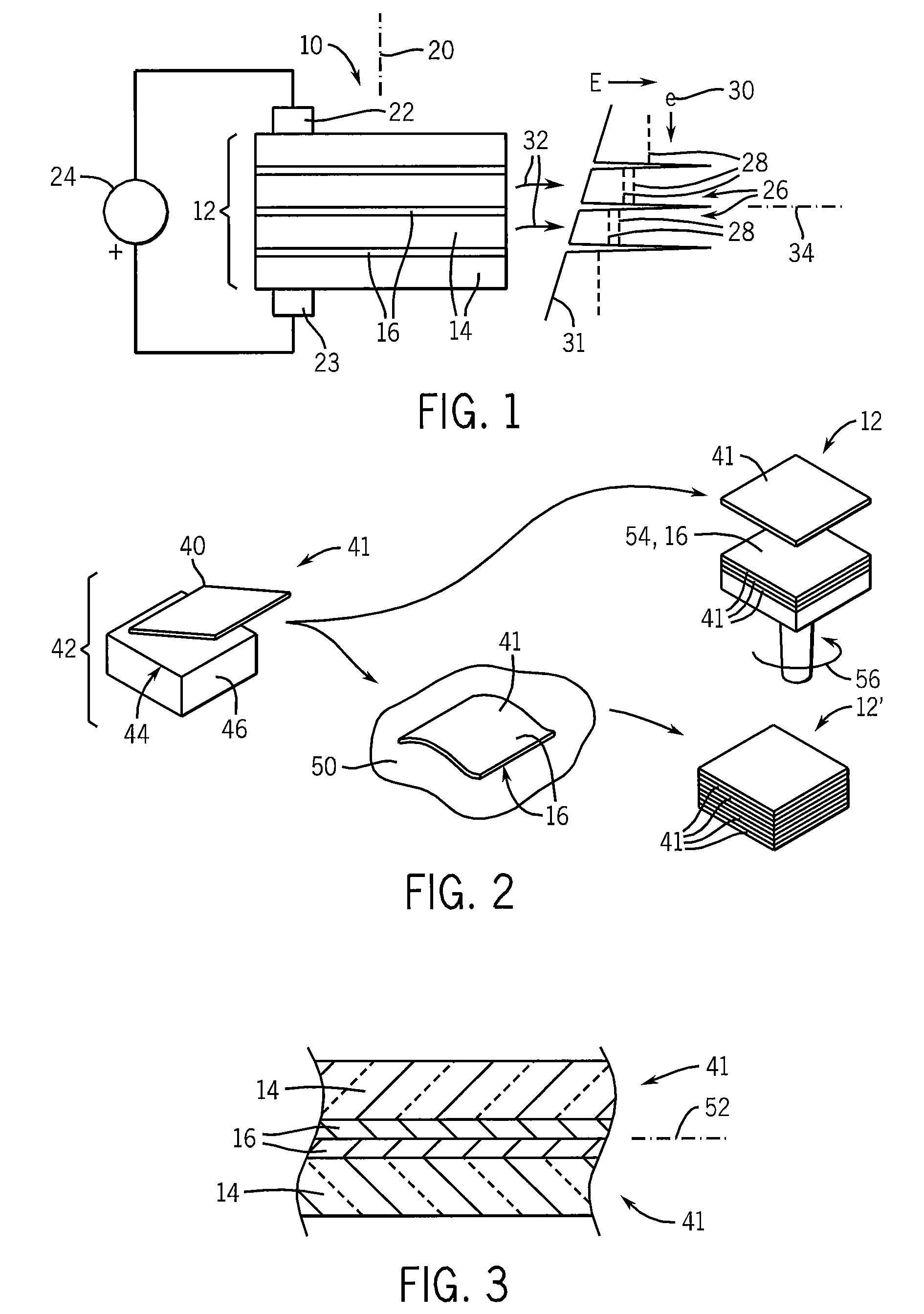

Robust modular electronic device without direct electrical connections for inter-module communication or control

ActiveUS20040198101A1Easy and cheap to add additional ESD protectionDegrades device performanceTelevision system detailsSide-by-side/stacked arrangementsElectric power transmissionTransformer action

A modular electronic device where (predominantly) sealed modules are aligned and attached / connected in pre-determined sequences, forming a robust block-like structure with extendable function: Control and / or inter-module communication are implemented without direct electrical interconnect, by non-contact means such as (magnetic, inductive, light, infrared, radio frequency, sound, ultrasound, or other non-contact means). This device's inter-module power transfer may be with or without direct electrical contact, or devices may be internally powered. Power transfer through inductive / transformer action where one or more alignment pins are used as transformer core is one potential implementation. Modules may be fluid filled to facilitate cooling and / or crush resistance to high-pressure environments.

Owner:RAPP ROBERT

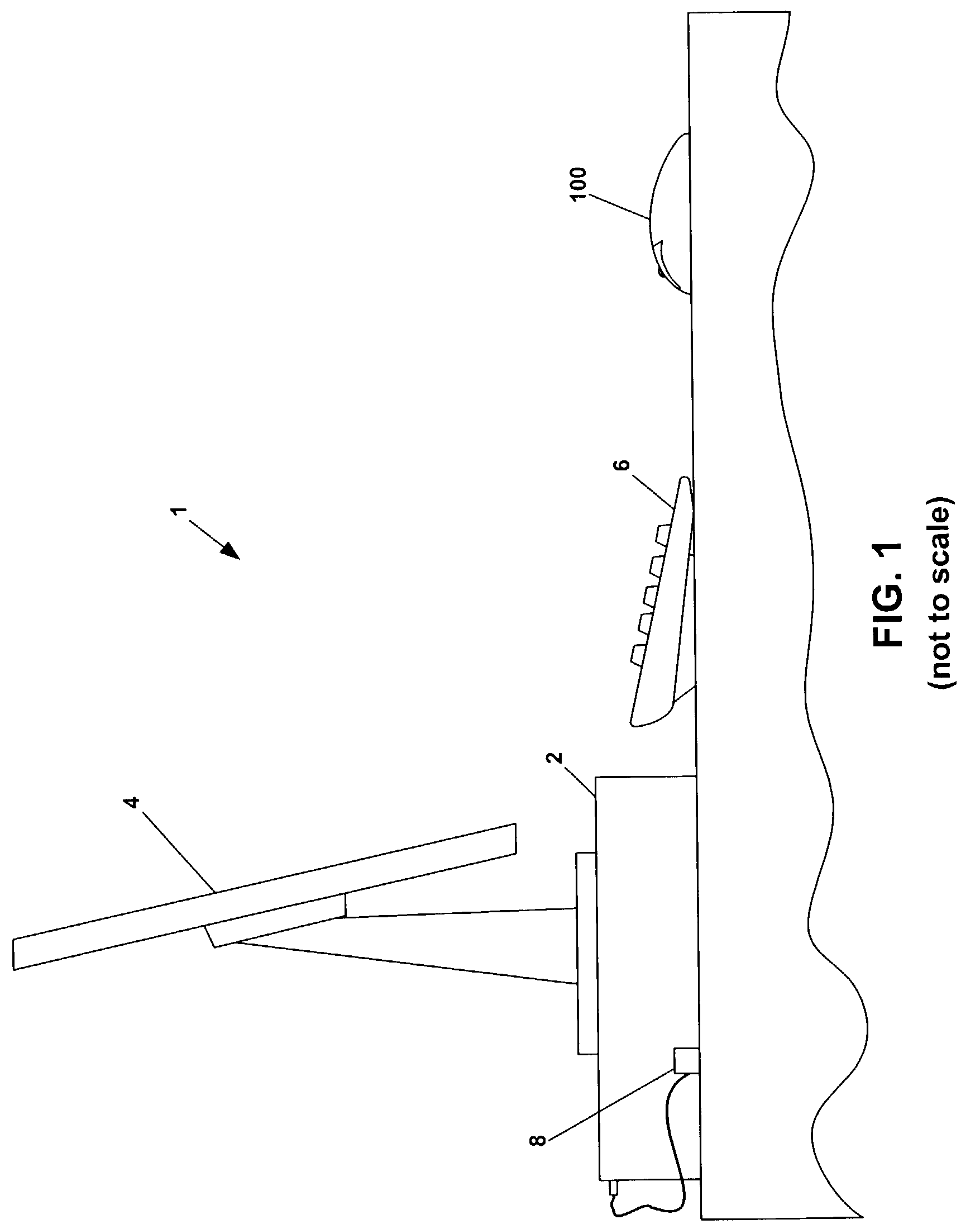

Heat generator

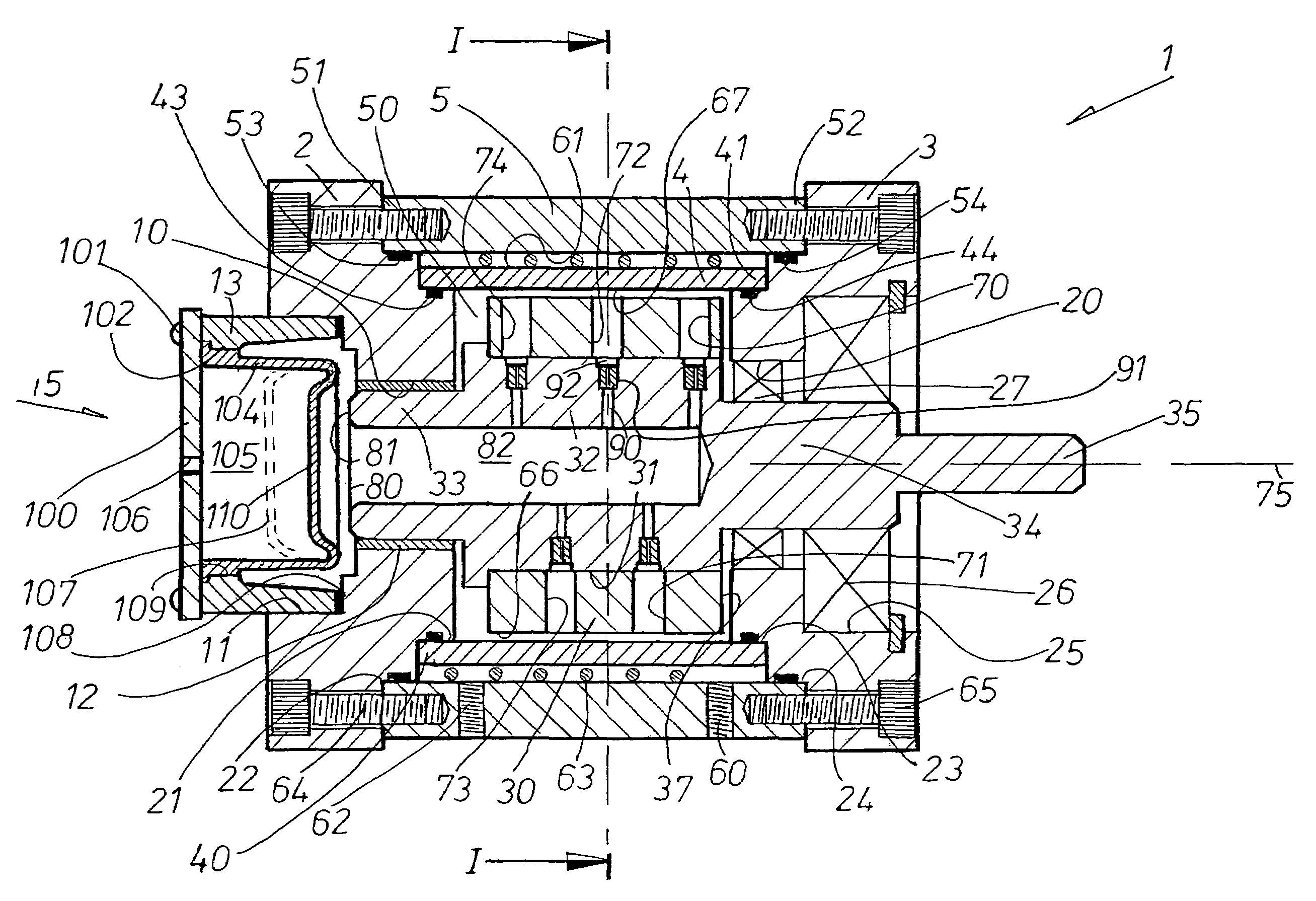

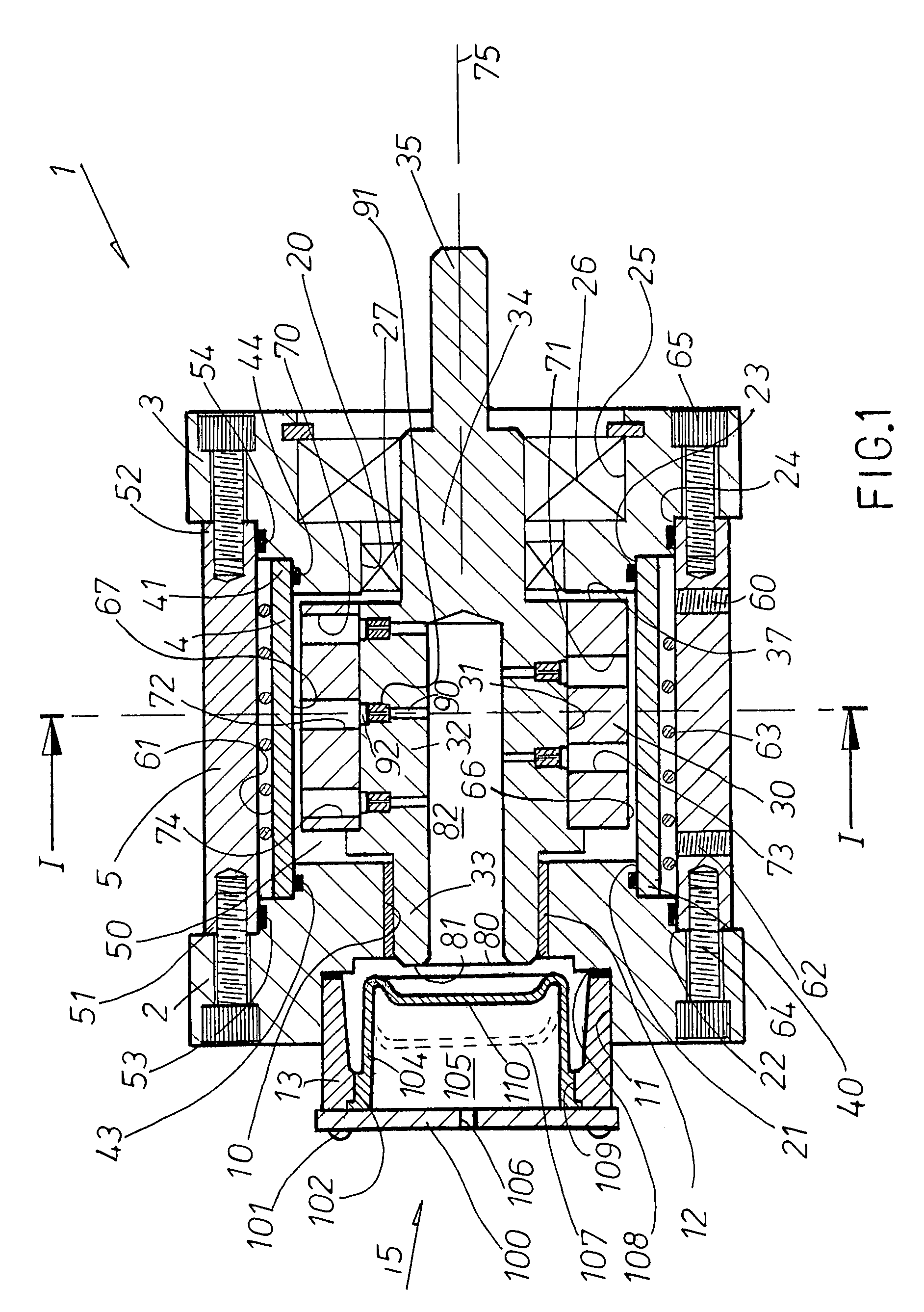

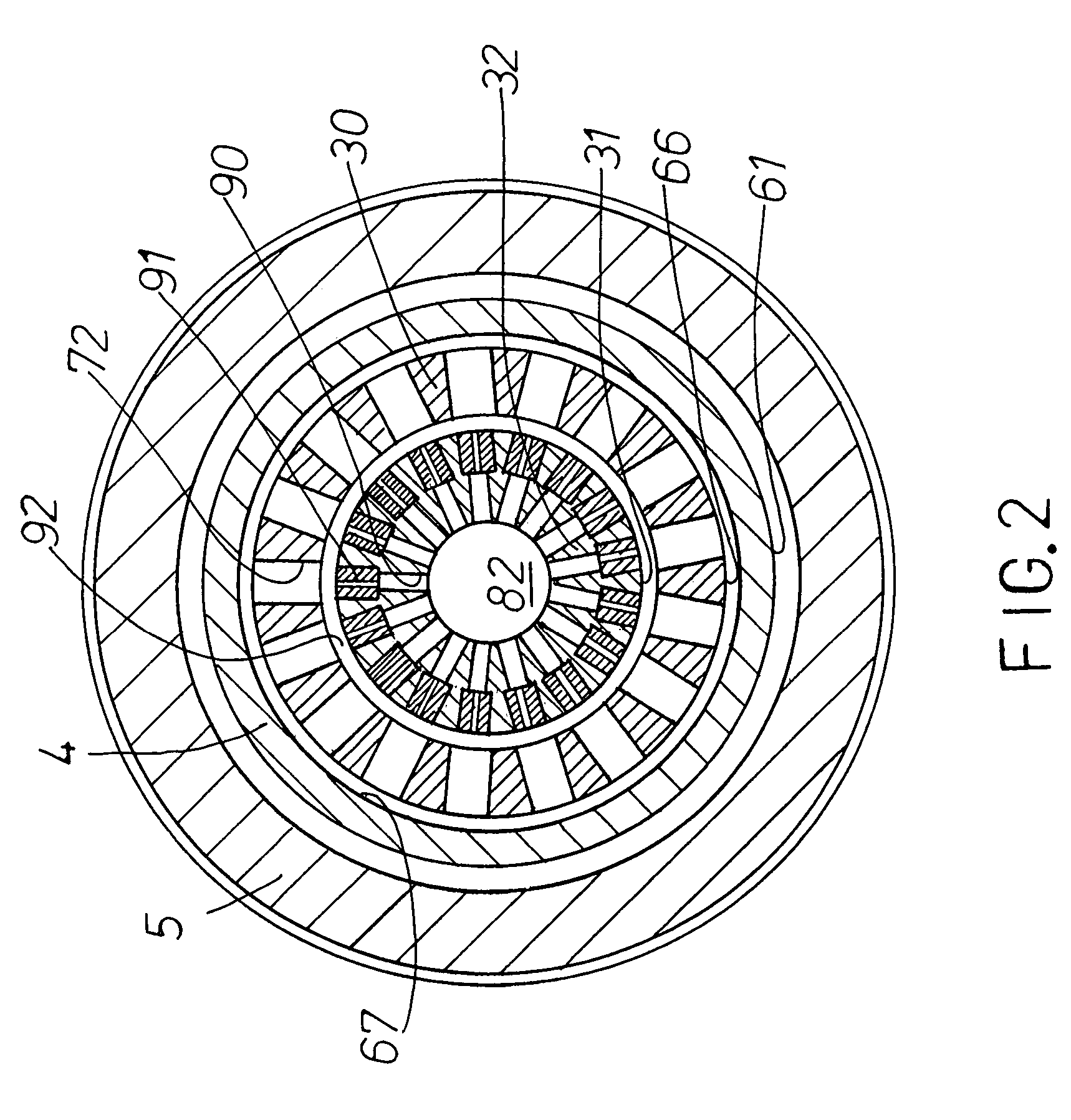

InactiveUS7387262B2Reduce equipment capacityPositive performanceAir-treating devicesOther heat production devicesInterior spaceViscous liquid

An apparatus for the heating of a viscous fluid contained in a heat generating chamber by a rotatable unit having a fluid shearing surface formed on a face thereof, the unit by shearing of the viscous fluid on that face induces the heating of said viscous fluid and where an external heat extracting surface is provided for this heat to be removed by a further fluid in contact with that surface. The two dissimilar fluids are kept apart by at least the housing acting as a fluid partition. The unit has an interior space as a storage location for viscous fluid with a deformable element for volume changes of the viscous fluid during the operation of the apparatus.

Owner:THOMA CHRISTIAN

New method for mechanical stress enhancement in semiconductor devices

ActiveUS20100052065A1High carrier mobilityReduce stressTransistorSolid-state devicesDevice materialSemiconductor

The present disclosure provides an integrated circuit. The integrated circuit includes a semiconductor substrate having an active region; at least one operational device on the active region, wherein the operational device include a strained channel; and at least one first dummy gate disposed at a side of the operational device and on the active region.

Owner:MOSAID TECH

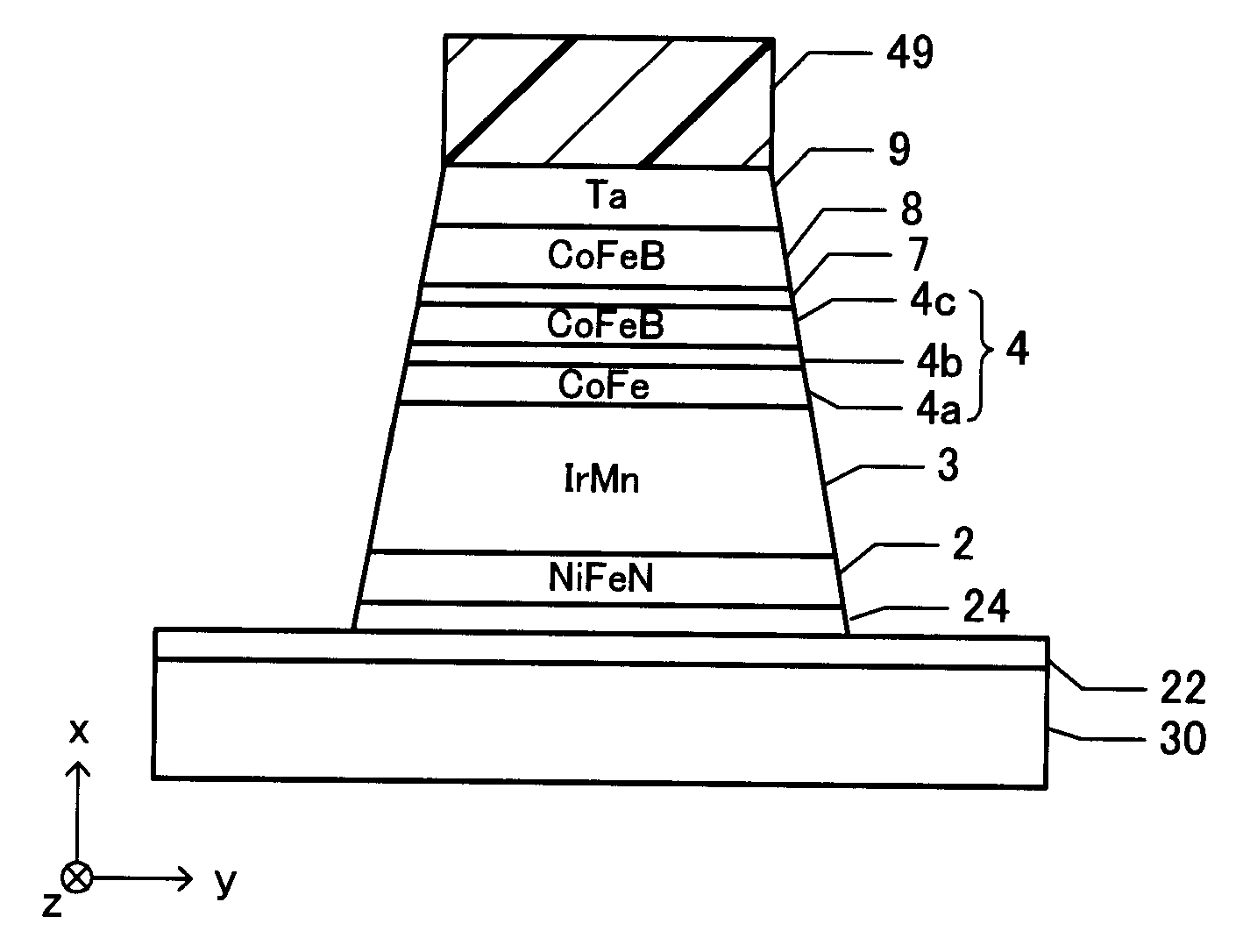

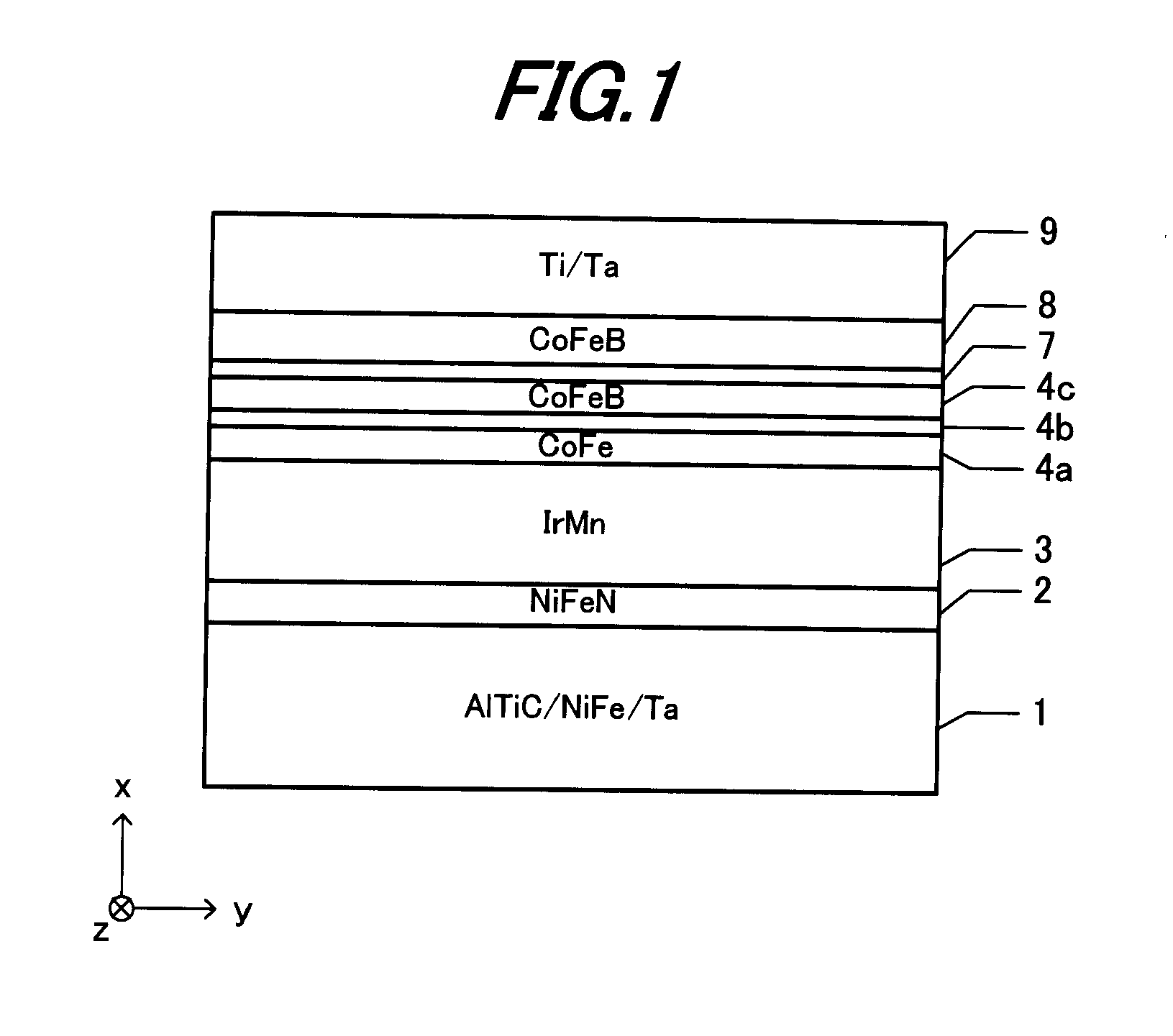

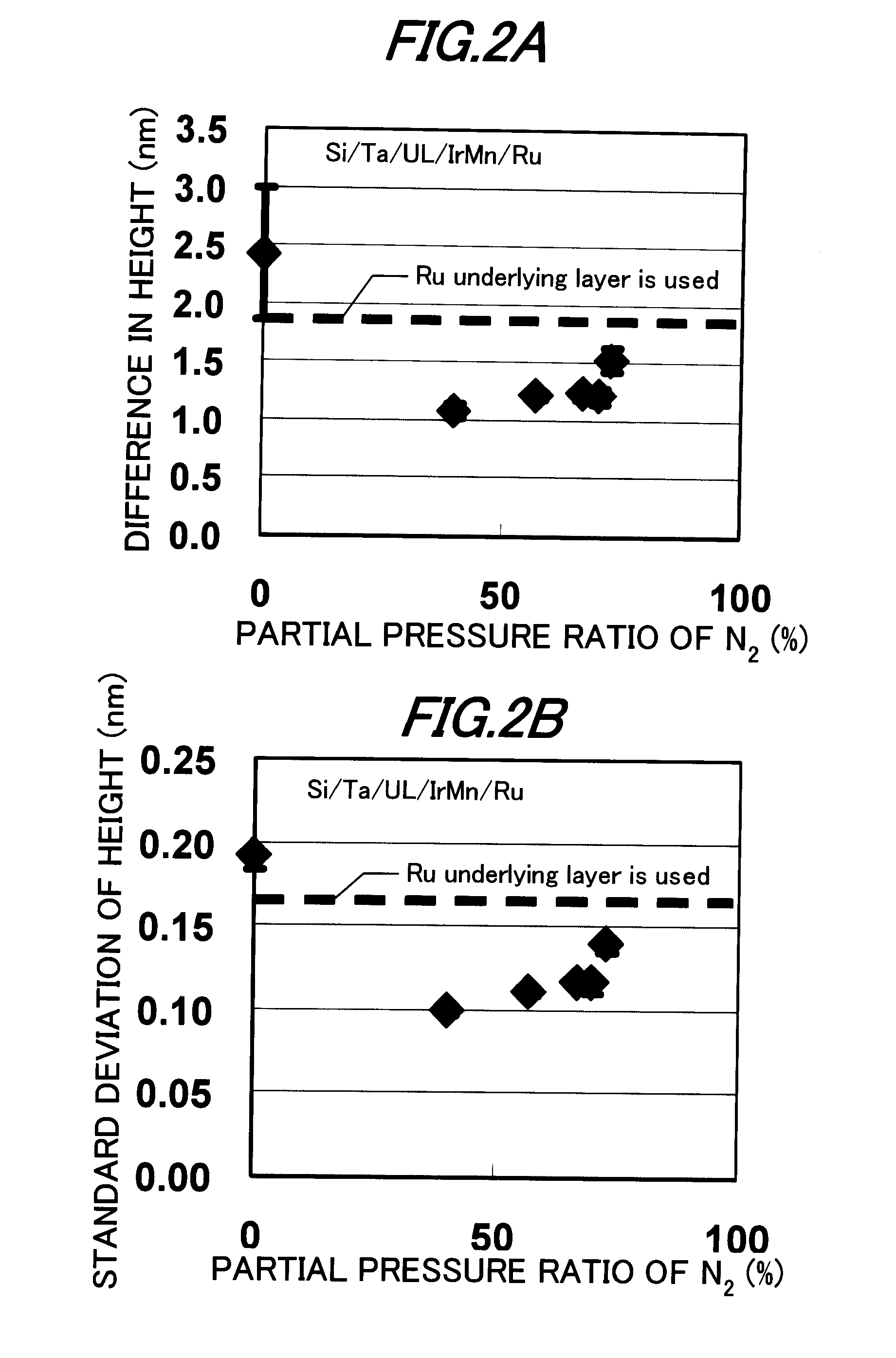

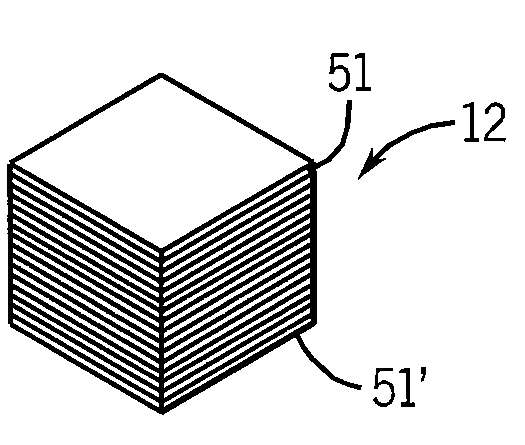

Magnetoresistance effect device, magnetic lamination structural body, and manufacture method for magnetic lamination structural body

InactiveUS20080232003A1Improve surface roughnessLower areaNanomagnetismMagnetic measurementsMagnetizationNon magnetic

An underlying layer (2) made of NiFeN is disposed over the principal surface of a substrate. A pinning layer (3) made of antiferromagnetic material containing Ir and Mn is disposed on the underlying layer. A reference layer (4c) made of ferromagnetic material whose magnetization direction is fixed through exchange-coupling with the pinning layer directly or via another ferromagnetic material layer, is disposed over the pinning layer. A nonmagnetic layer (7) made of nonmagnetic material is disposed over the reference layer. A free layer (8) made of ferromagnetic material whose magnetization direction changes in dependence upon an external magnetic field, is disposed over the nonmagnetic layer.

Owner:FUJITSU LTD

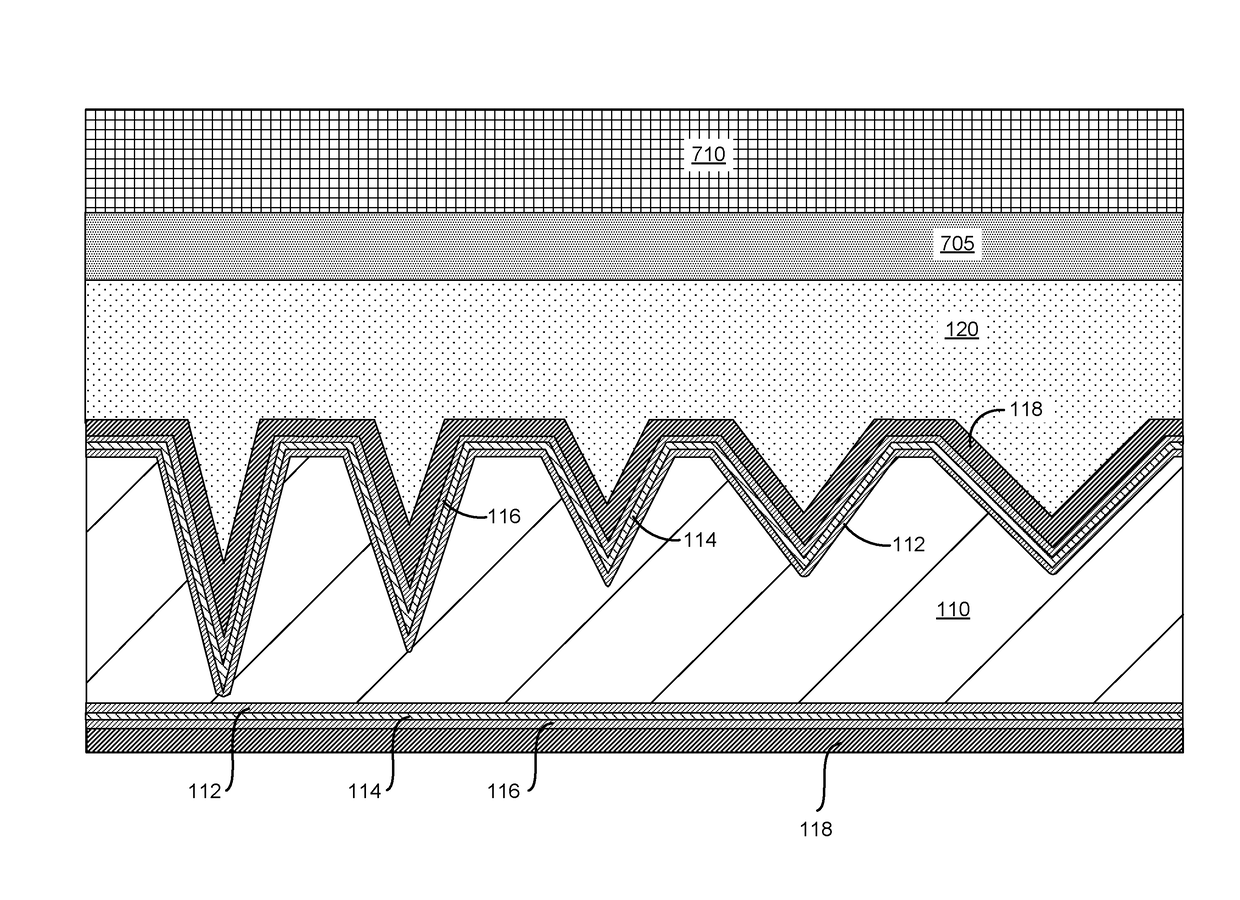

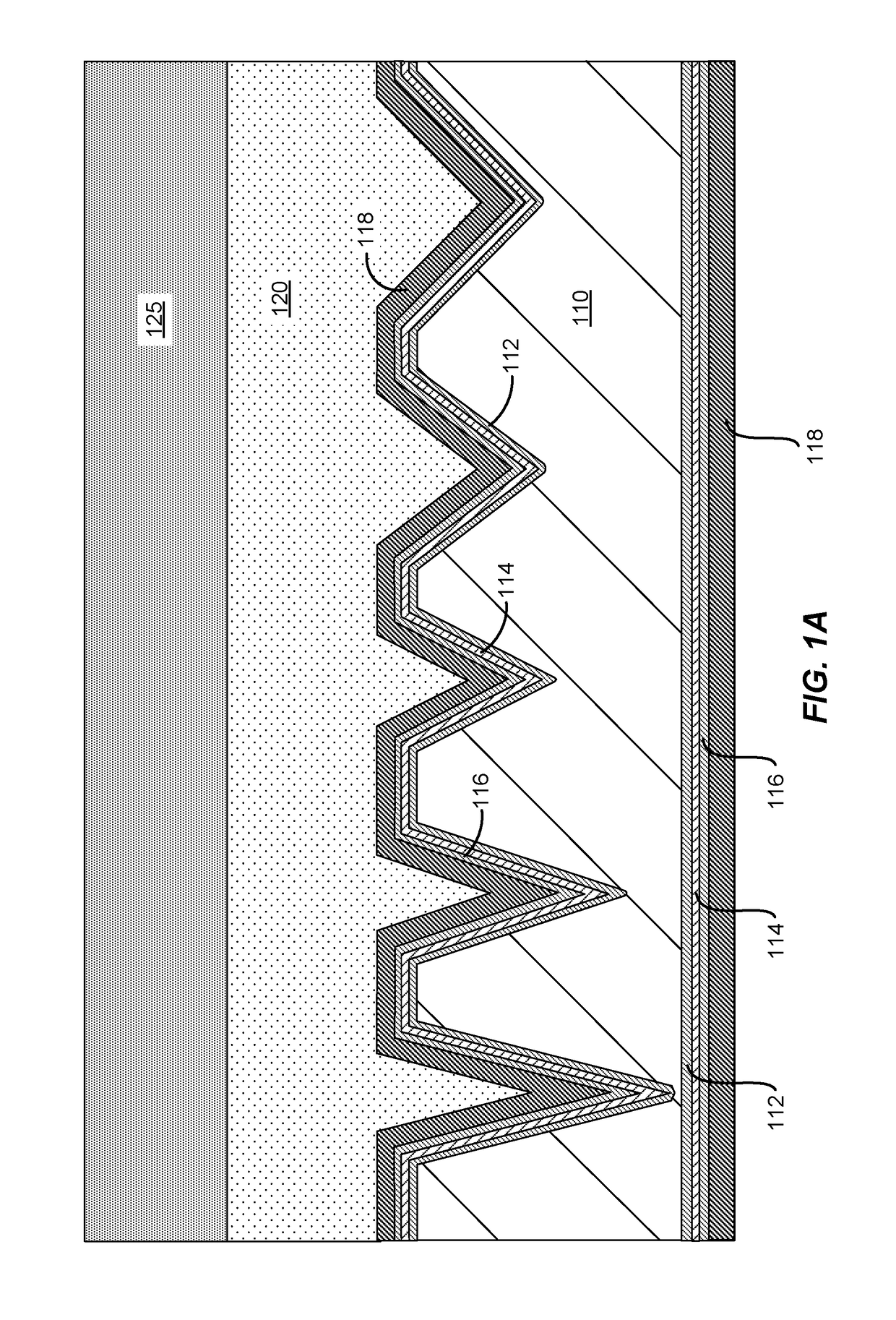

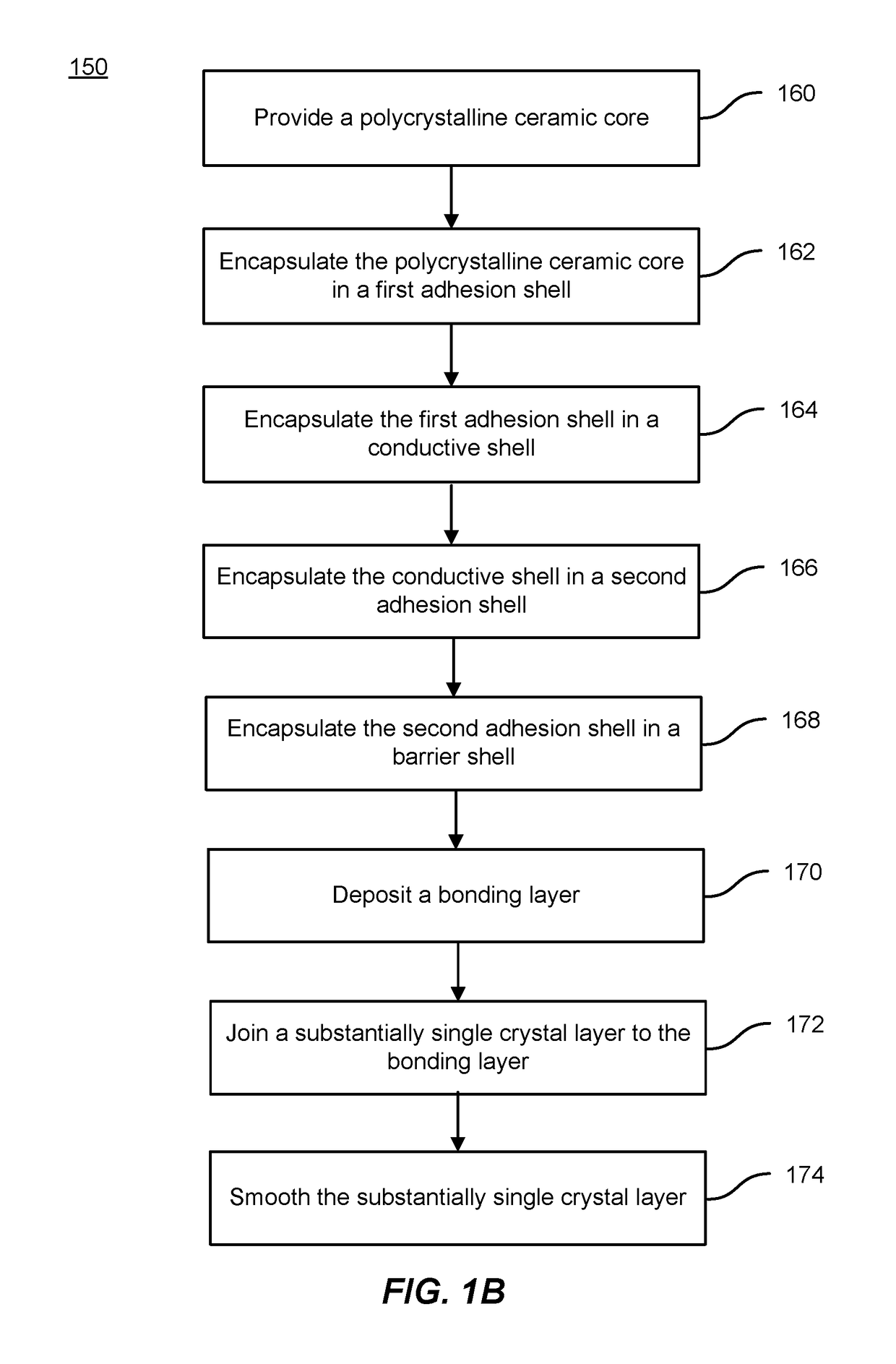

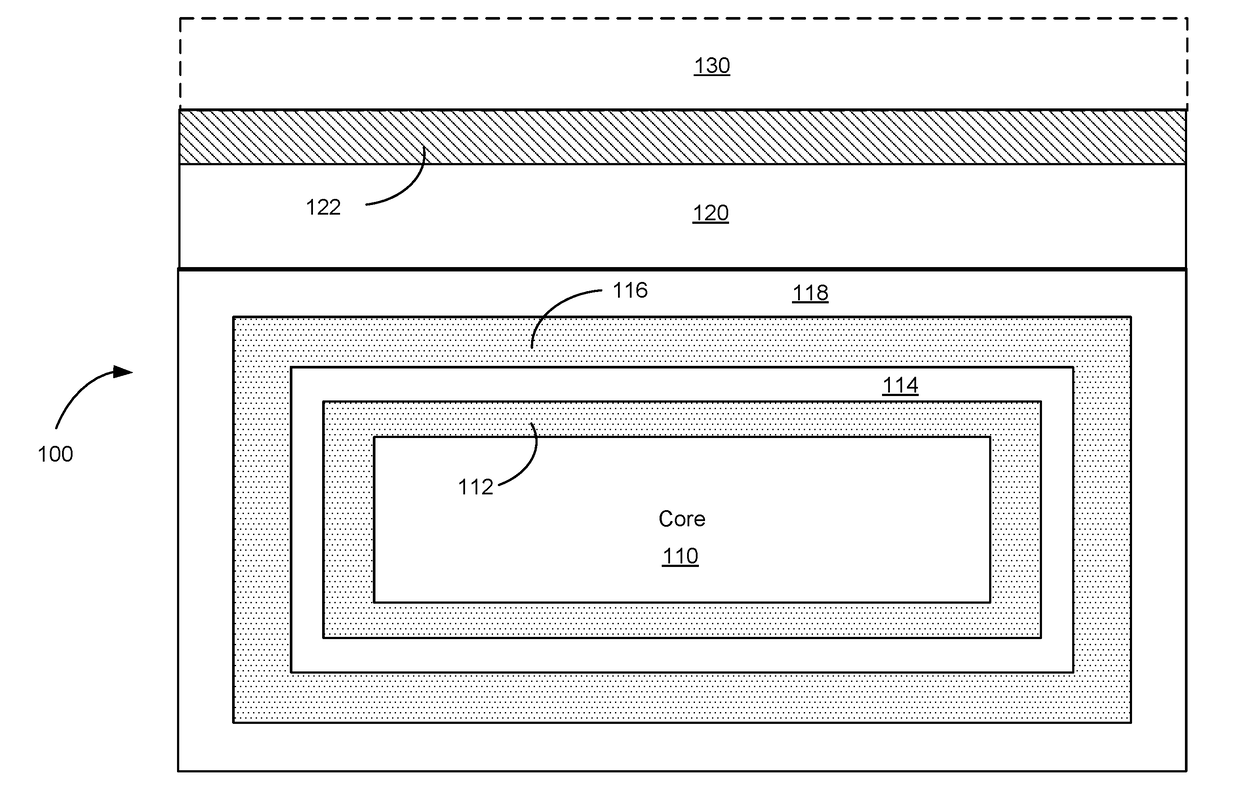

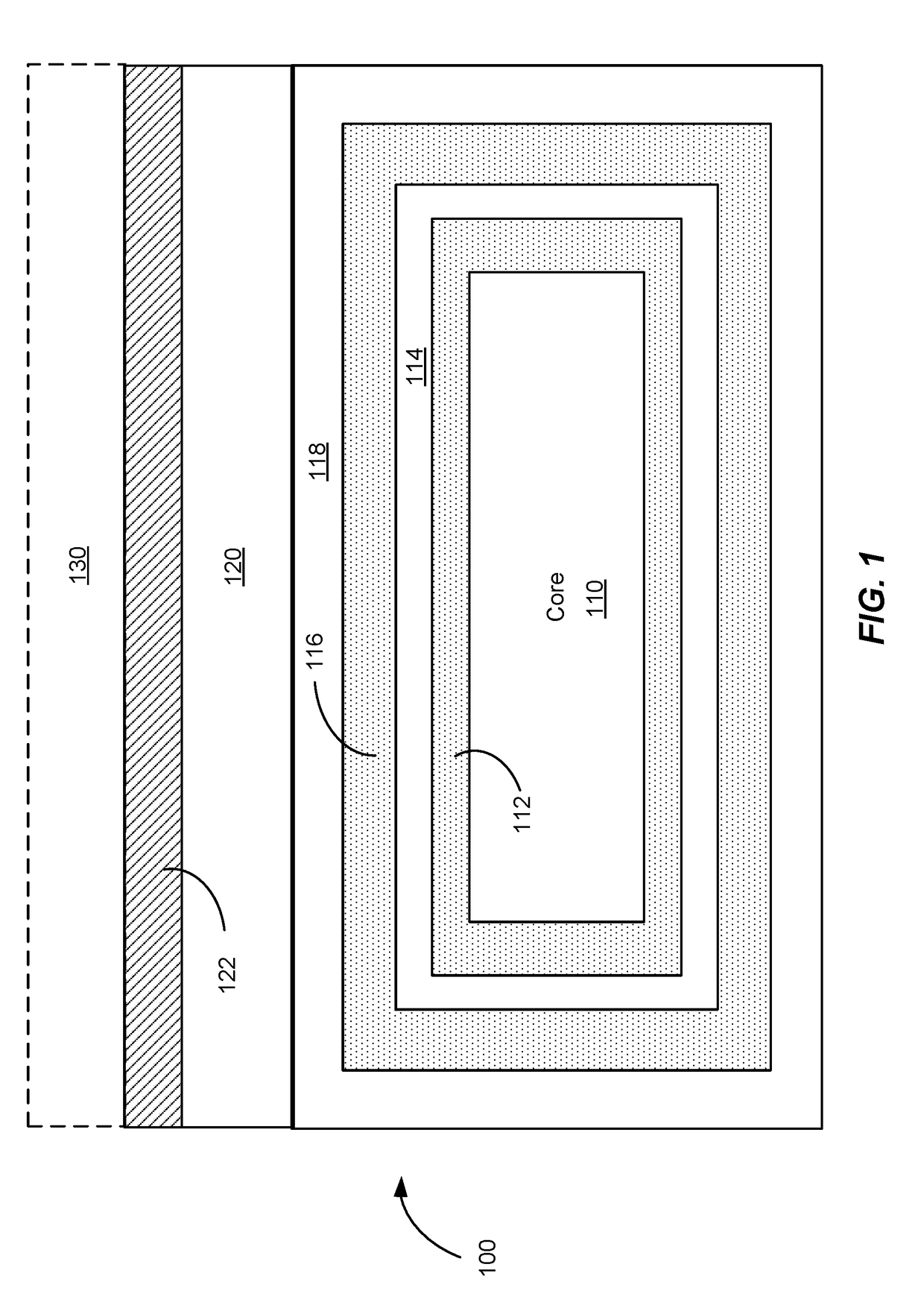

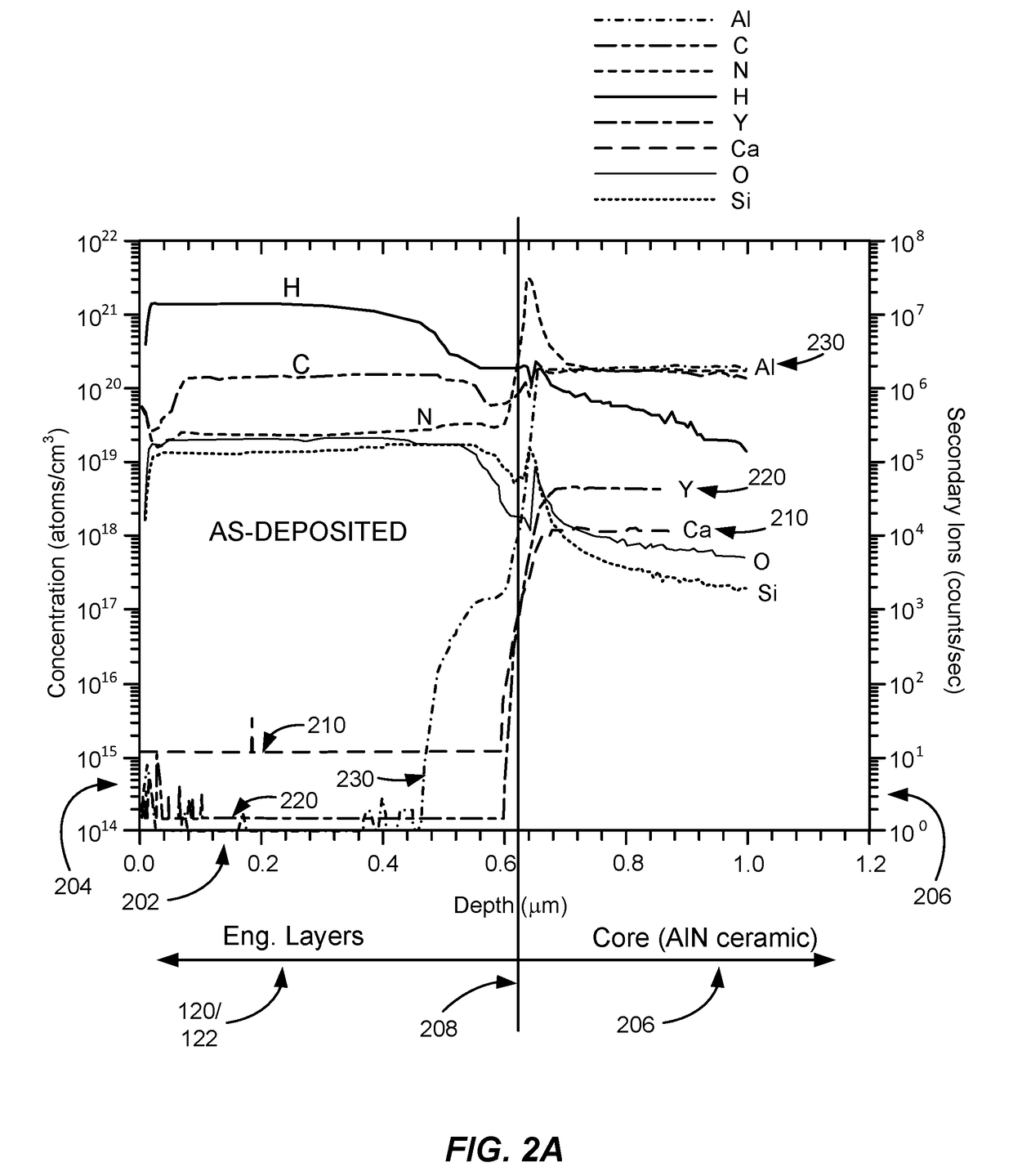

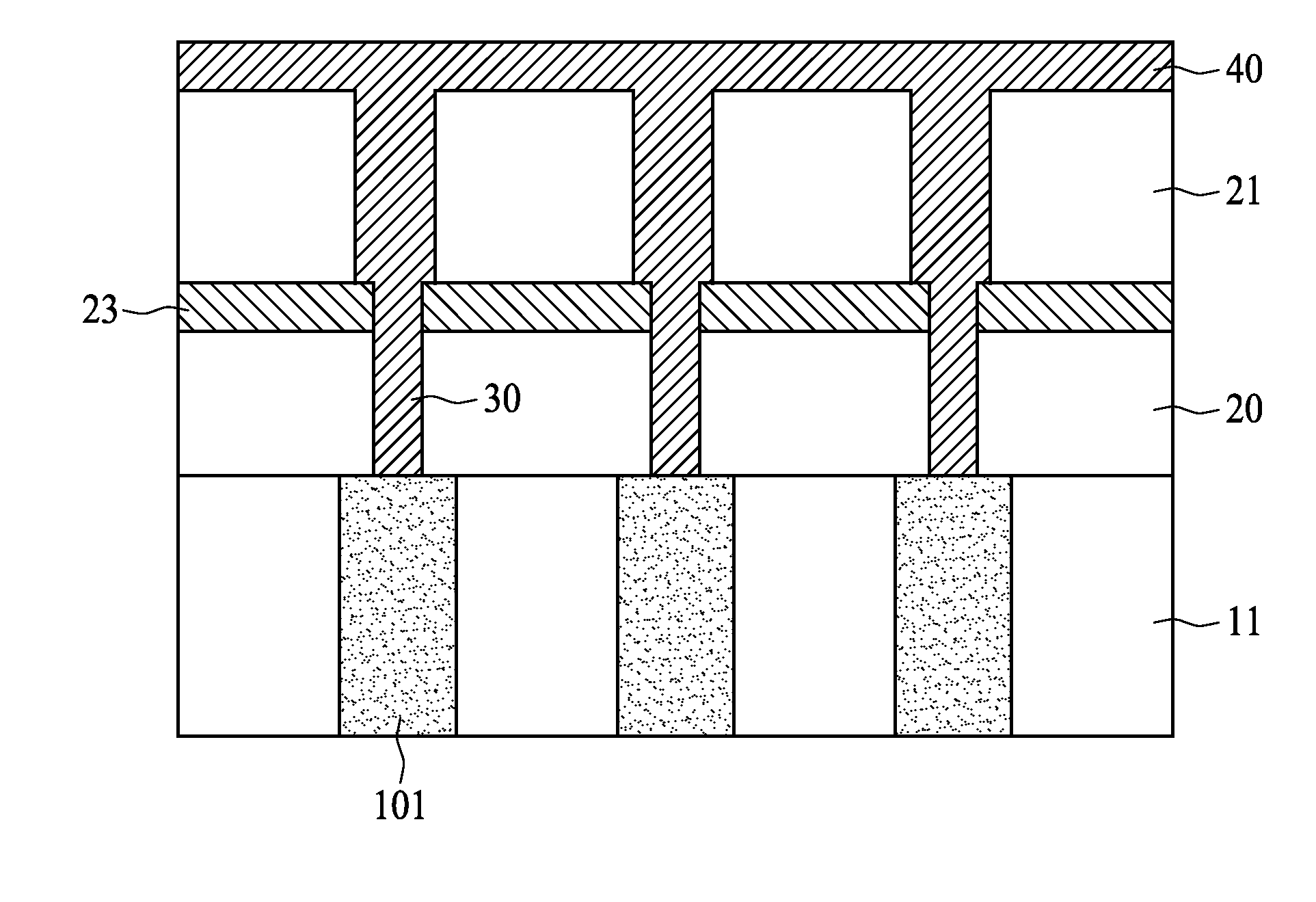

Polycrystalline ceramic substrate and method of manufacture

ActiveUS20180047557A1Relieve pressureIncrease the dislocation densityPolycrystalline material growthSolid-state devicesMetallurgyCeramic substrate

A method of fabricating a ceramic substrate structure includes providing a ceramic substrate, encapsulating the ceramic substrate in a barrier layer, and forming a bonding layer coupled to the barrier layer. The method further includes removing a portion of the bonding layer to expose at least a portion of the barrier layer and define fill regions, and depositing a second bonding layer on the at least a portion of the exposed barrier layer and the fill regions.

Owner:QROMIS INC

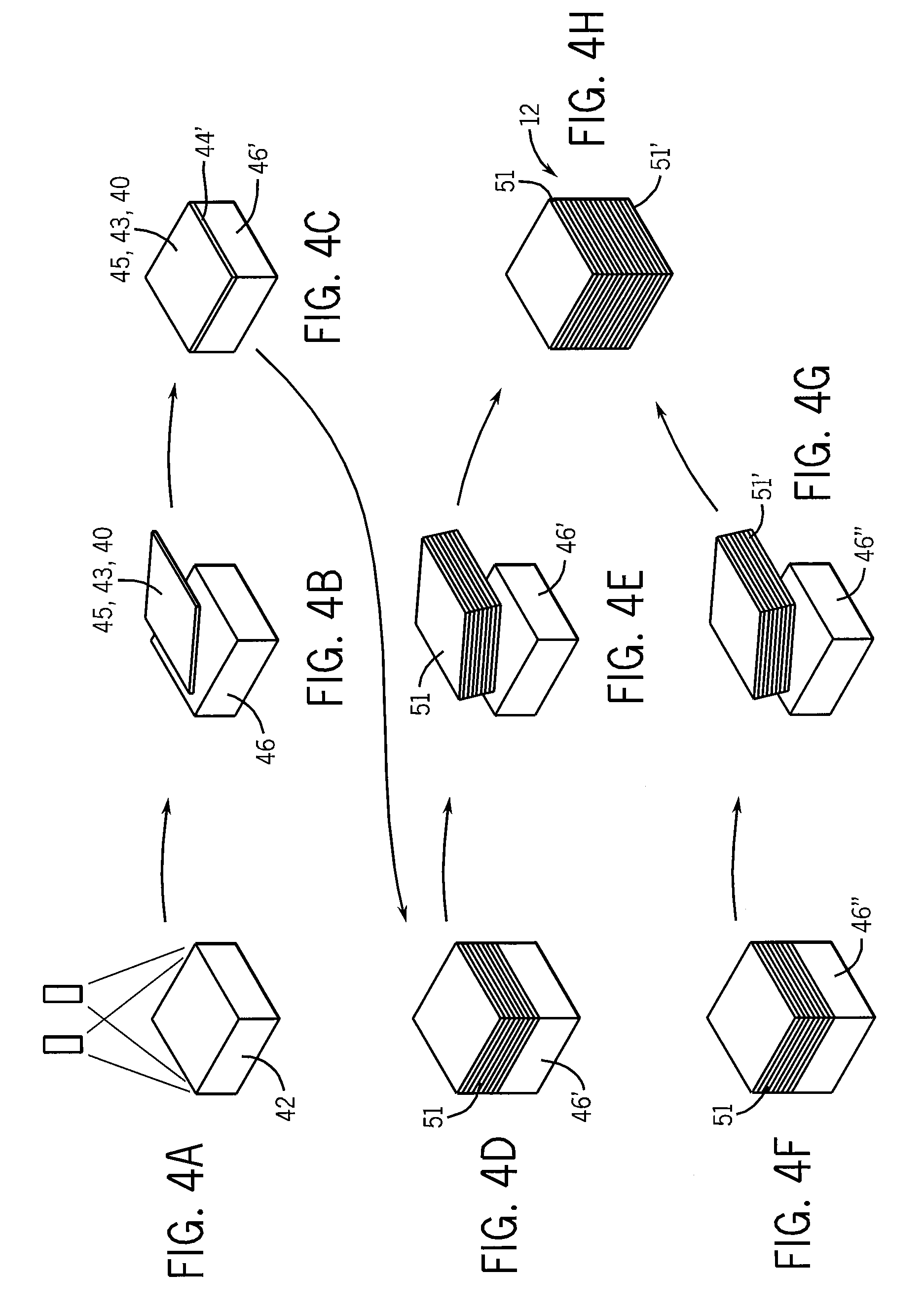

Robust modular electronic device without direct electrical connections for inter-module communication or control

ActiveUS7322863B2Improve protectionThe equipment is easy to operateTelevision system detailsSide-by-side/stacked arrangementsElectric power transmissionTransformer action

A modular electronic device where (predominantly) sealed modules are aligned and attached / connected in pre-determined sequences, forming a robust block-like structure with extendable function: Control and / or inter-module communication are implemented without direct electrical interconnect, by non-contact means such as (magnetic, inductive, light, infrared, radio frequency, sound, ultrasound, or other non-contact means). This device's inter-module power transfer may be with or without direct electrical contact, or devices may be internally powered. Power transfer through inductive / transformer action where one or more alignment pins are used as transformer core is one potential implementation. Modules may be fluid filled to facilitate cooling and / or crush resistance to high-pressure environments.

Owner:RAPP ROBERT

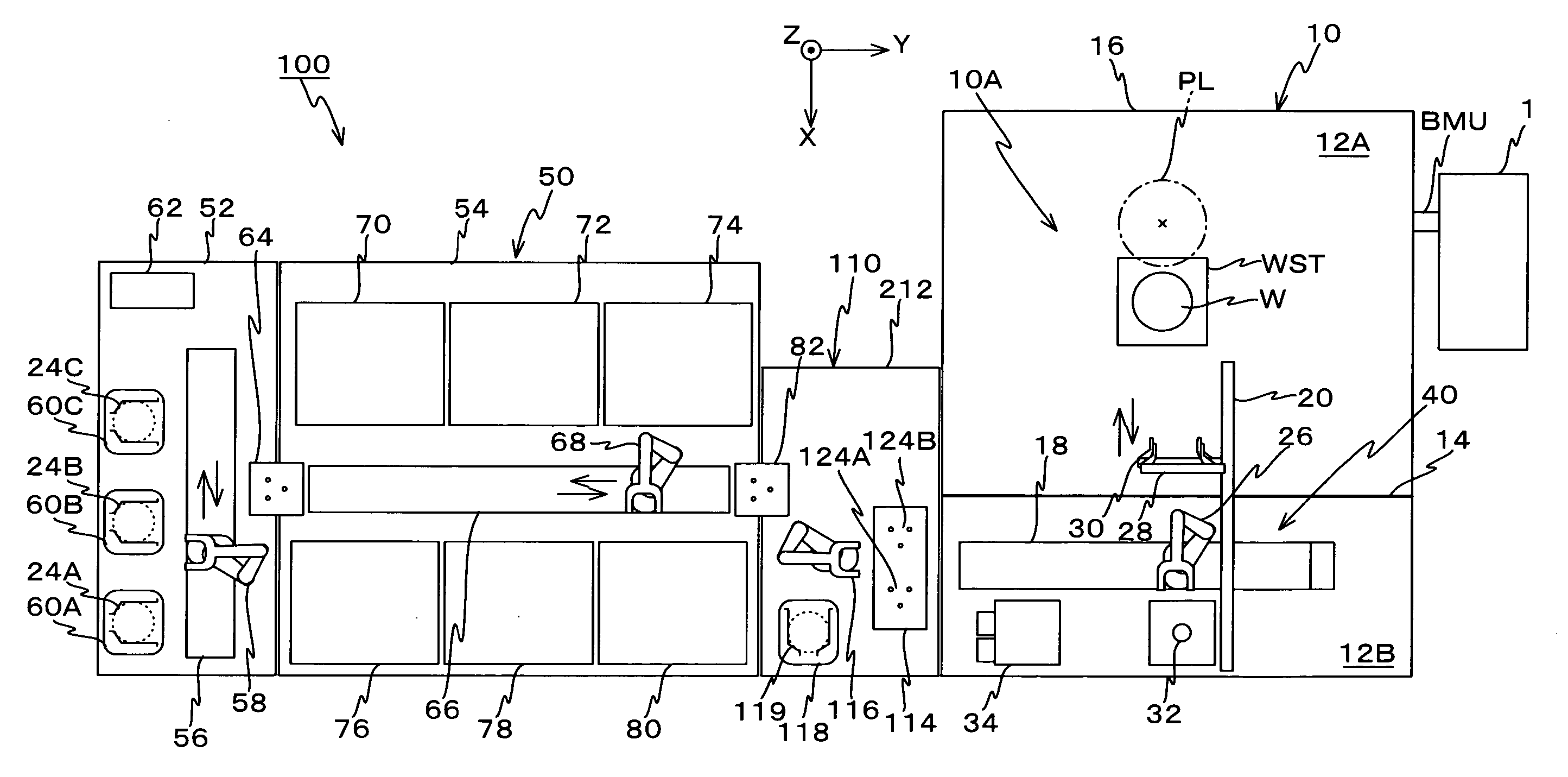

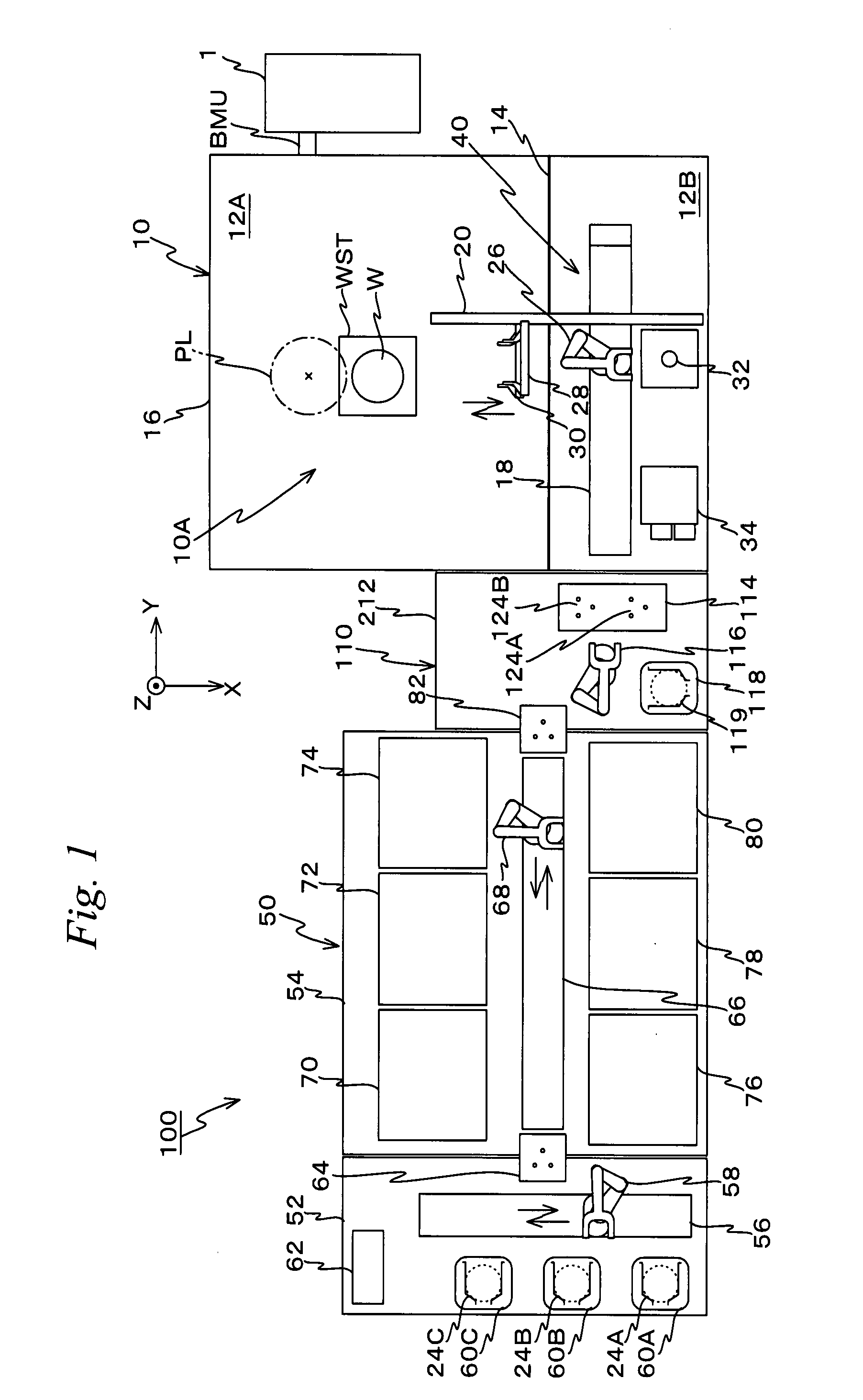

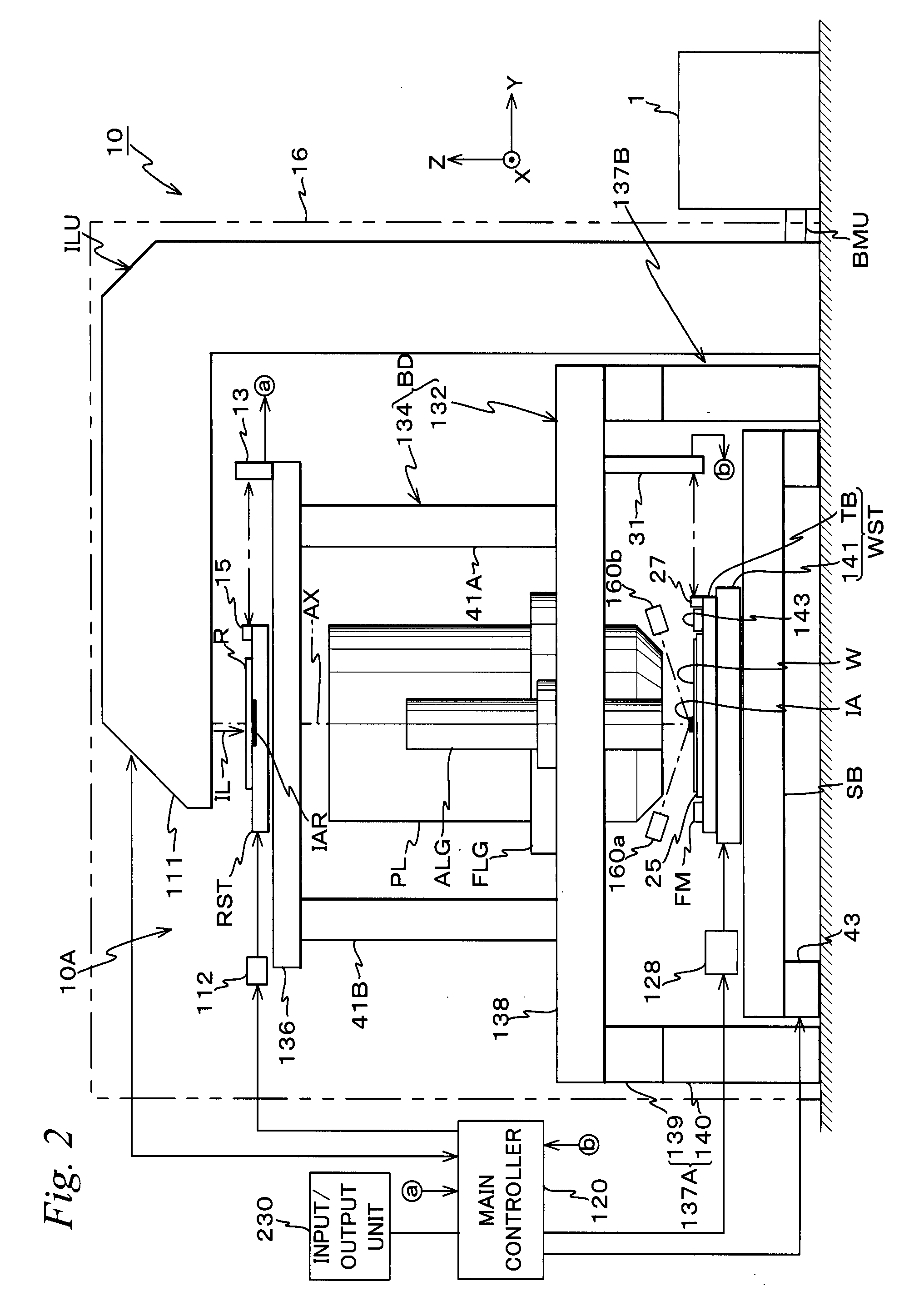

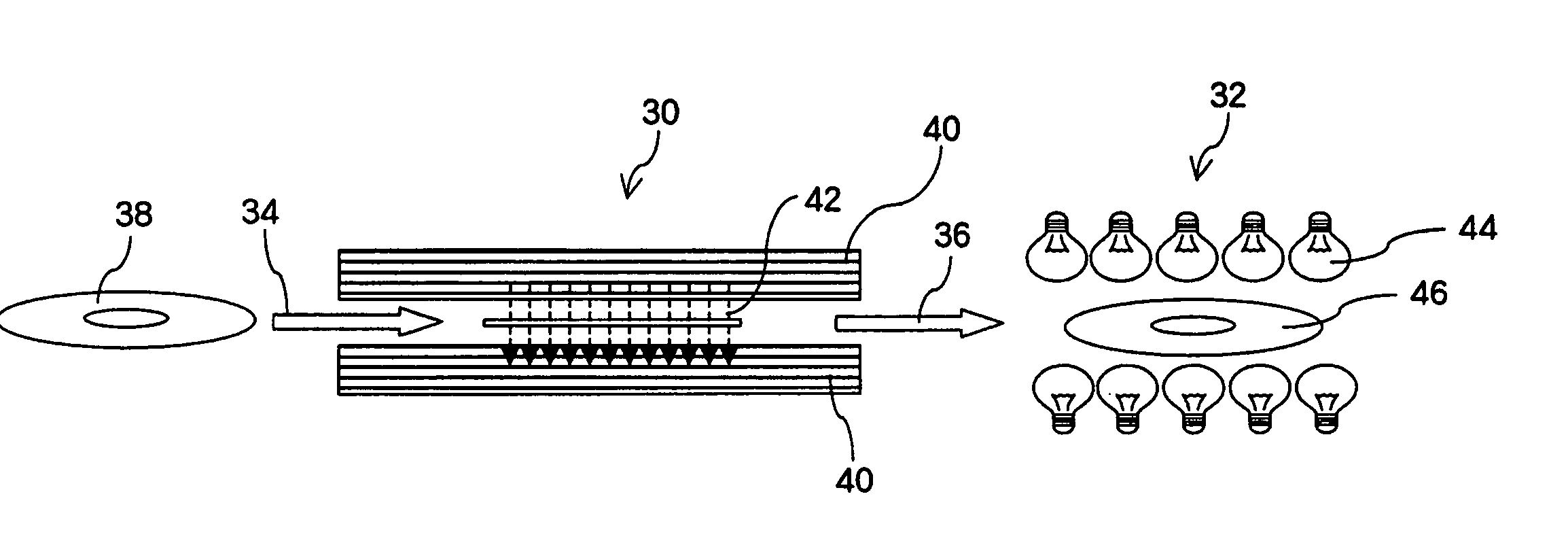

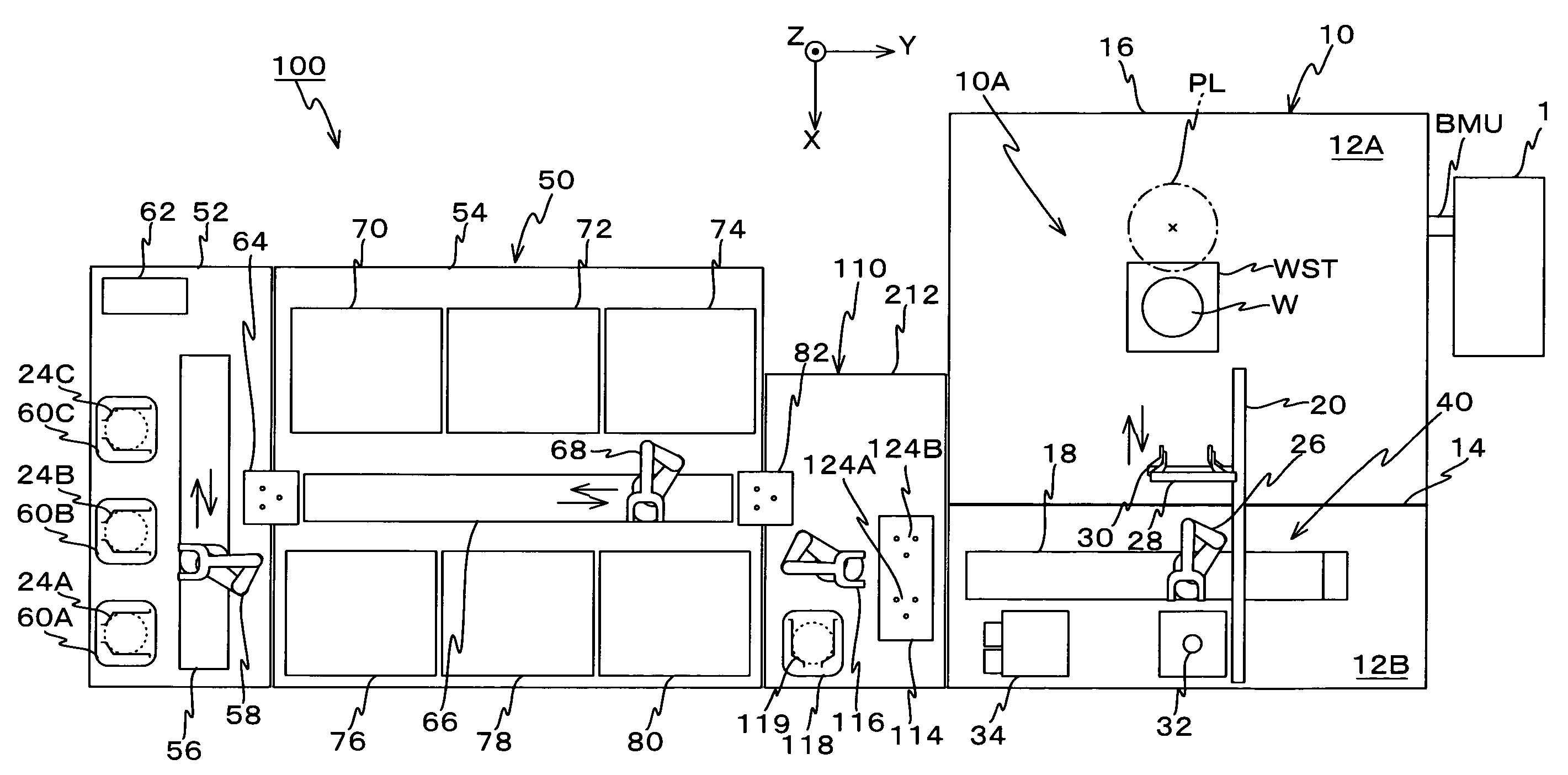

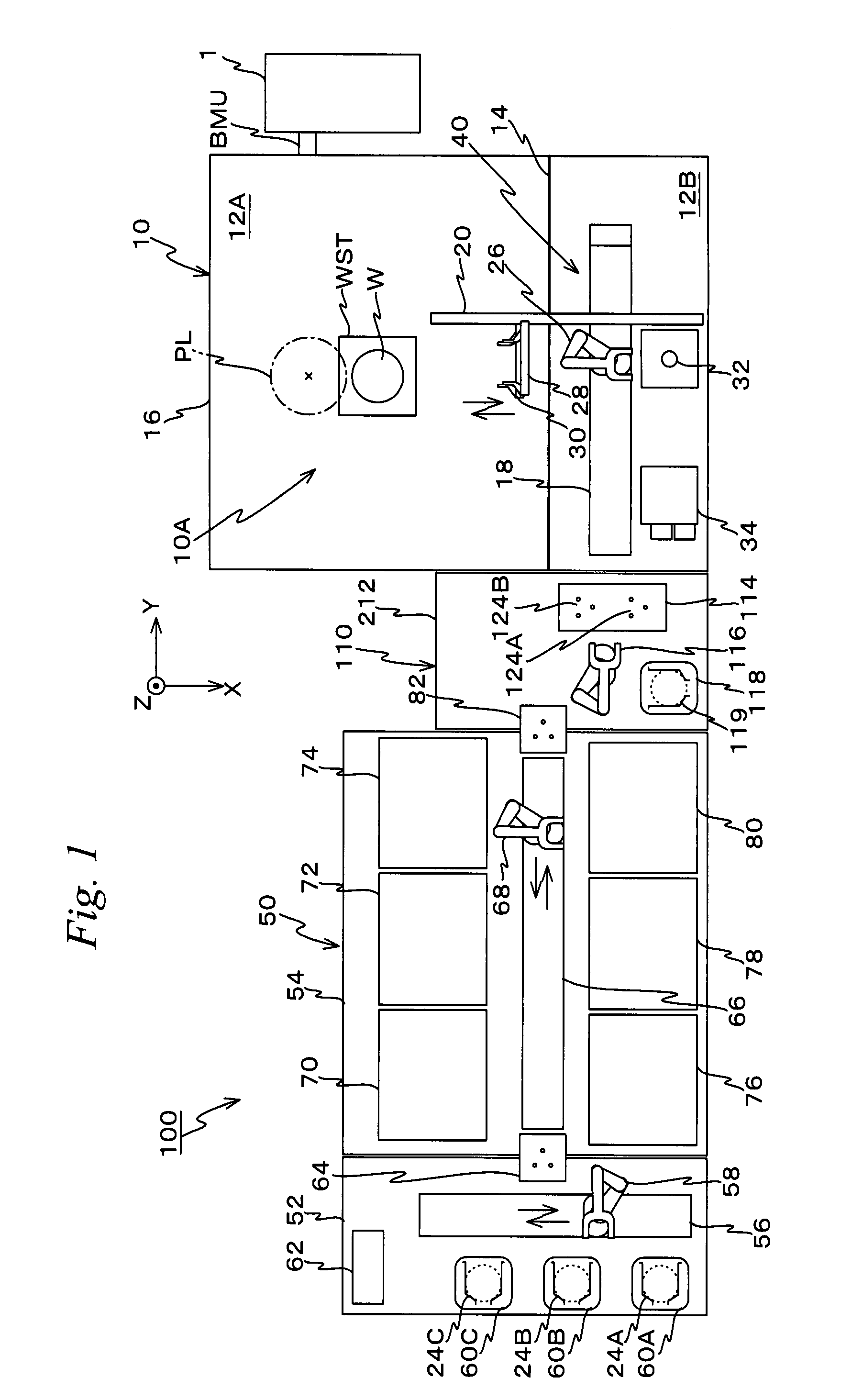

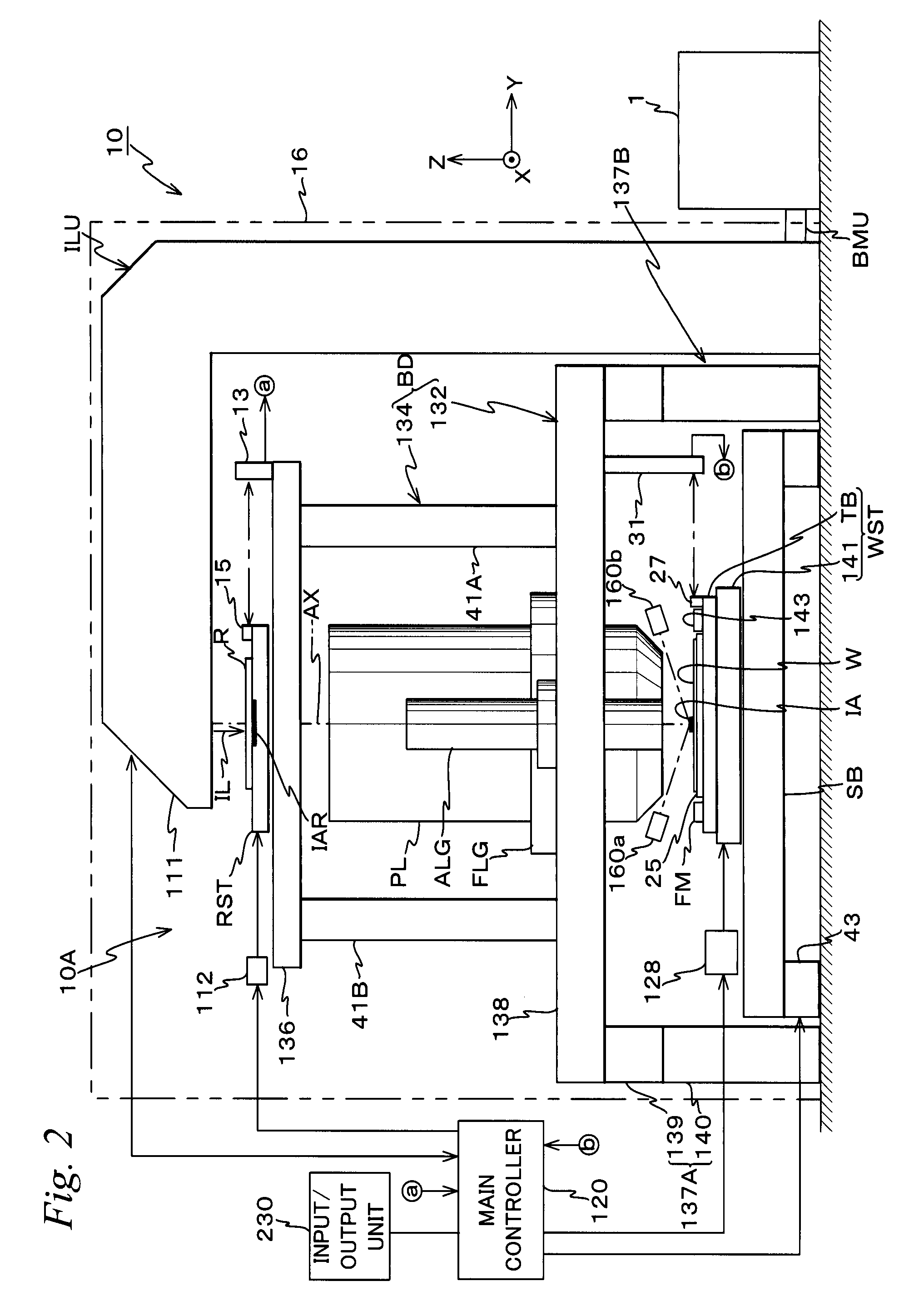

Exposure Apparatus, Operation Decision Method, Substrate Processing System, Maintenance Management Method, and Device Manufacuring Method

ActiveUS20070252966A1Improve productivityReduce equipment capacityLiquid processingPhotomechanical apparatusPrimary operationDowntime

An exposure apparatus is equipped with a main controller that decides an operation of the exposure apparatus based on information on maintenance from a C / D. Therefore, the main controller can decide to perform a specific operation, which is necessary for maintaining performance of the exposure apparatus and requires stop of the primary operation of the exposure apparatus, during maintenance of the C / D, that is, when the primary operation of the exposure apparatus has to be stopped by necessity, in parallel with the maintenance of the C / D. As a consequence, downtime of the exposure apparatus necessary for performing the specific operation can be decreased as a whole, which makes it possible to improve the operating rate without lowering apparatus performance of the exposure apparatus that is inline connected to a substrate processing apparatus.

Owner:NIKON CORP

Vertical semiconductor diode manufactured with an engineered substrate

ActiveUS20180061630A1Relieve pressureIncrease the dislocation densityPolycrystalline material growthSolid-state devicesSingle crystalGallium nitride

A semiconductor diode includes an engineered substrate including a substantially single crystal layer, a buffer layer coupled to the substantially single crystal layer, and a semi-insulating layer coupled to the buffer layer. The semiconductor diode also includes a first N-type gallium nitride layer coupled to the semi-insulating layer and a second N-type gallium nitride layer coupled to the first N-type gallium nitride layer. The first N-type gallium nitride layer has a first doping concentration and the second N-type gallium nitride layer has a second doping concentration less than the first doping concentration. The semiconductor diode further includes a P-type gallium nitride layer coupled to the second N-type gallium nitride layer, an anode contact coupled to the P-type gallium nitride layer, and a cathode contact coupled to a portion of the first N-type gallium nitride layer.

Owner:QROMIS INC

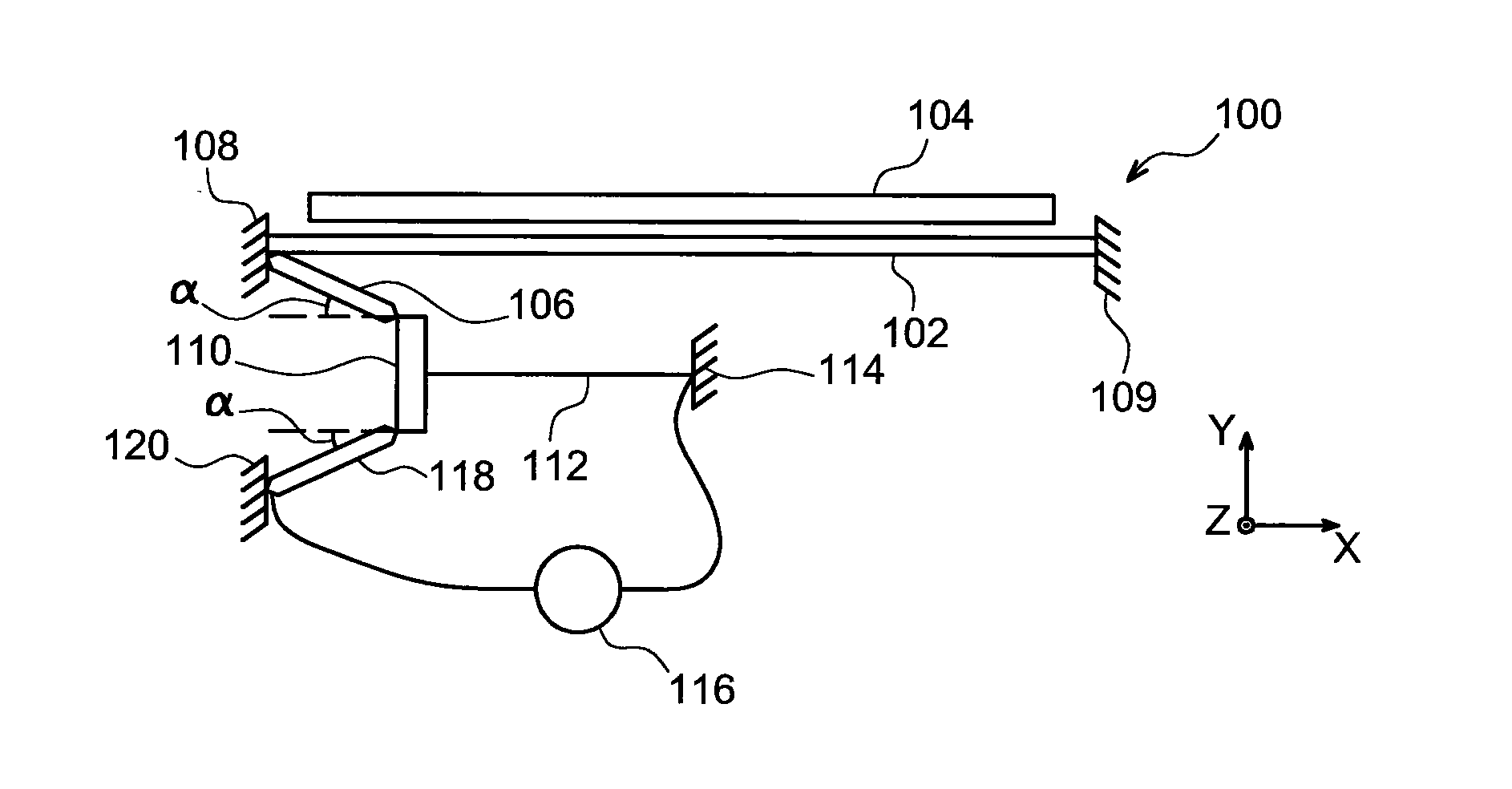

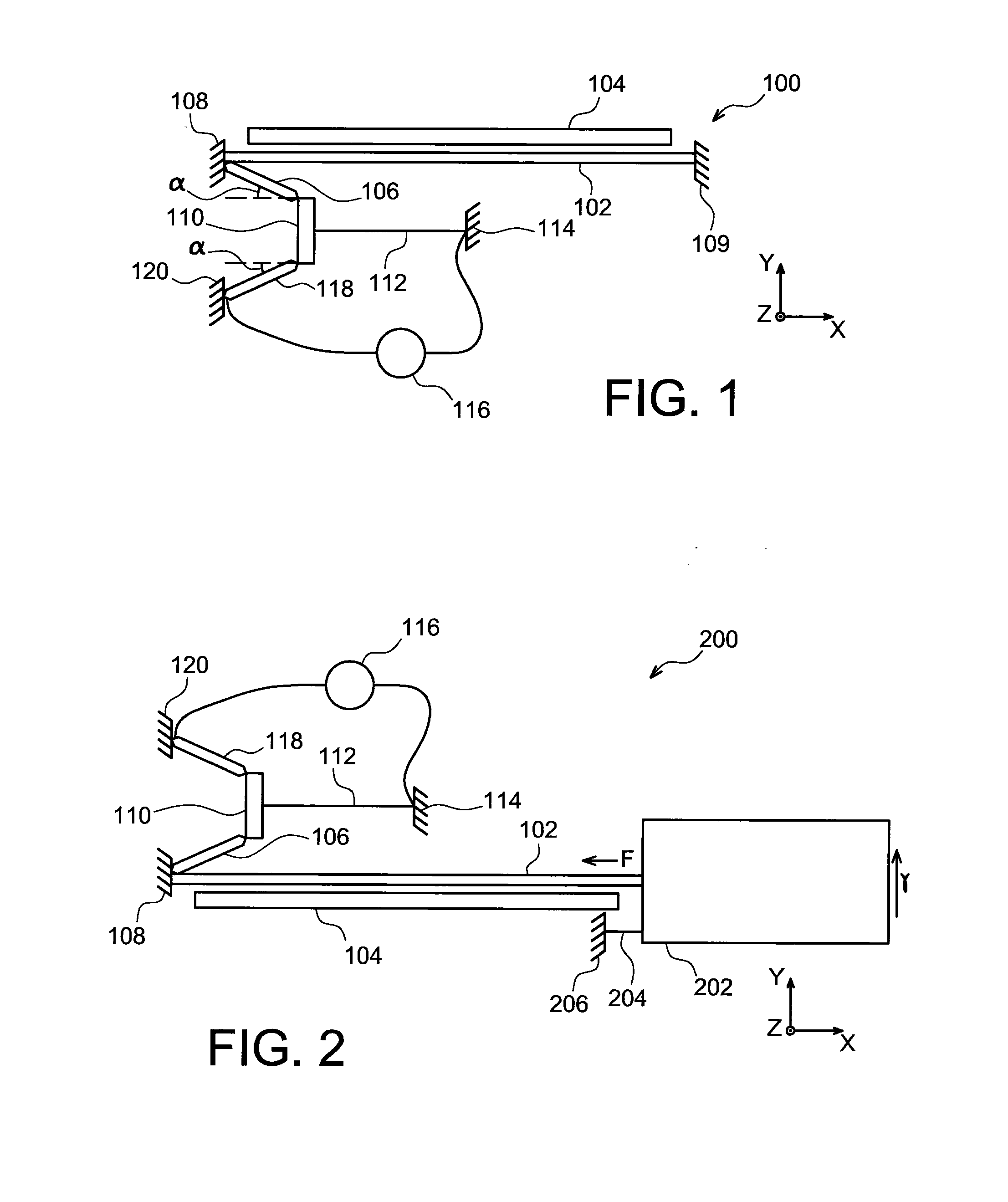

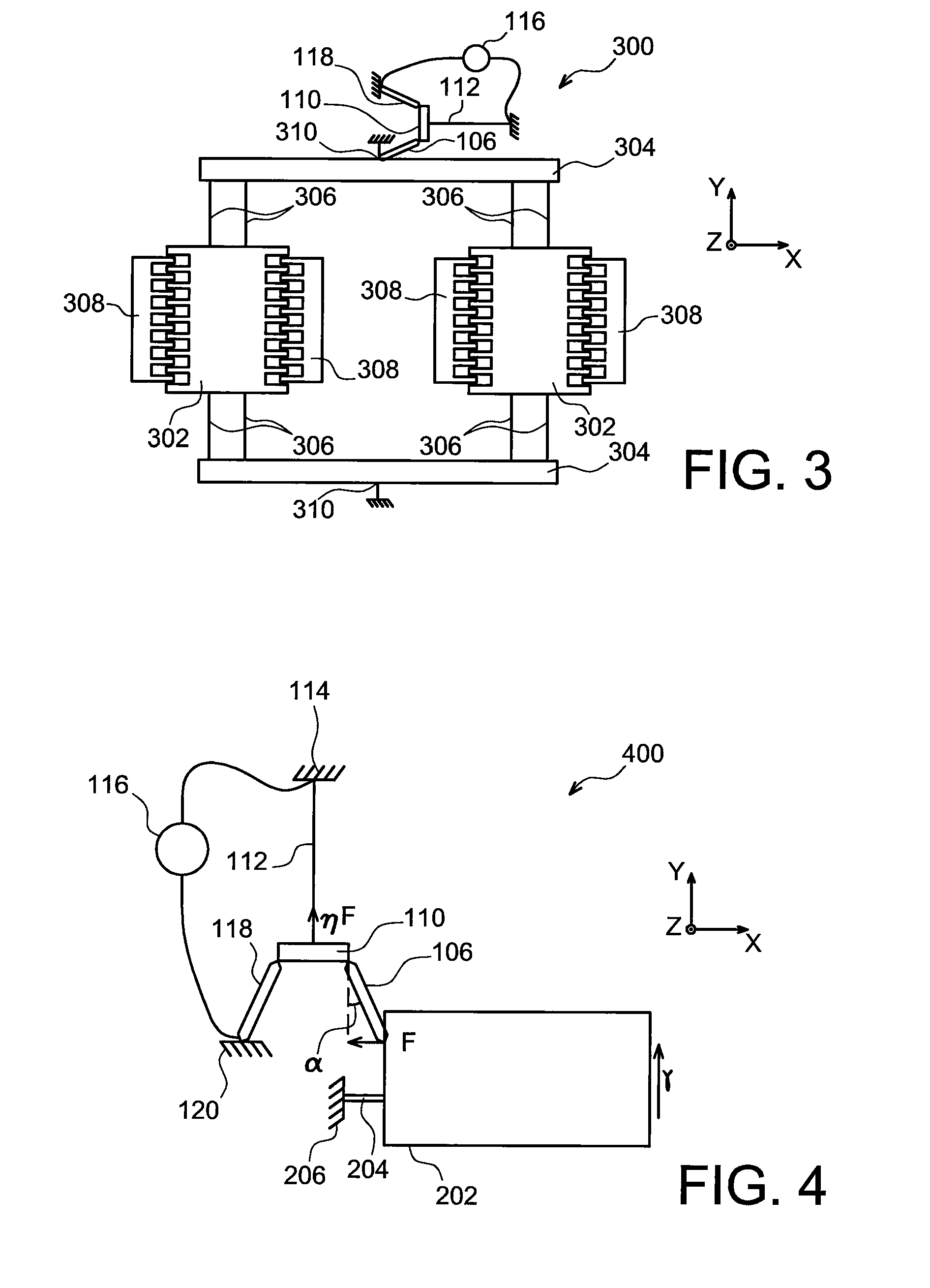

Device with detection by suspended piezoresistive strain gauge comprising a strain amplifier cell

InactiveUS20090139342A1High sensitivityEasy to implementMaterial strength using tensile/compressive forcesAcceleration measurementEngineeringStrain gauge

A device, with piezoresistive detection comprising at least:a proof body on which an effort to be measured is exerted,means of detecting a strain exerted by the proof body under the action of the effort, comprising at least one suspended piezoresistive strain gauge,a strain amplifier cell comprising at least two rigid arms mechanically linked to each other by at least one link element at the level of a first of their ends, a second end of a first of the two rigid arms being mechanically linked to the proof body, a second end of a second of the two rigid arms being fixed to the substrate, the link element being mechanically linked to a first end of the suspended piezoresistive strain gauge.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

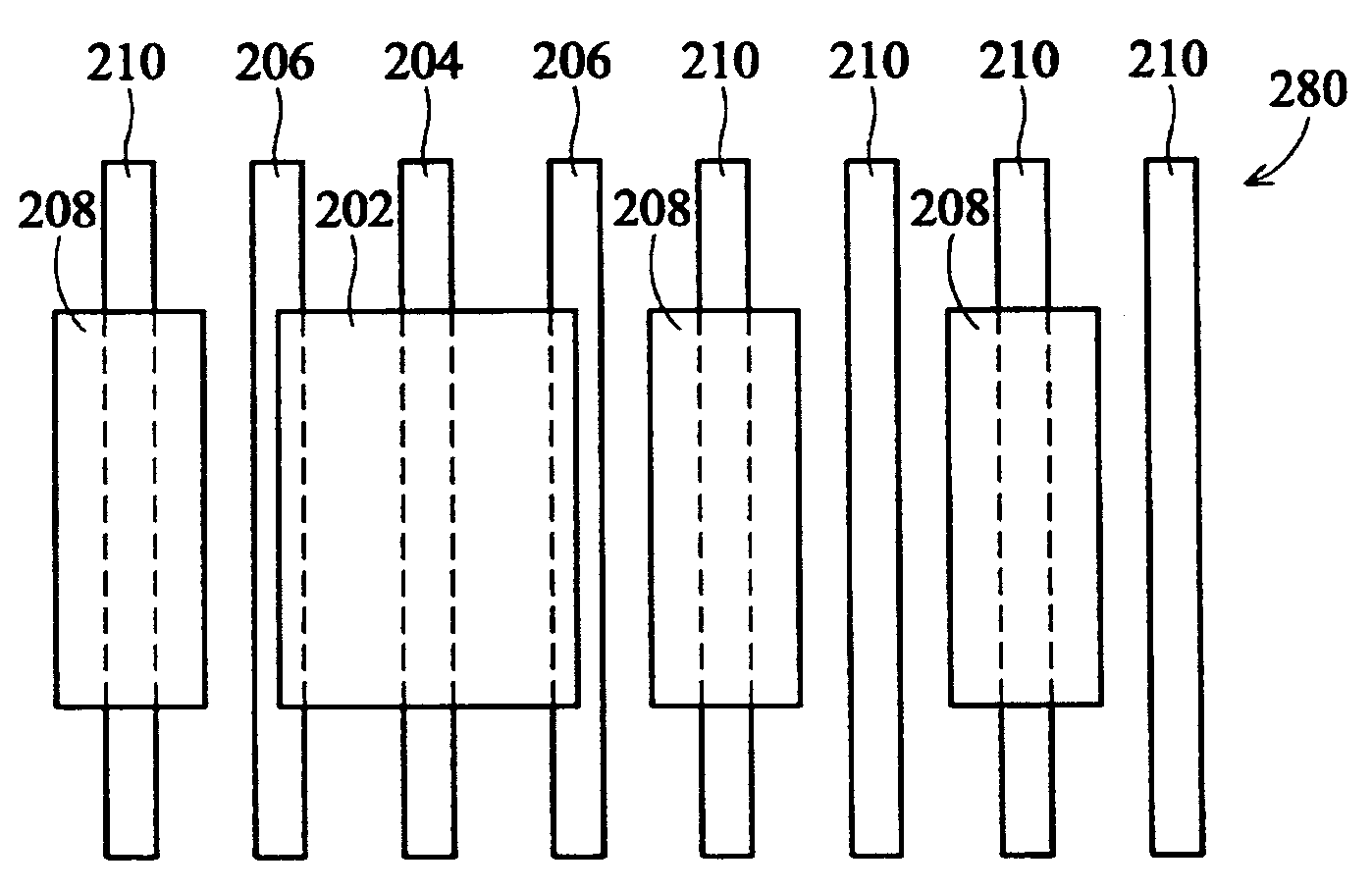

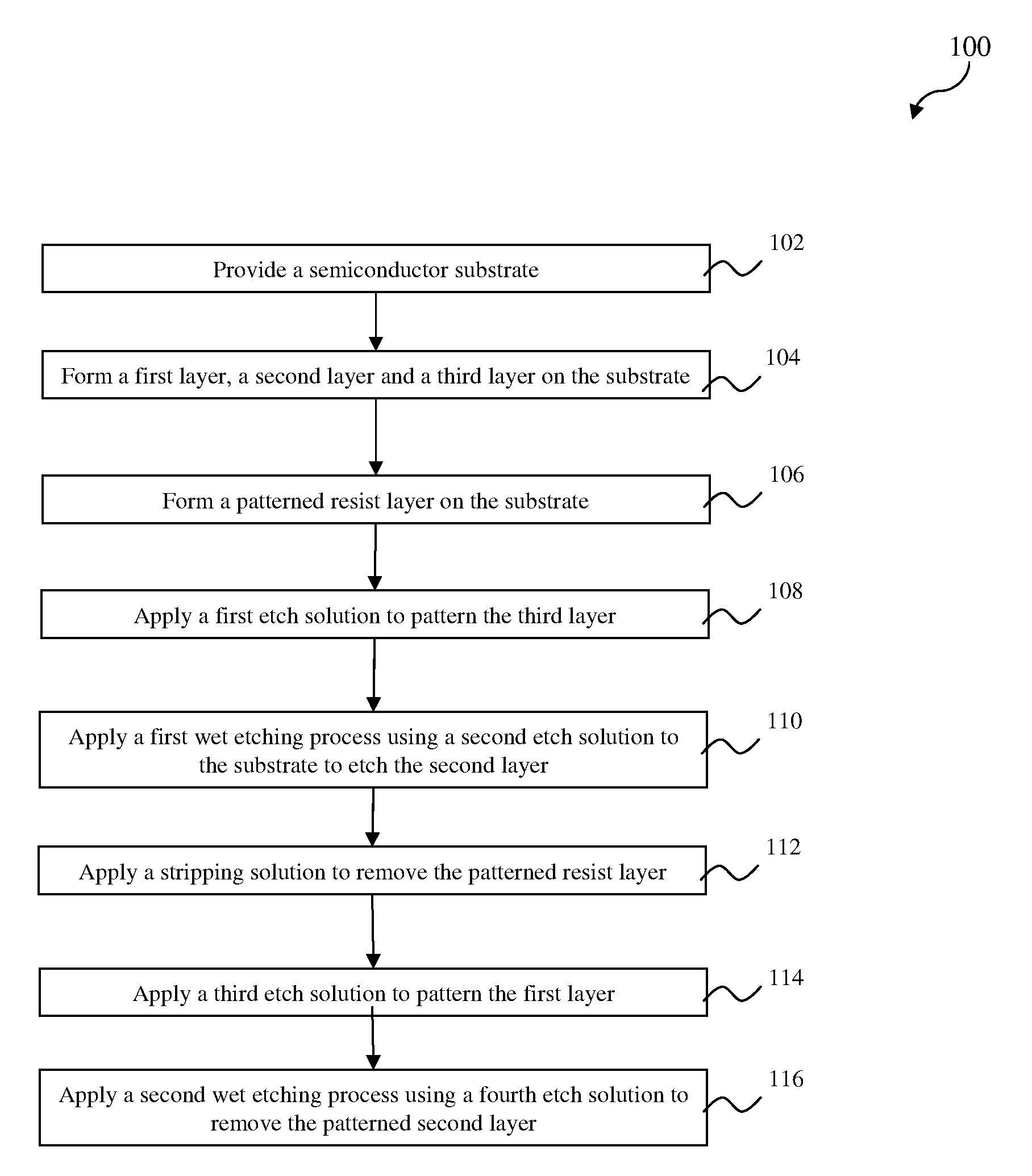

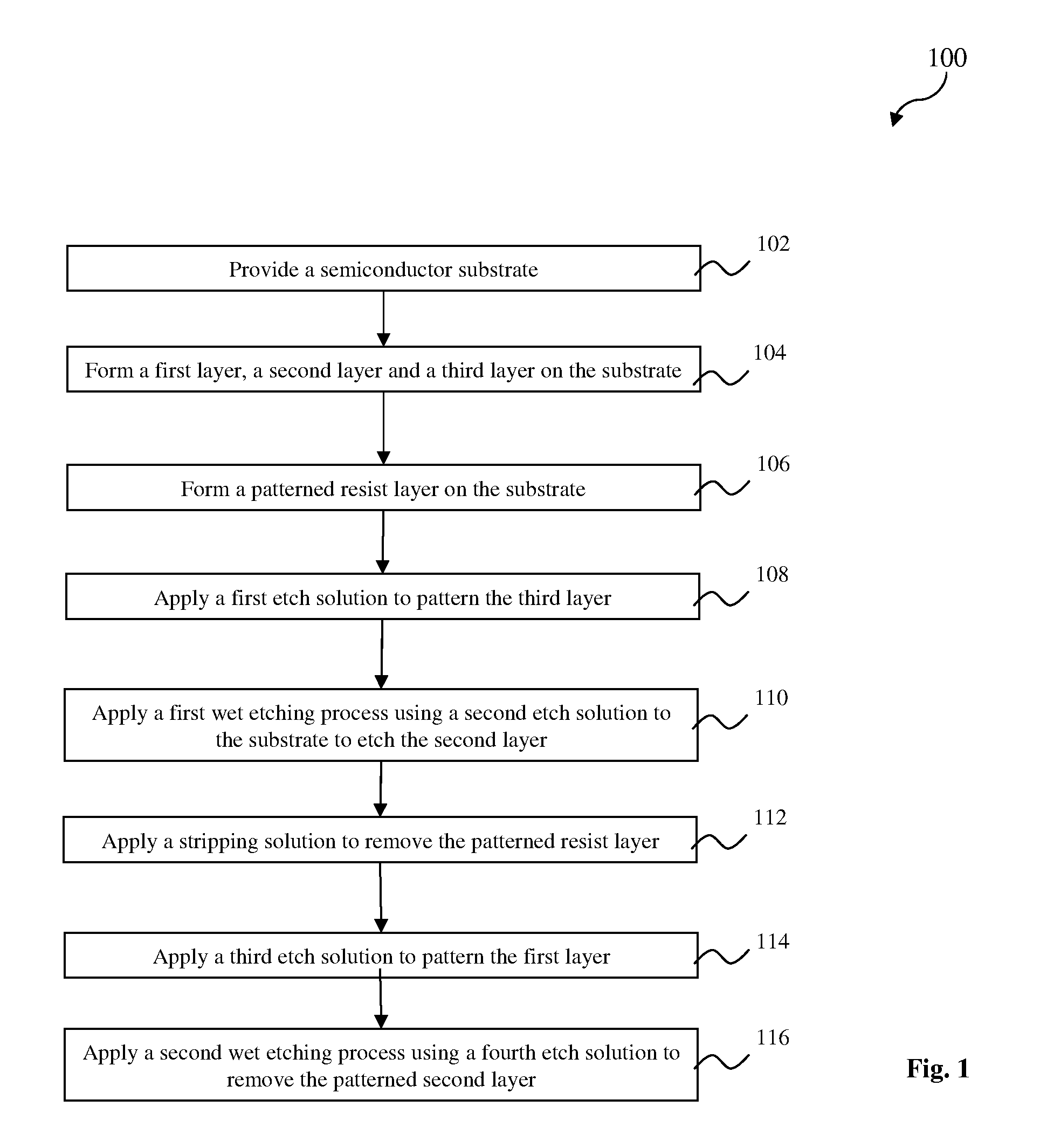

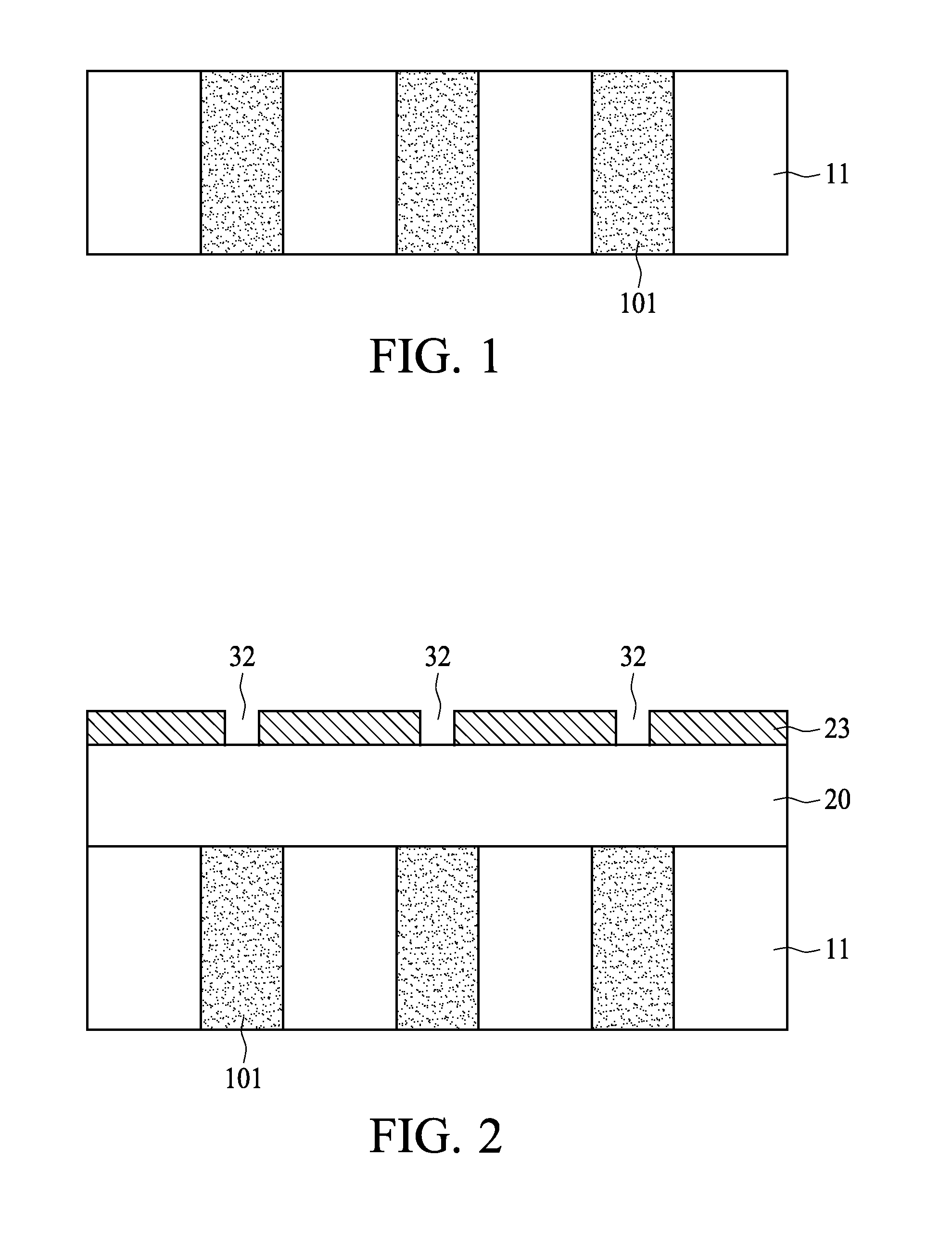

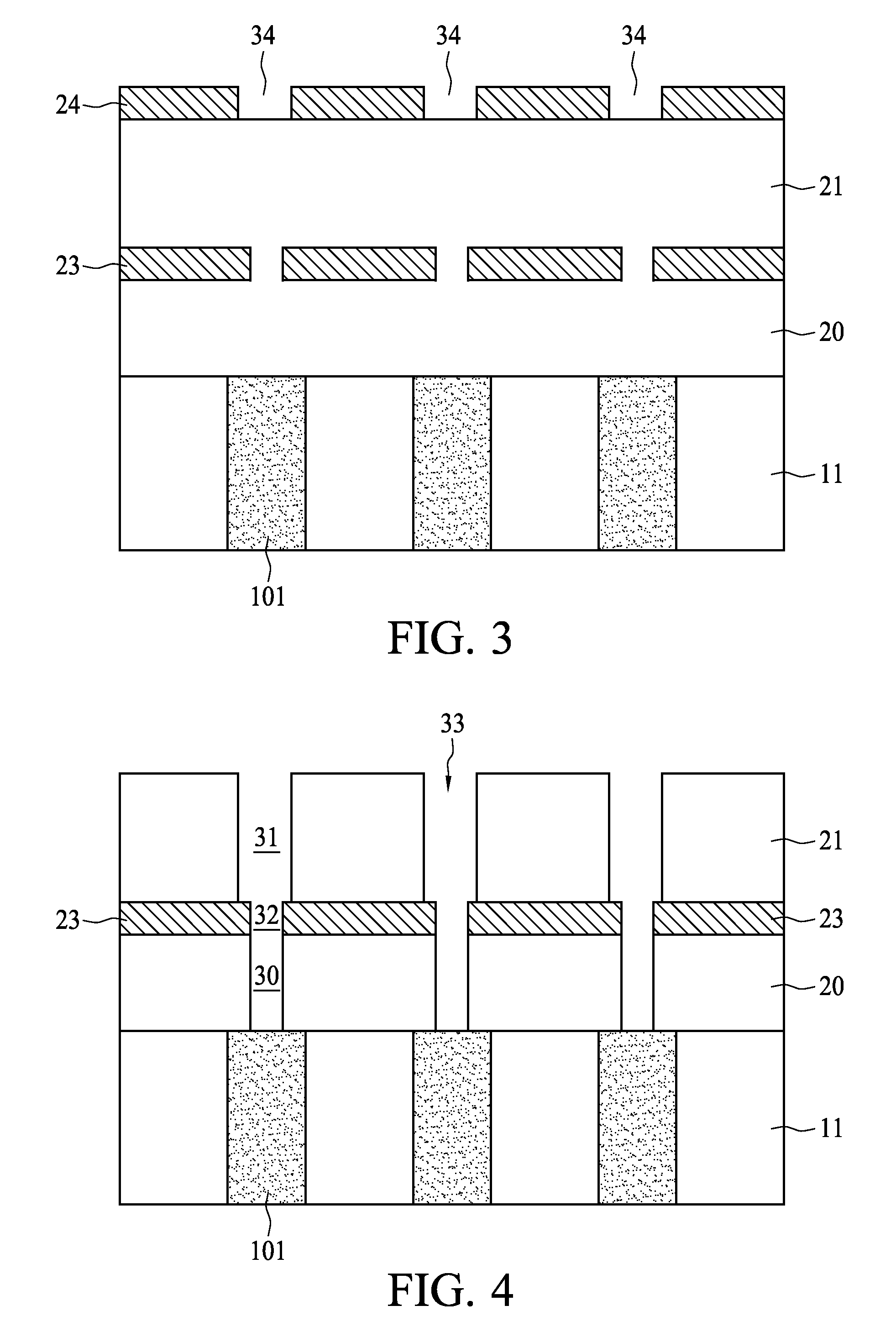

Method for forming a sacrificial sandwich structure

InactiveUS20100068874A1Reduce equipment capacitySemiconductor/solid-state device manufacturingSemiconductor devicesResistEtching

The present disclosure provides a method for making a semiconductor device. The method includes forming a first material layer on a substrate; forming a second material layer on the first material layer; forming a sacrificial layer on the second material layer; forming a patterned resist layer on the sacrificial layer; applying a first wet etching process using a first etch solution to the substrate to pattern the sacrificial layer using the patterned resist layer as a mask, resulting in a patterned sacrificial layer; applying an ammonia hydroxide-hydrogen peroxide-water mixture (APM) solution to the substrate to pattern the second material layer, resulting in a patterned second material layer; applying a second wet etching process using a second etch solution to the substrate to pattern the first material layer; and applying a third wet etching process using a third etch solution to remove the patterned sacrificial layer.

Owner:TAIWAN SEMICON MFG CO LTD

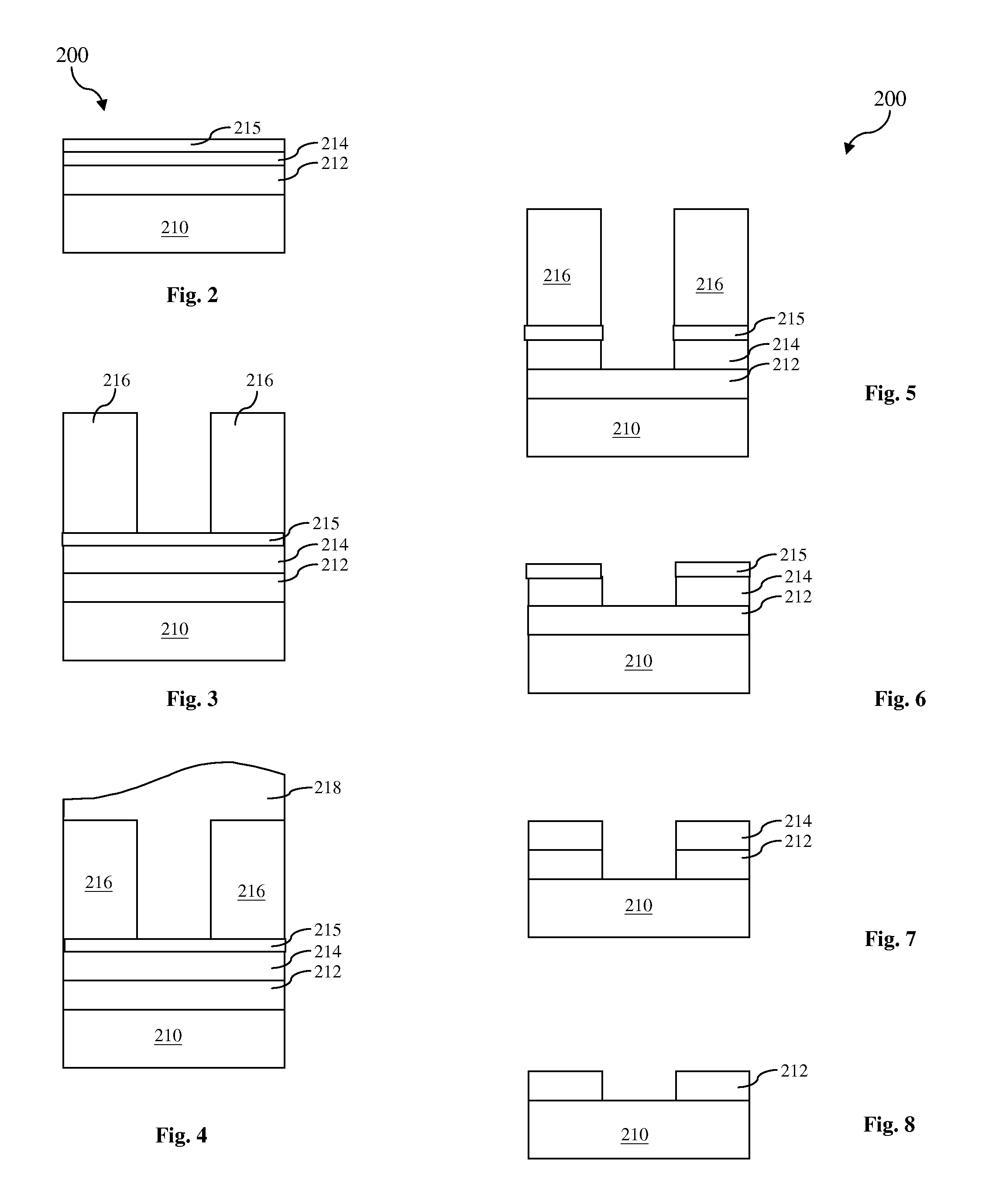

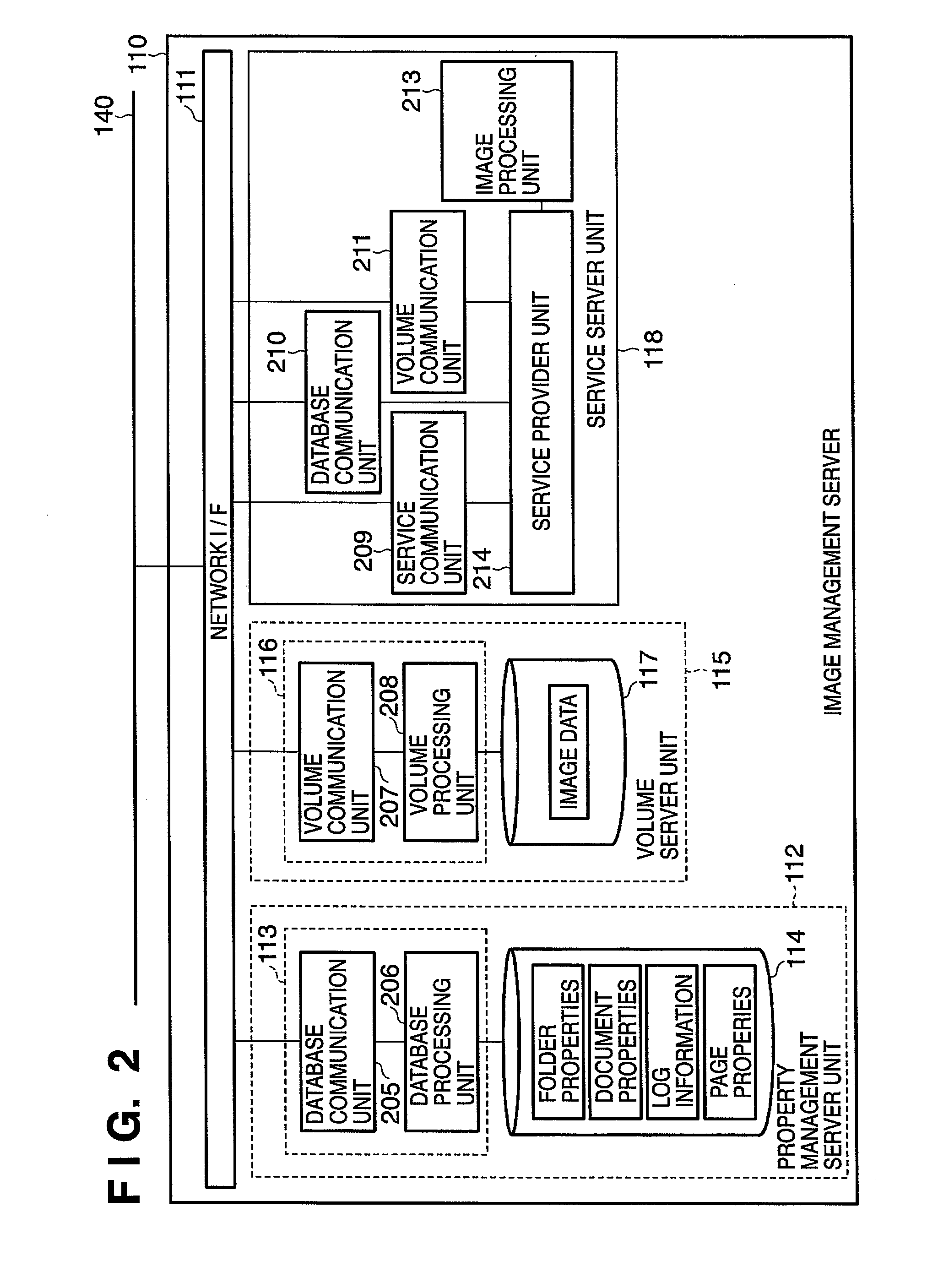

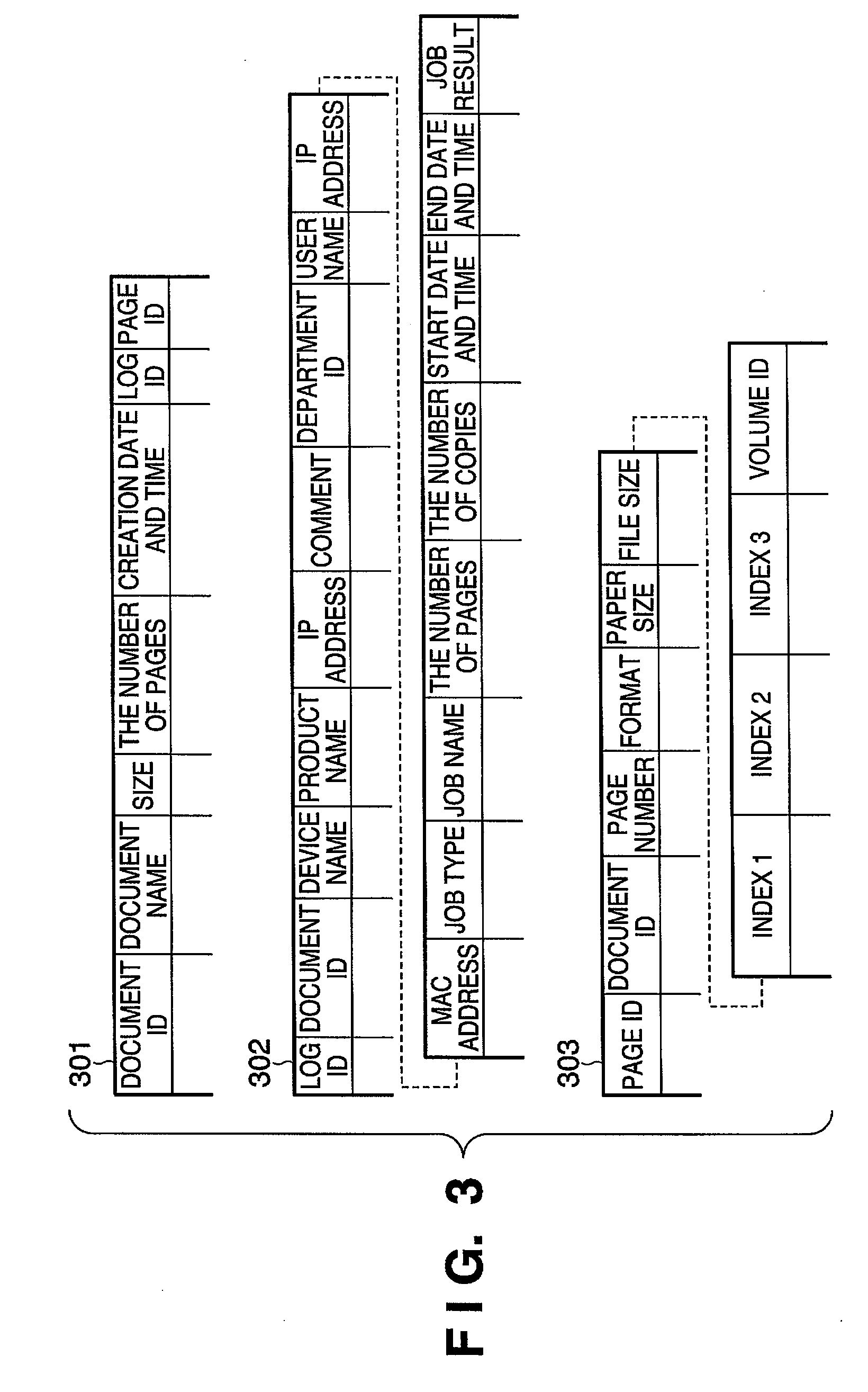

Image processing system, image processing apparatus, and image processing method

InactiveUS20080212136A1Reduce equipment capacityReduce capacityDigital data processing detailsAnalogue secracy/subscription systemsDigital watermarkingImage based

In a digital multi-function peripheral, image data to be output and first log information are generated based on an image forming job. Second log information embedded as digital watermark information is detected from the image data, and the reliability of the digital watermark information is computed. If the reliability is high, the first log information is held in a property storage unit 114 in an image management server 110. If the reliability is low, the first log information is held in the property storage unit 114 and the image data is held in a volume storage unit.

Owner:CANON KK

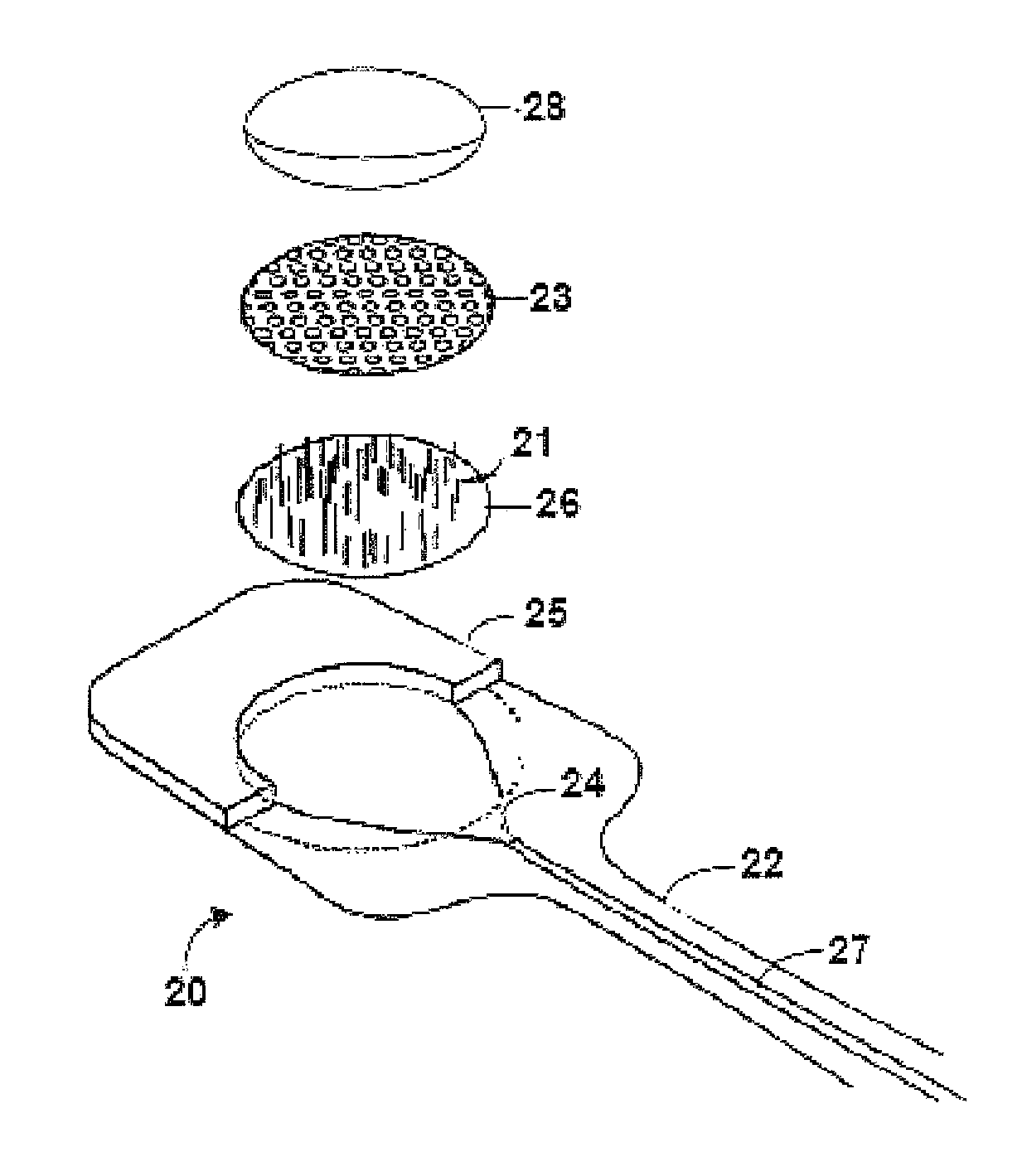

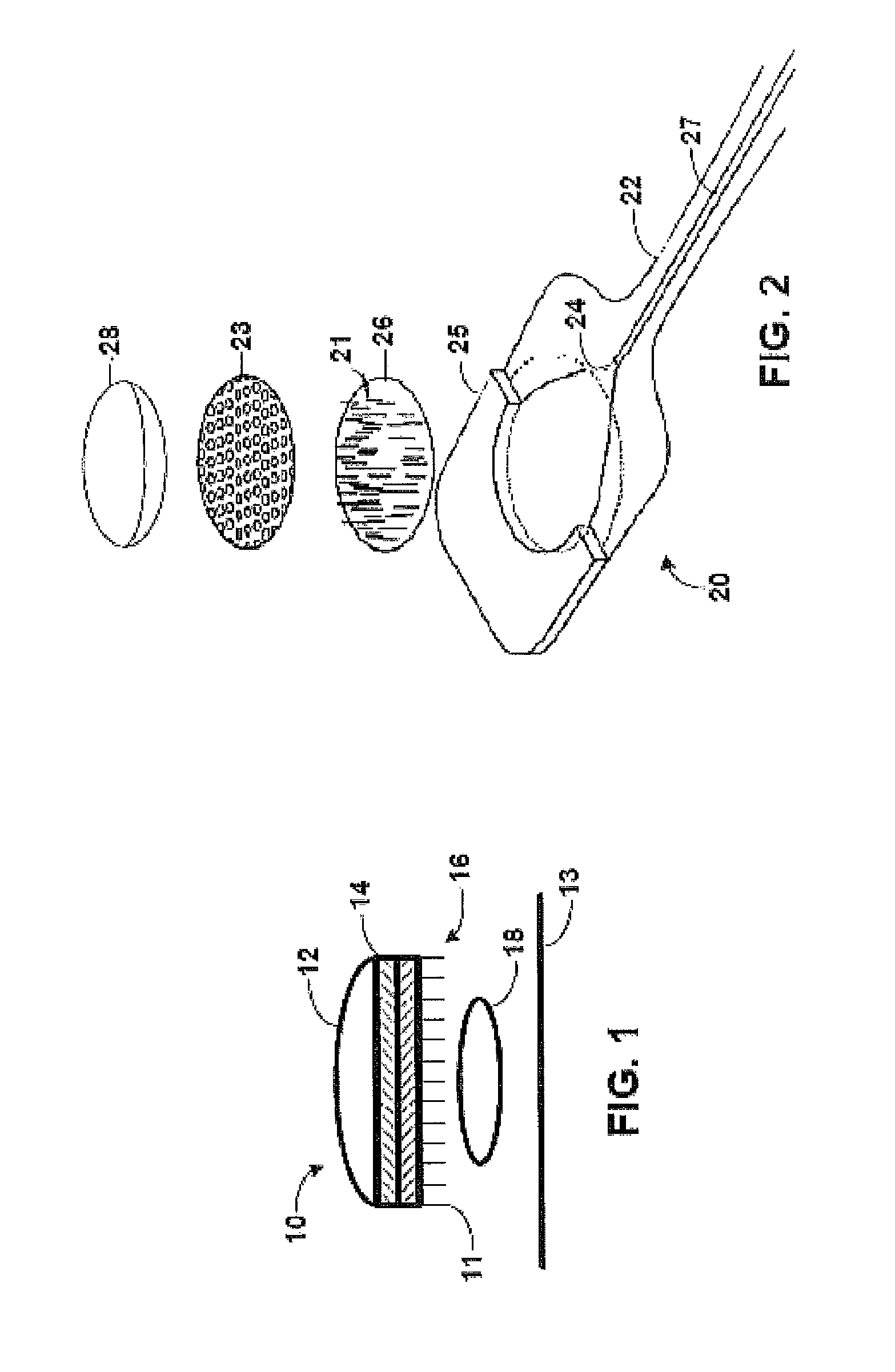

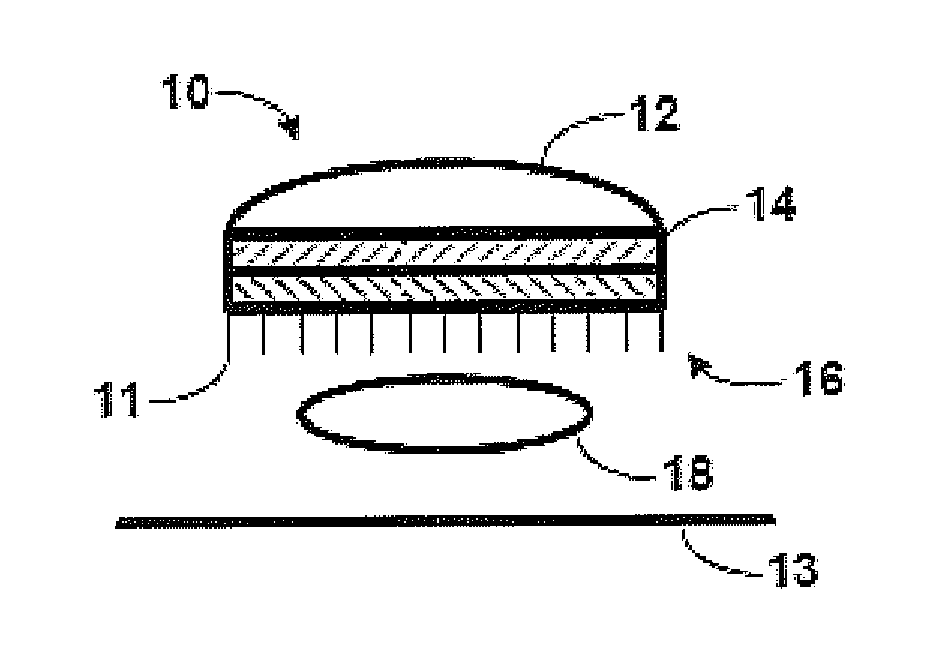

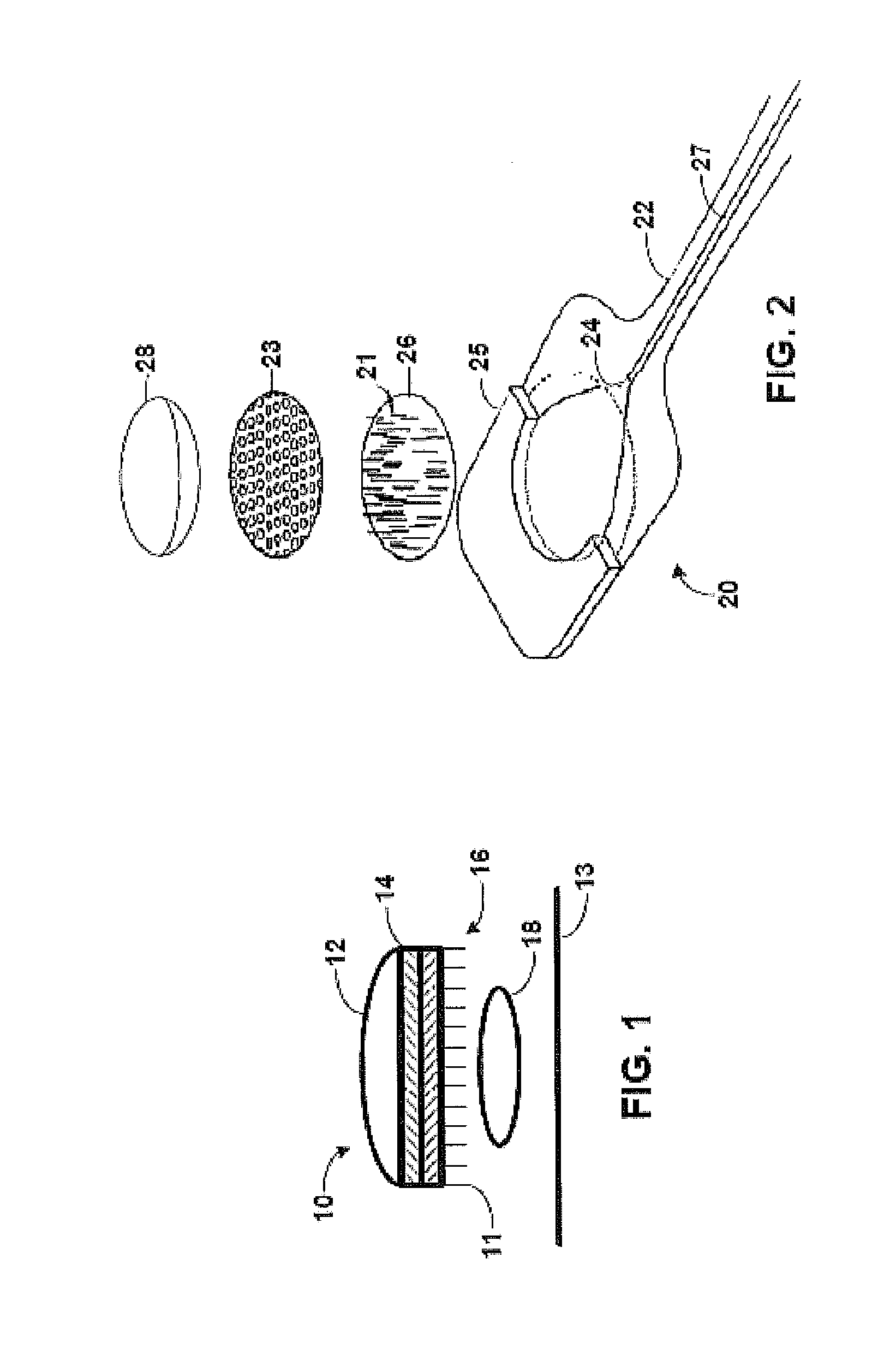

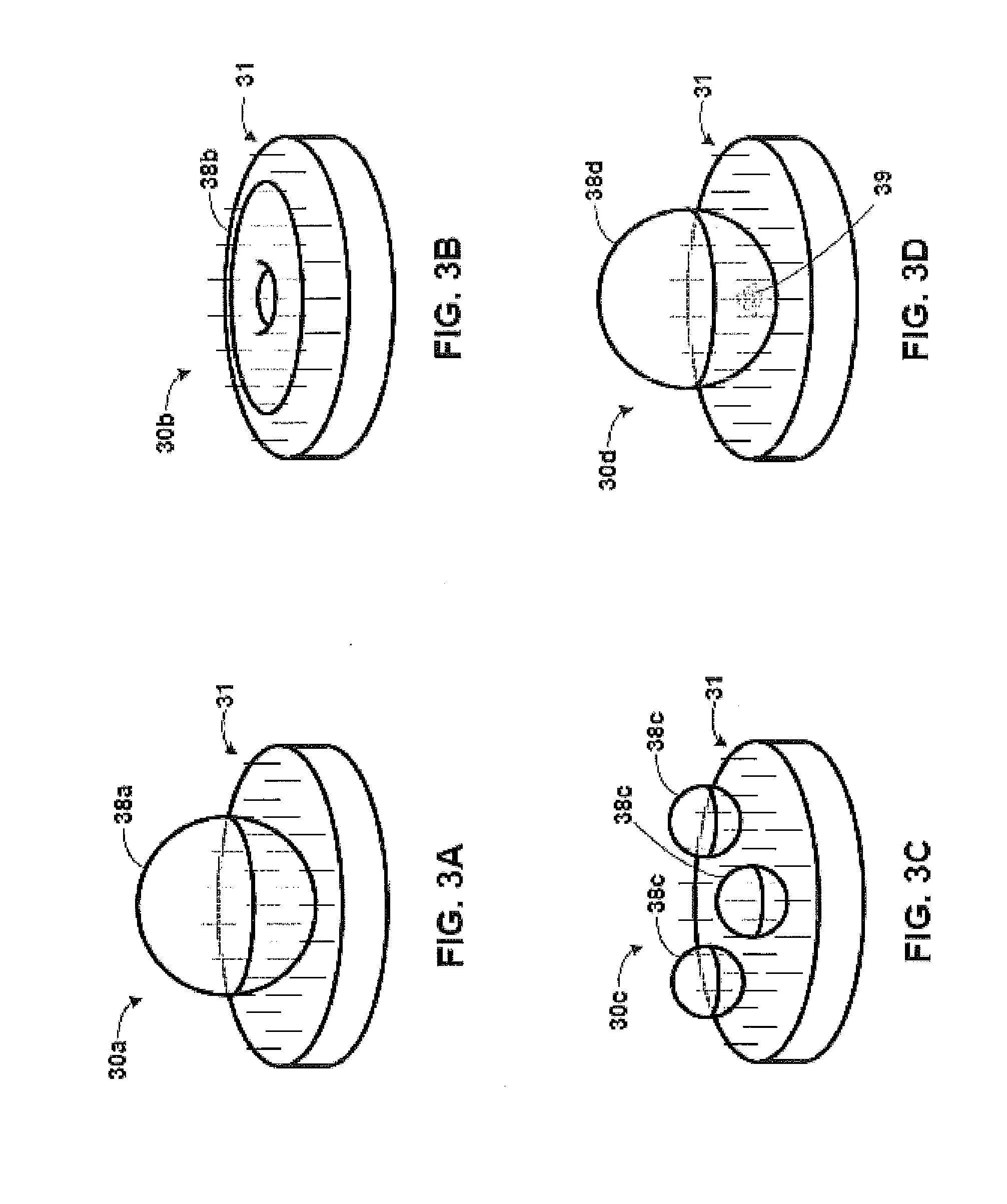

Device with encapsulated gel

ActiveUS8805470B2Simple interfaceReduce equipment capacityElectroencephalographySensorsBiomedical engineeringMedical treatment

Apparatus and techniques are provided for interfacing a device with a surface. The apparatus and techniques provide gel encapsulation and isolation mechanisms to extend the shelf-life of the preparation devices, allow for the use of more effective materials, and improve the quality of the contact between a device and an application surface. Particular embodiments of these apparatus and techniques suitable for use in medical contexts are also provided.

Owner:TYCO HEALTHCARE GRP LP

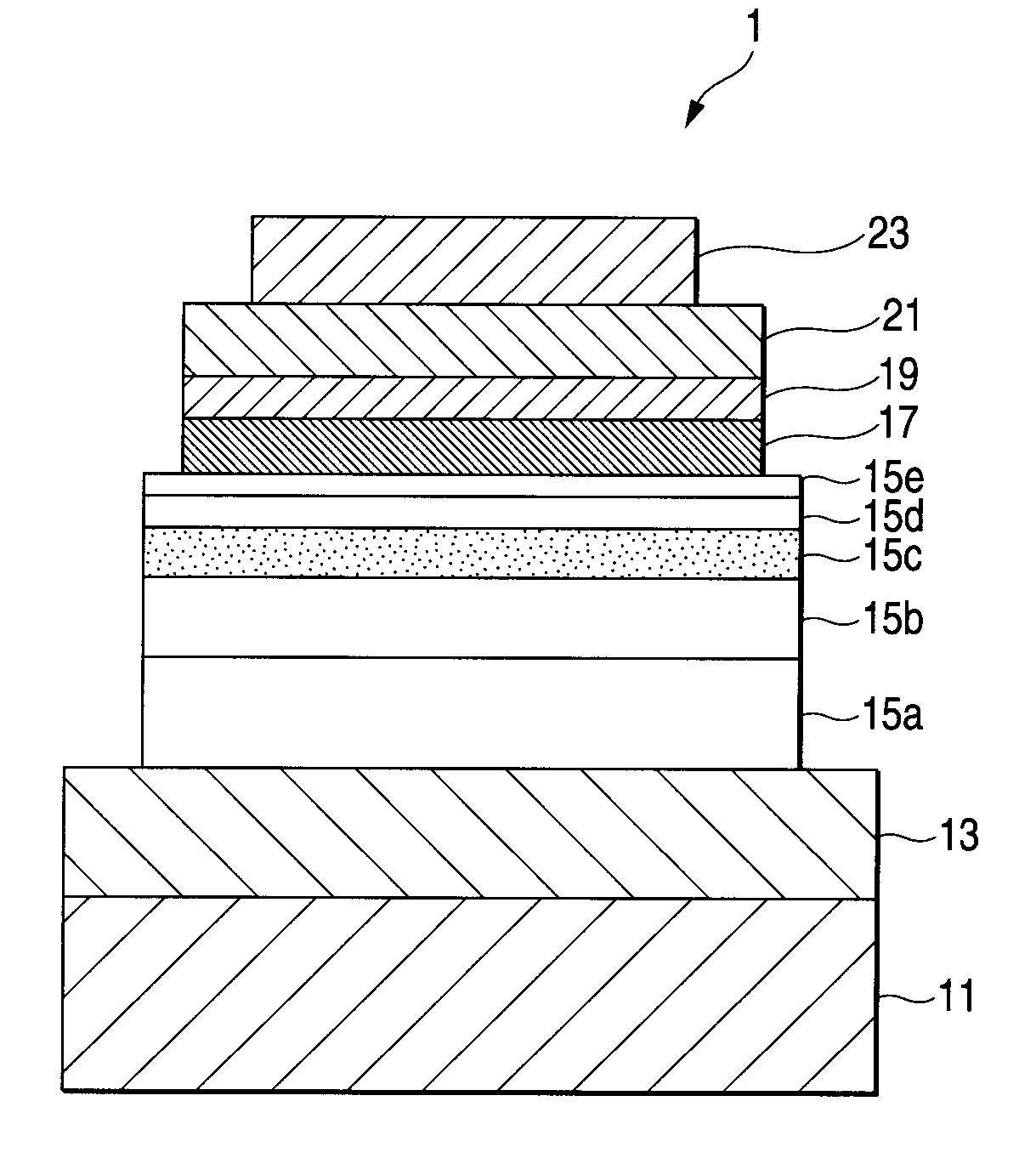

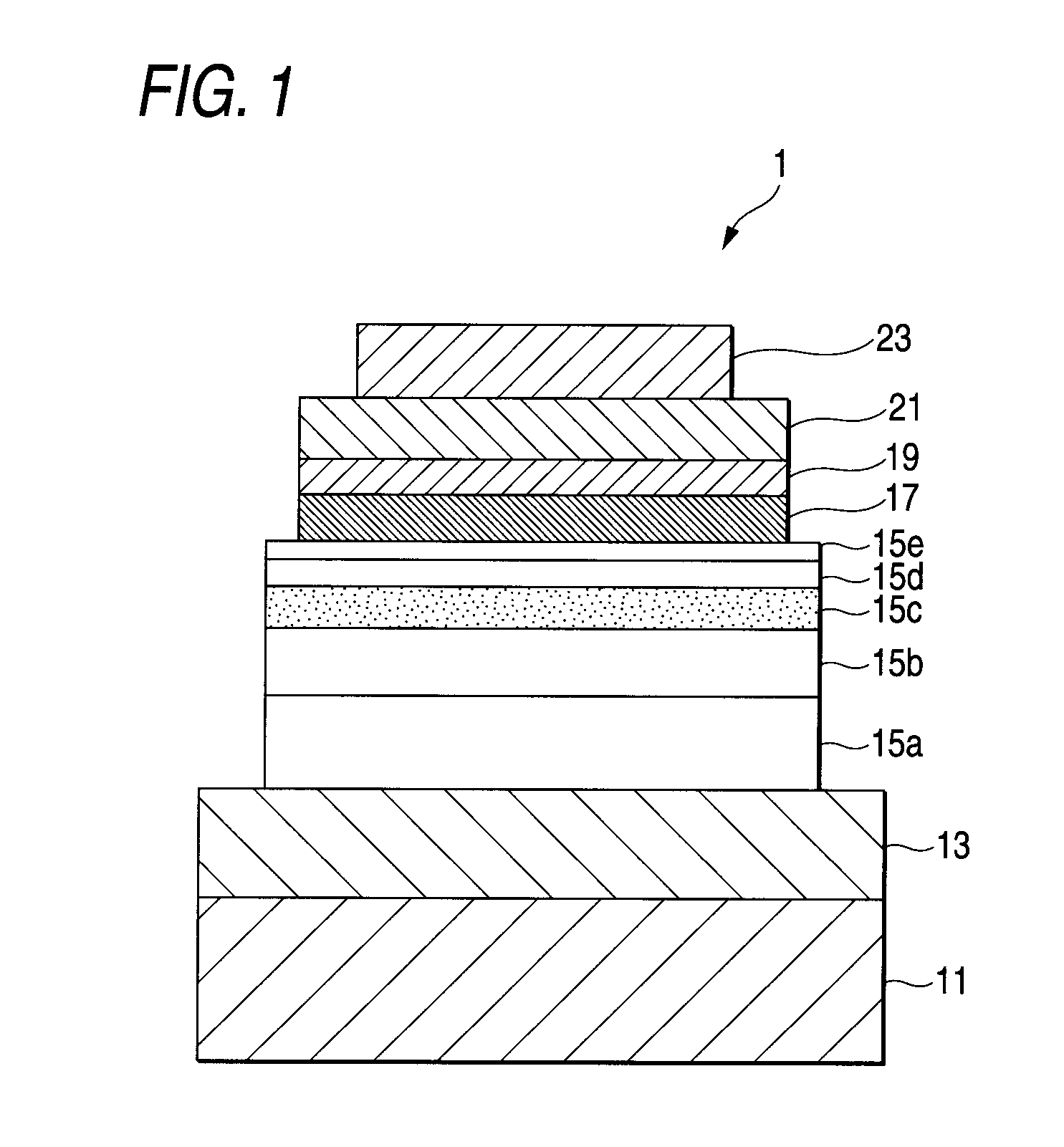

Organic electroluminescent device

ActiveUS20070182320A1Increase in drive voltageInitial luminanceDischarge tube luminescnet screensElectroluminescent light sourcesOrganic electroluminescenceTransport layer

An organic electroluminescent device provided with a lower electrode formed on a substrate, a light emitting unit having at least an organic light emitting layer and formed on the lower electrode, and a light transmissive upper electrode formed on the light emitting unit, wherein a connection layer for supplying a charge into the light emitting unit and a charge transport layer having charge transporting properties of a reverse conducting type against a charge to be injected from the upper electrode are stacked in this order from a side of the light emitting unit between the light emitting unit and the upper electrode.

Owner:SONY CORP

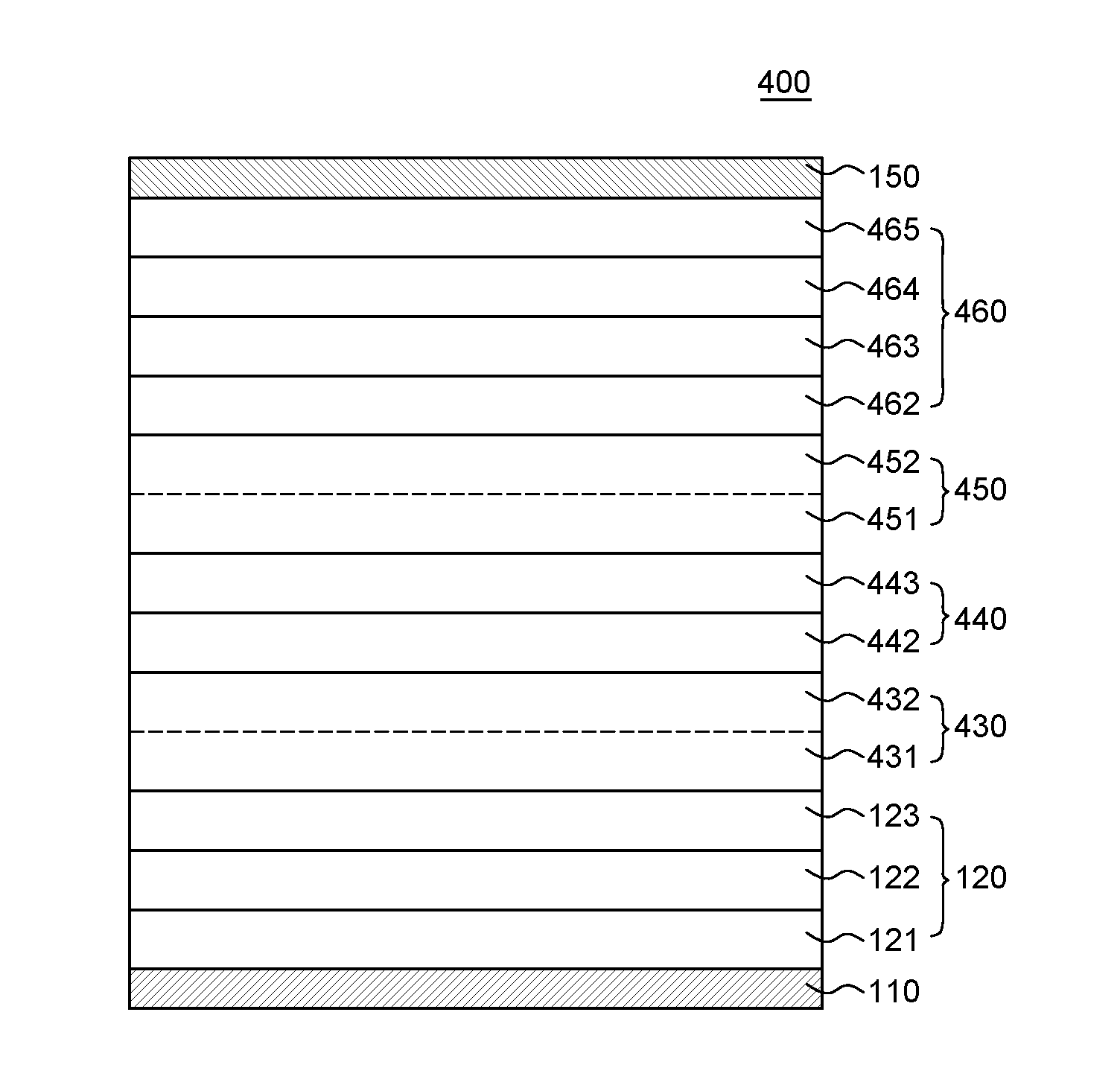

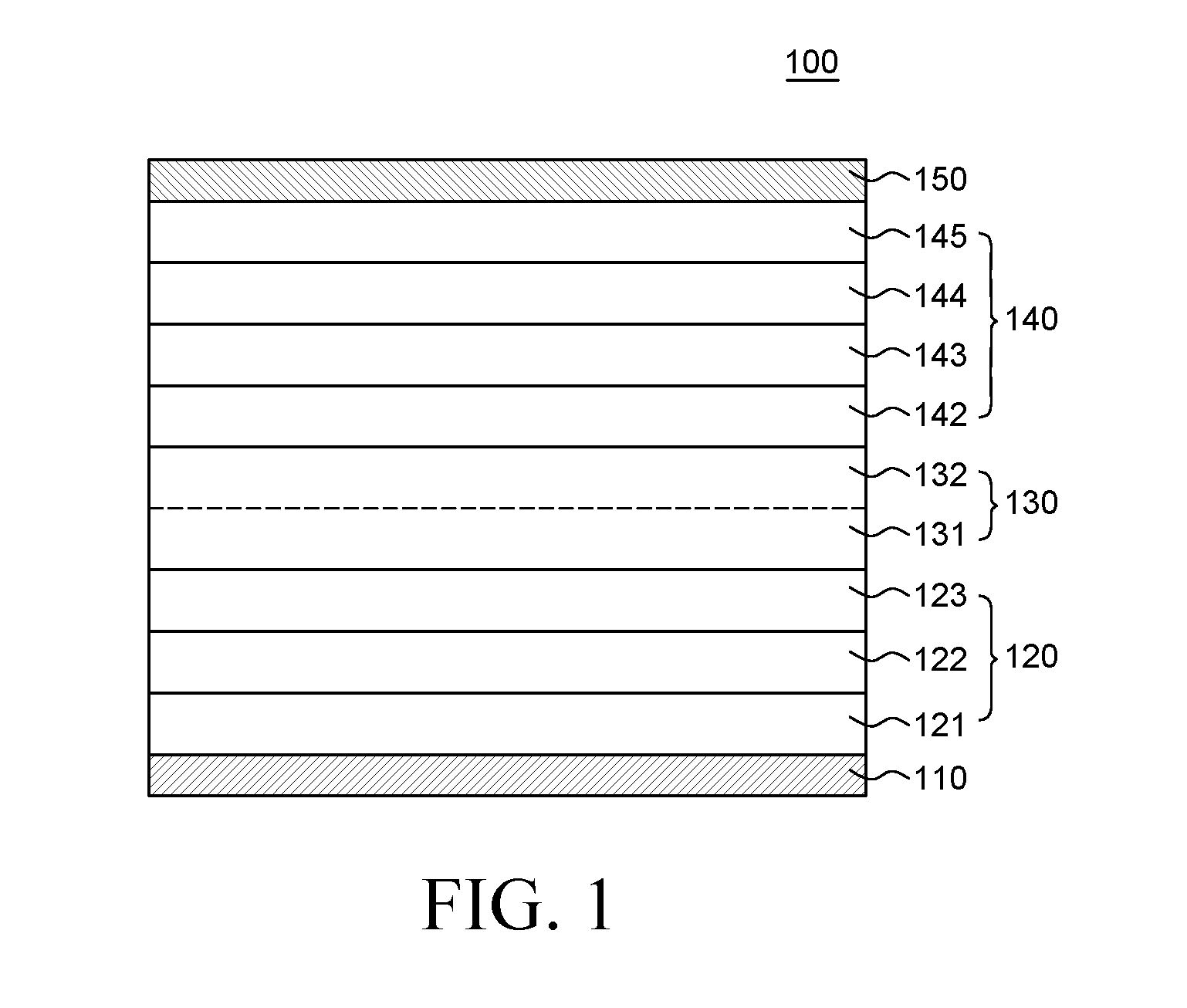

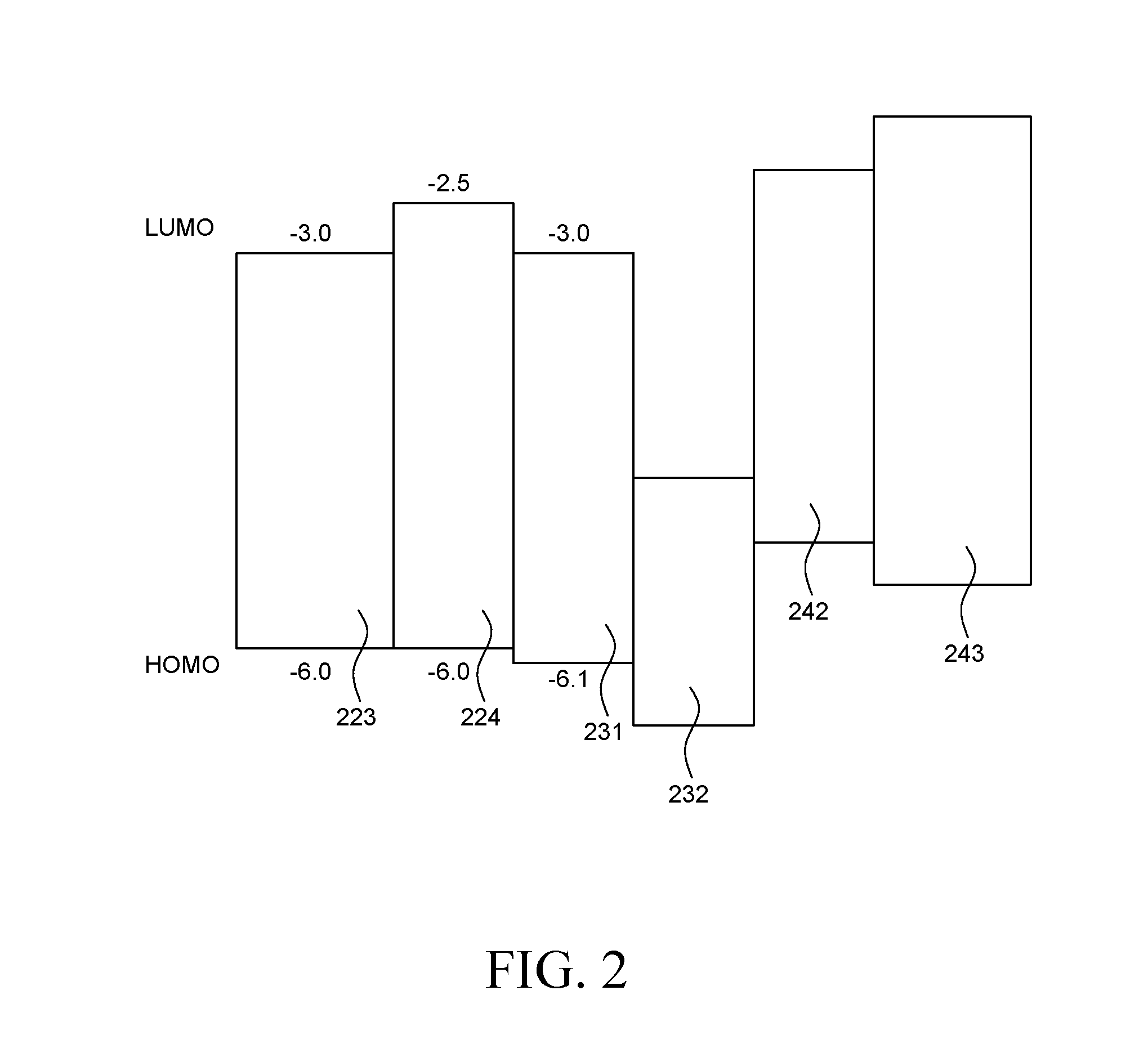

Organic Light Emitting Device

ActiveUS20160343776A1Improve color change rateImprove efficiencySolid-state devicesSemiconductor/solid-state device manufacturingOrganic light emitting deviceColor changes

Provided is an organic light emitting device. The organic light emitting device includes a plurality of light emitting units laminated between a first electrode and a second electrode and each including an organic emitting layer, and a charge generation layer between the light emitting units. Further, the charge generation layer includes an N-type charge generation layer disposed to be in direct contact with an organic emitting layer of the adjacent light emitting unit and HOMO levels of the N-type charge generation layer and the organic emitting layer are regulated. Thus, a color change rate based on a viewing angle can be improved, and efficiency and a lifetime of the organic light emitting device can be improved.

Owner:LG DISPLAY CO LTD

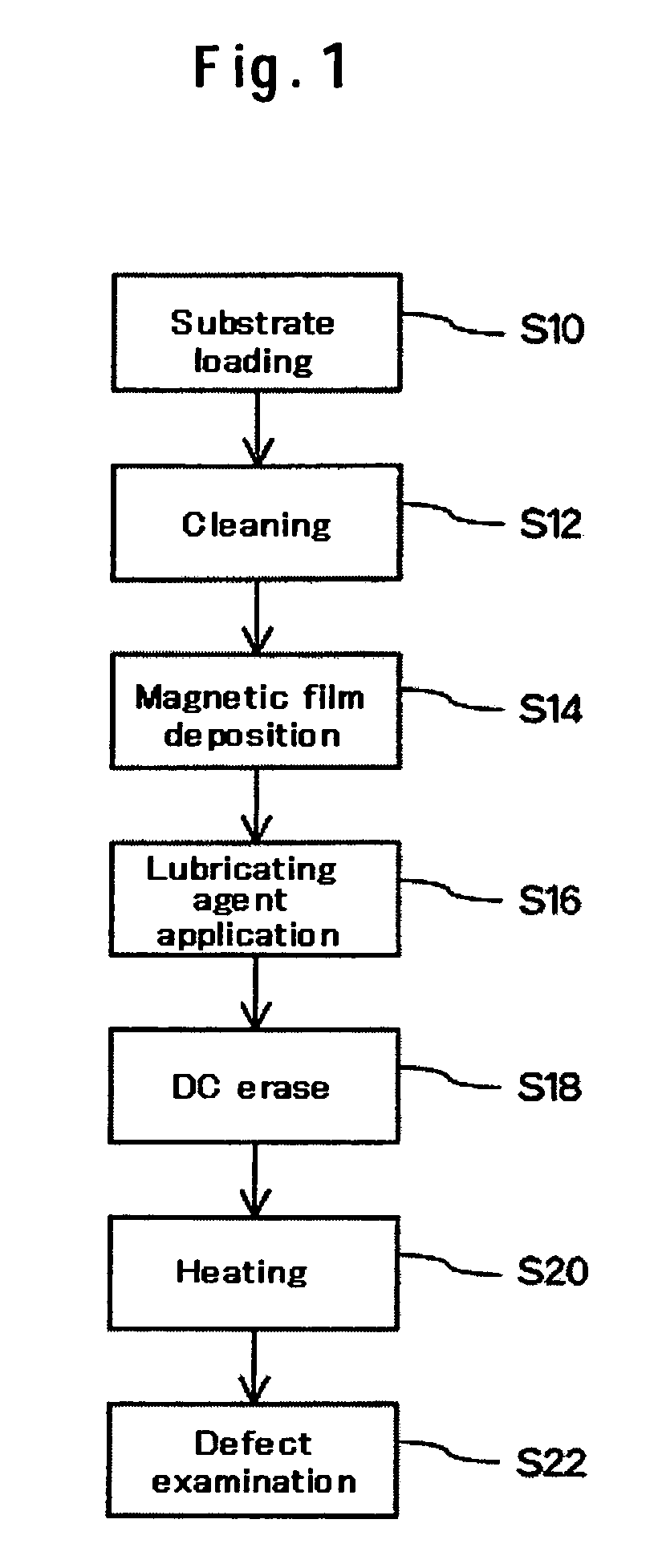

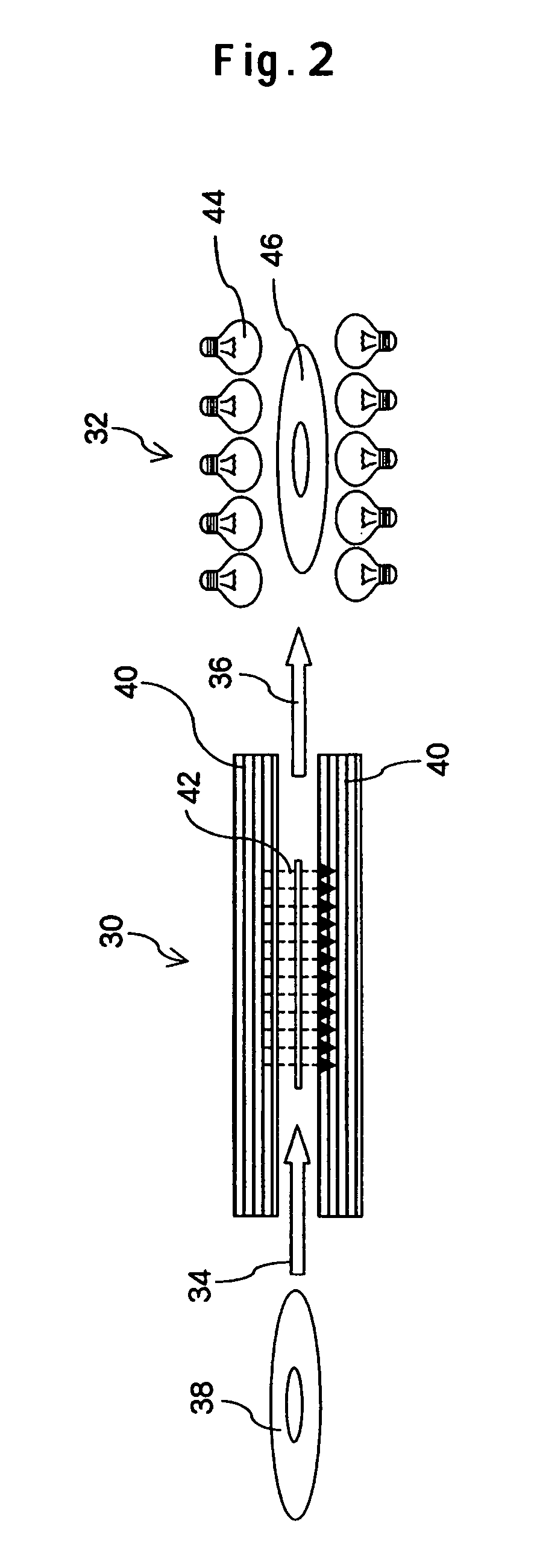

Defect inspection method for perpendicular magnetic recording medium, magnetic disk device, and method of registering defects in magnetic disk device having a perpendicular magnetic recording medium therein

InactiveUS20060109000A1Efficient detectionLower performance requirementsMagnetic property measurementsRecord information storageDemagnetizing fieldManufacturing technology

Because of its characteristics, a perpendicular magnetic recording medium has the inconvenience that since sections with low signal stability due to magnetic defects are not easily detectible in advance, these sections are detected after mounting of the medium in a magnetic disk device or after product shipping. According to one embodiment, in the manufacturing processes for the perpendicular magnetic recording medium, a DC-erase process step for direct-current demagnetizing the medium is performed after a magnetic film deposition process step and a lubricating-agent application process step. This maximizes the effects of a demagnetizing field and intentionally increases directional instability of magnetization. After the above processes, the medium is further provided with a heating process to accelerate the reversal of magnetization in latent defective sections. A defect examination step for detecting the magnetization reversal sections on the basis of changes in the baseline of the signal read out from the medium under the above state is performed, whereby defects can be detected efficiently.

Owner:HITACHI GLOBAL STORAGE TECH NETHERLANDS BV

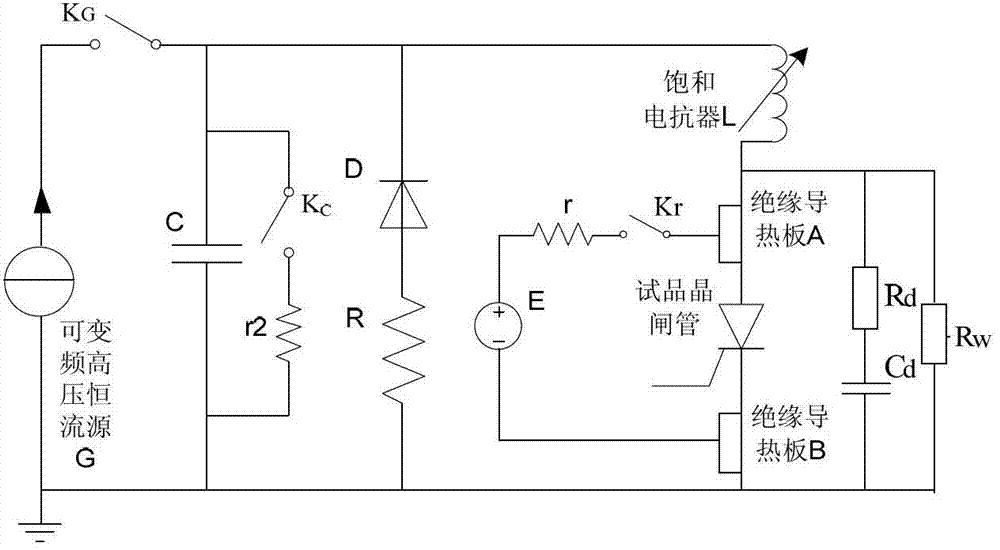

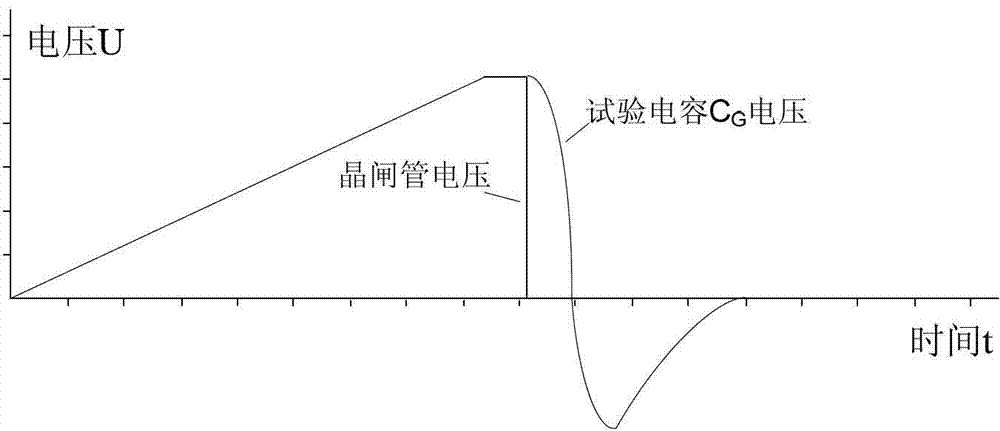

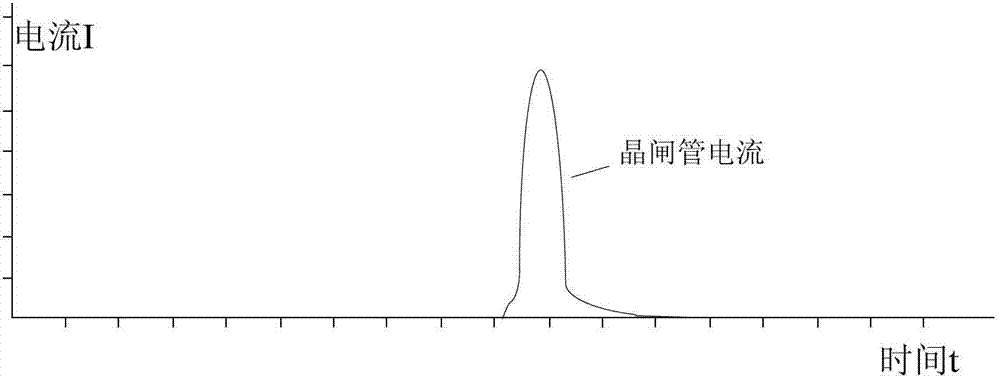

Testing method and device of thyristor switching stress

ActiveCN103048595AVersatileReduce equipment capacityTesting dielectric strengthOptimal designThyristor

The invention provides a testing method and device of thyristor switching stress, which has comprehensive functions and meets the testing requirements of the thyristor switching stress under various working conditions of a converter valve. Moreover, the topological structure of a circuit is simple and practical, the required equipment capacity is small, and the device cost is low. The testing for a single thyristor is directly carried out by the method, the capability of each thyristor inside for enduring switching voltage and current can be checked before the converter valve is assembled, and therefore the producing and manufacturing safety and economical property of the converter valve are improved. In addition, the testing strength of electrothermal stress can be improved by adjusting testing parameters by the method, and therefore the limiting tolerance value of the thyristor switching stress can be known through continuous tests, and bases are provided for the optimal design of a converter-valve system.

Owner:CHINA EPRI ELECTRIC POWER ENG CO LTD +2

MEMS Device with Surface Having a Low Roughness Exponent

ActiveUS20080187154A1Effect device performanceReduce equipment capacityTransducer detailsSemiconductor electrostatic transducersCapacitanceMems microphone

A MEMS microphone has a backplate and a movable diaphragm that together form a variable capacitance. The backplate has a backplate surface and, in a corresponding manner, the diaphragm has a diaphragm surface that faces the backplate surface. At least one of the backplate surface and the diaphragm surface has at least a portion with a Hurst exponent that is less than or equal to about 0.5.

Owner:INVENSENSE

Input device with user-balanced performance and power consumption

InactiveUS20060030374A1Improve device performanceIncreased power consumptionEnergy efficient ICTPower supply for data processingBalance performancePower management

Operational characteristics of a wireless input device are modified so as to balance performance and power conservation. Power management algorithms may include an algorithm that improves device performance and increases device power consumption, as well as an algorithm that decreases device power consumption and reduces device performance. An algorithm that most closely corresponds to the desired balance of performance and power consumption is identified. The identified algorithm is then transmitted to the wireless device.

Owner:MICROSOFT TECH LICENSING LLC

Exposure apparatus, operation decision method, substrate processing system, maintenance management method, and device manufacturing method

ActiveUS7692764B2Reduce equipment capacityImprove operating rateLiquid processingPhotomechanical apparatusPrimary operationDowntime

An exposure apparatus is equipped with a main controller that decides an operation of the exposure apparatus based on information on maintenance from a C / D. Therefore, the main controller can decide to perform a specific operation, which is necessary for maintaining performance of the exposure apparatus and requires stop of the primary operation of the exposure apparatus, during maintenance of the C / D, that is, when the primary operation of the exposure apparatus has to be stopped by necessity, in parallel with the maintenance of the C / D. As a consequence, downtime of the exposure apparatus necessary for performing the specific operation can be decreased as a whole, which makes it possible to improve the operating rate without lowering apparatus performance of the exposure apparatus that is inline connected to a substrate processing apparatus.

Owner:NIKON CORP

Quantum-well photoelectric device assembled from nanomembranes

ActiveUS20090283749A1Lower defectSuperior virtual substrateSemiconductor/solid-state device manufacturingNanoopticsQuantum wellPhotoelectric effect

Owner:WISCONSIN ALUMNI RES FOUND

Device and method for performing information processing using plurality of processors

InactiveUS7111119B2Increase the number ofReduce equipment capacityInput/output to record carriersMemory adressing/allocation/relocationMemory addressInformation processing

Owner:HITACHI LTD

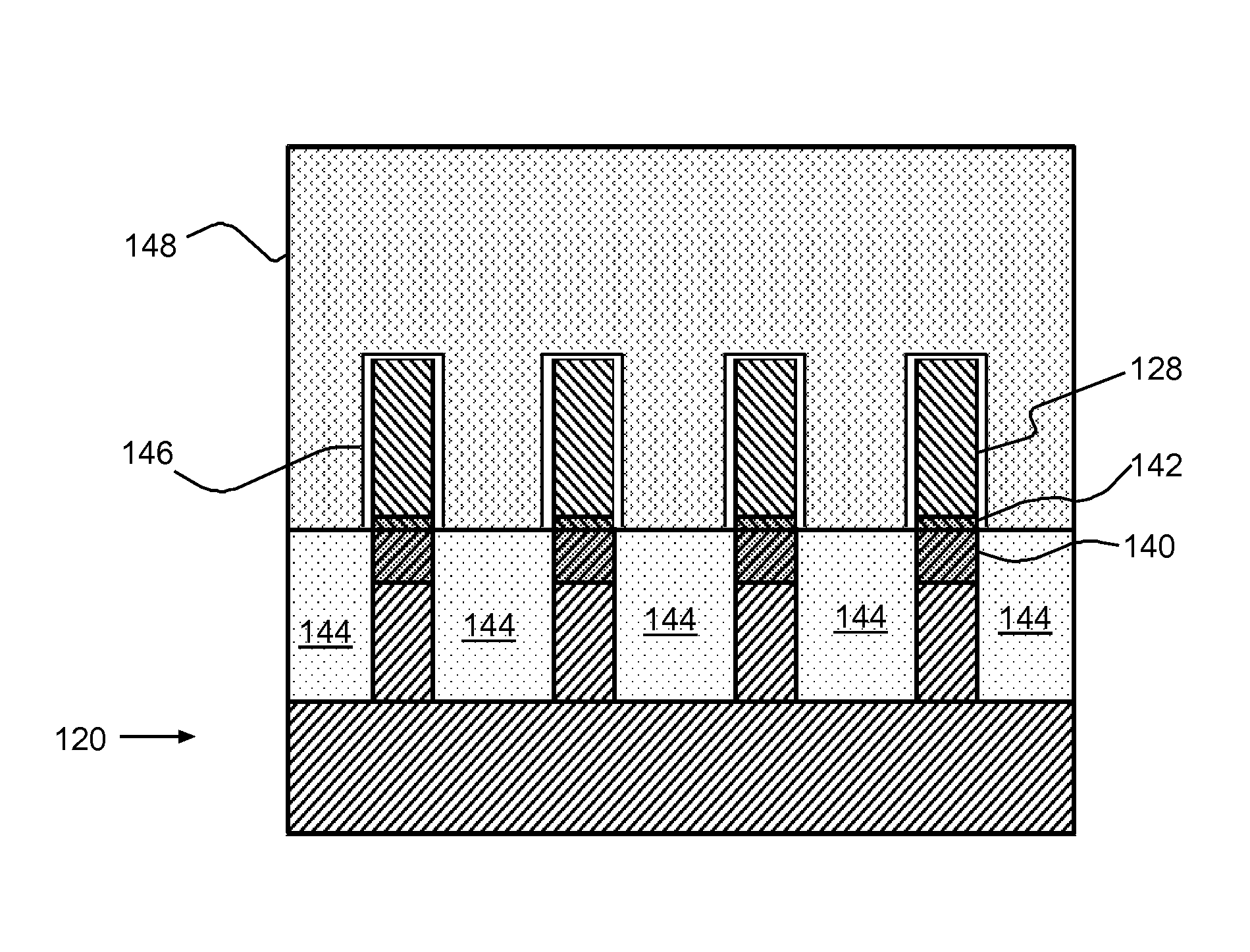

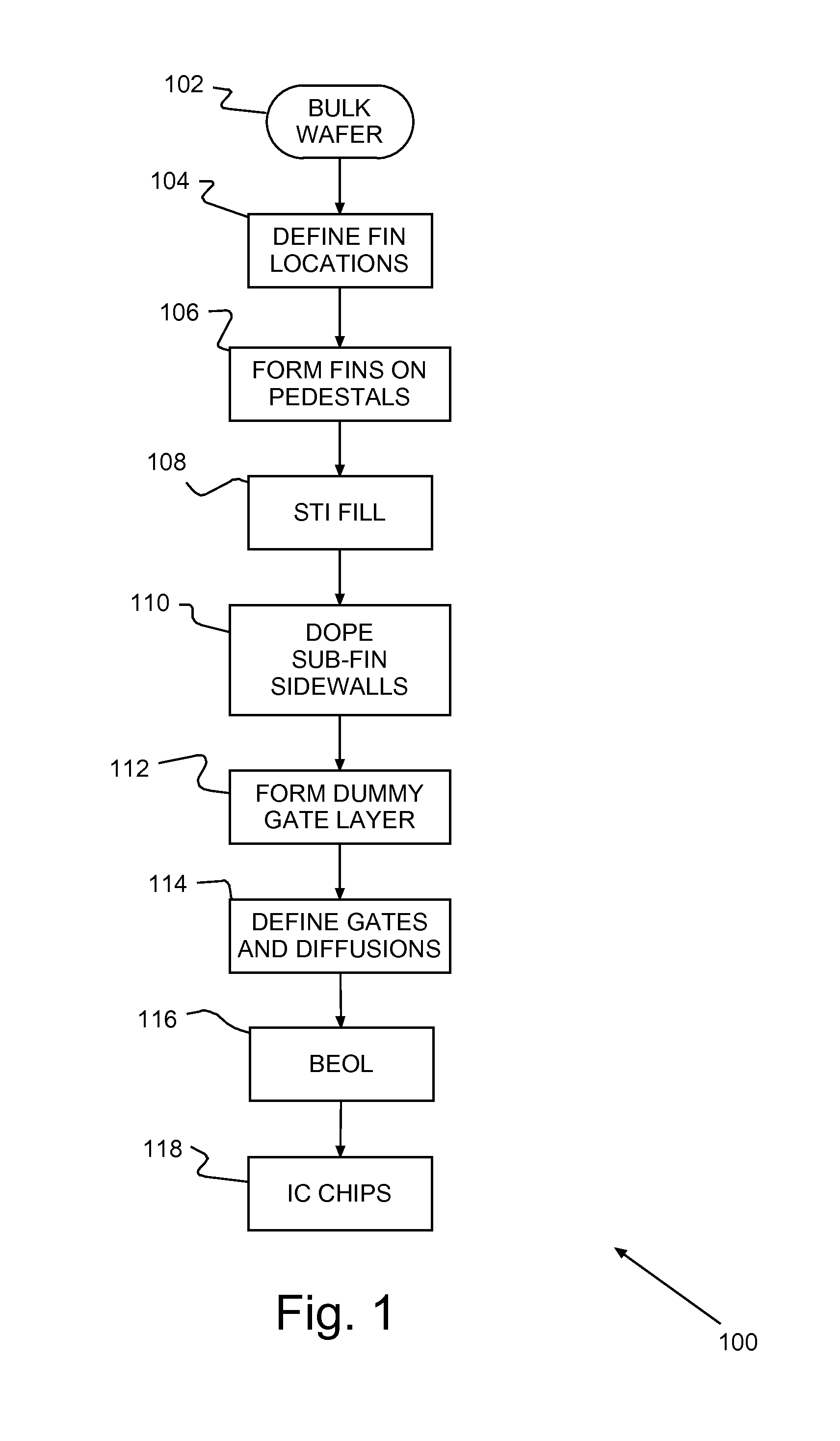

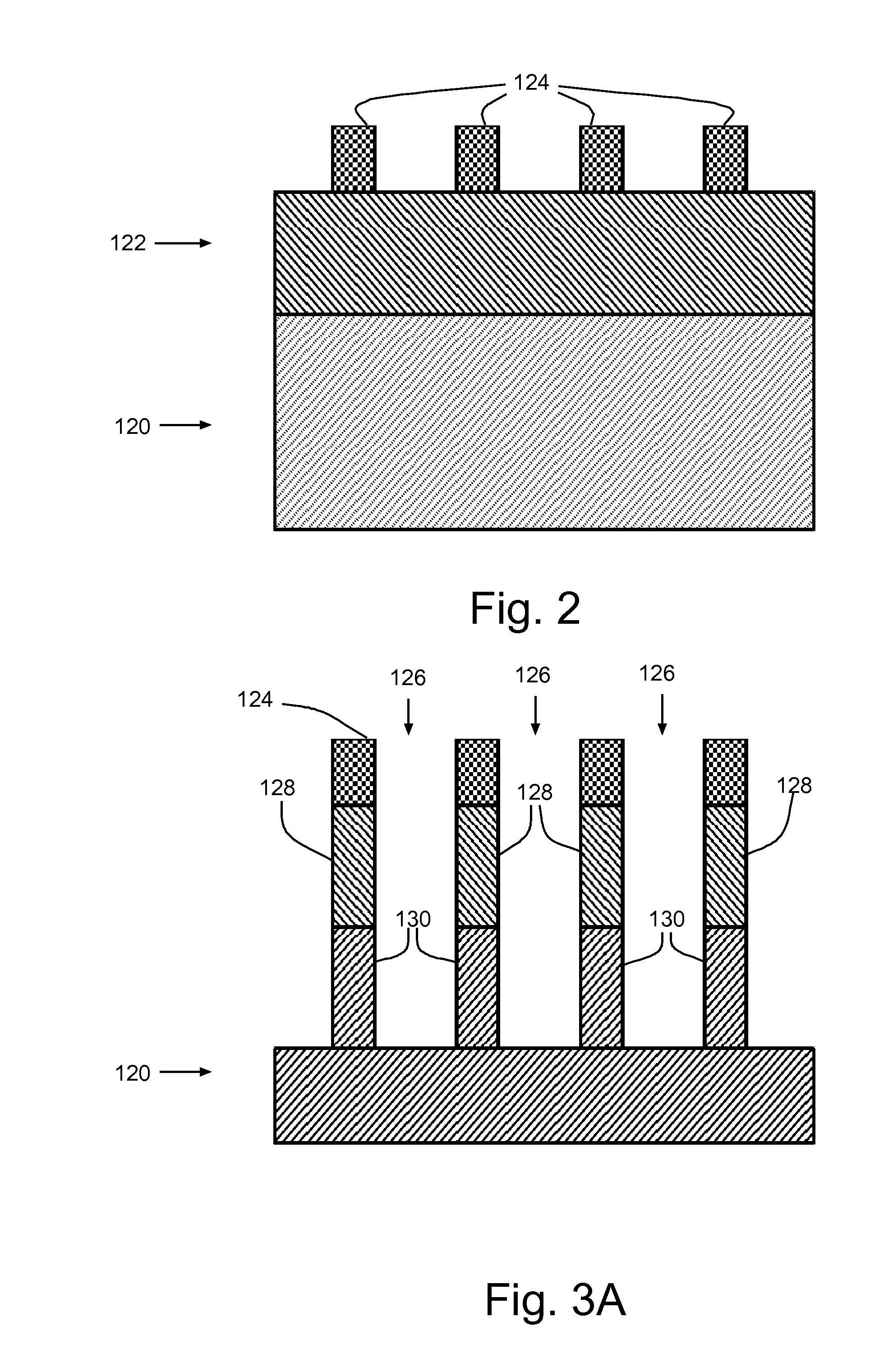

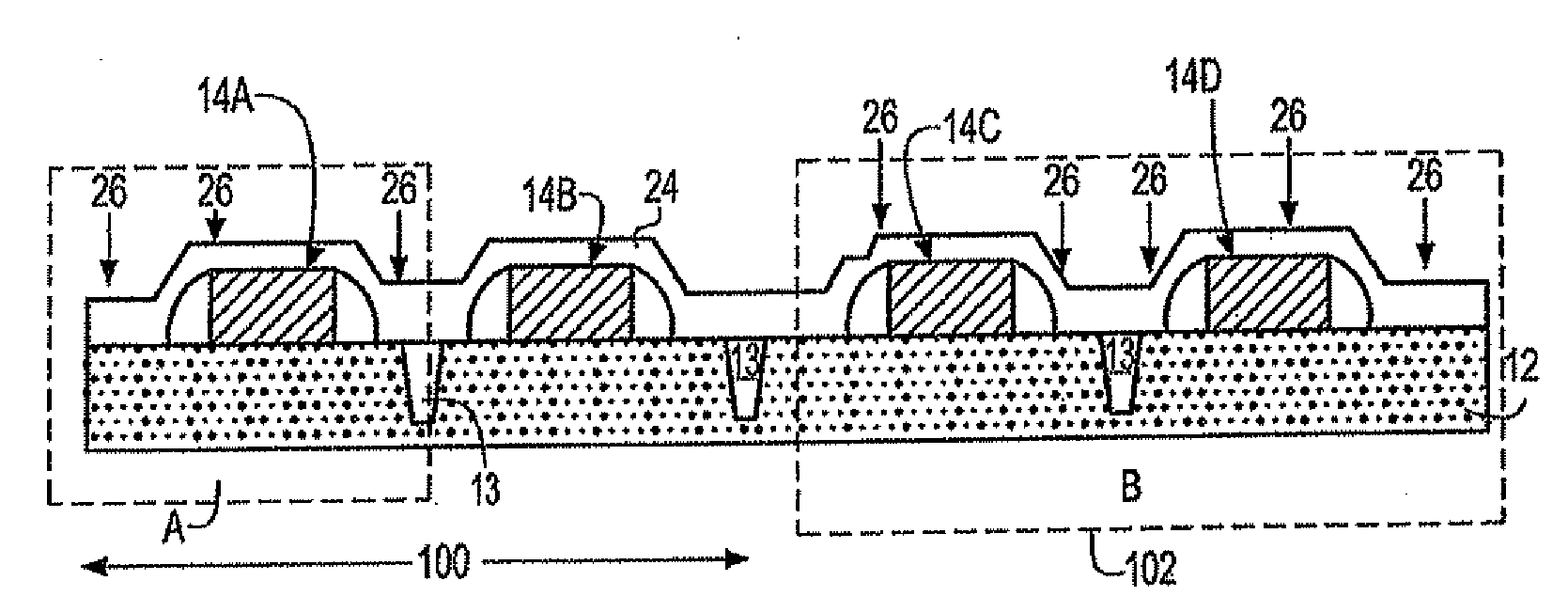

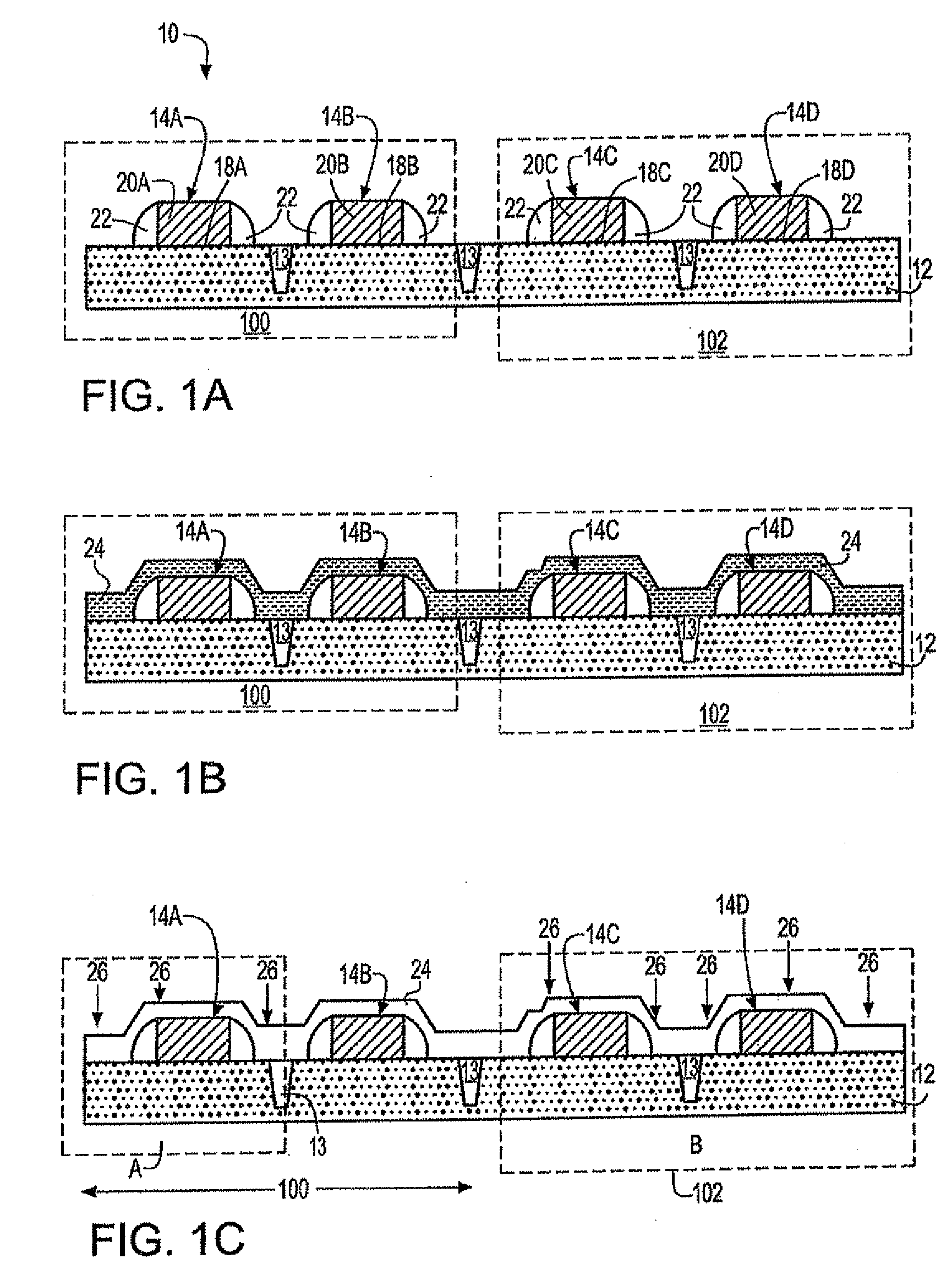

Sub-fin doped bulk fin field effect transistor (finfet), integrated circuit (IC) and method of manufacture

ActiveUS20160329326A1Reduce punch-through currentReduce equipment capacityTransistorSolid-state devicesDopantEngineering

A field effect transistor (FET), integrated circuit (IC) chip including the FETs and a method of forming the IC. Fins on pedestals are defined, e.g., with a hard mask, in a fin layer on a semiconductor wafer and spaces between the pedestals are filled with dielectric material, e.g., shallow trench isolation (STI). Sacrificial sidewalls are forming along the sides of fins and pedestal sub-fins sidewalls are re-exposed. Pedestal sub-fins are doped with a punch-though dopant and punch-though dopant is diffused into the sub-fins and the bottoms of fins. After removing the hard mask and sacrificial sidewalls, metal FET gates are formed on the fins.

Owner:IBM CORP

Structure of static random access memory with stress engineering for stability

InactiveUS7471548B2Improve performanceStability and writabilityTransistorTransducer detailsStatic random-access memoryRandom access memory

Owner:INT BUSINESS MASCH CORP +1

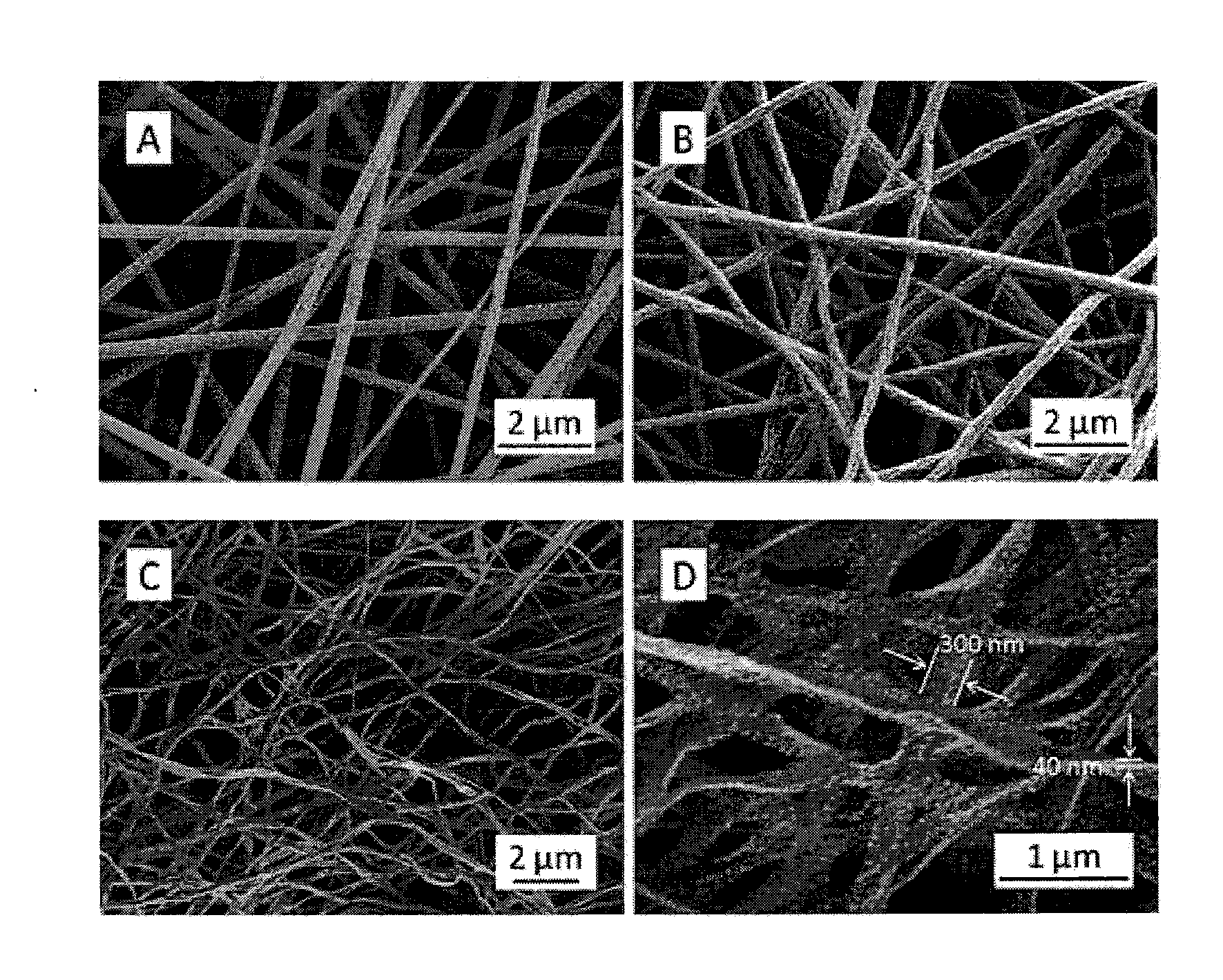

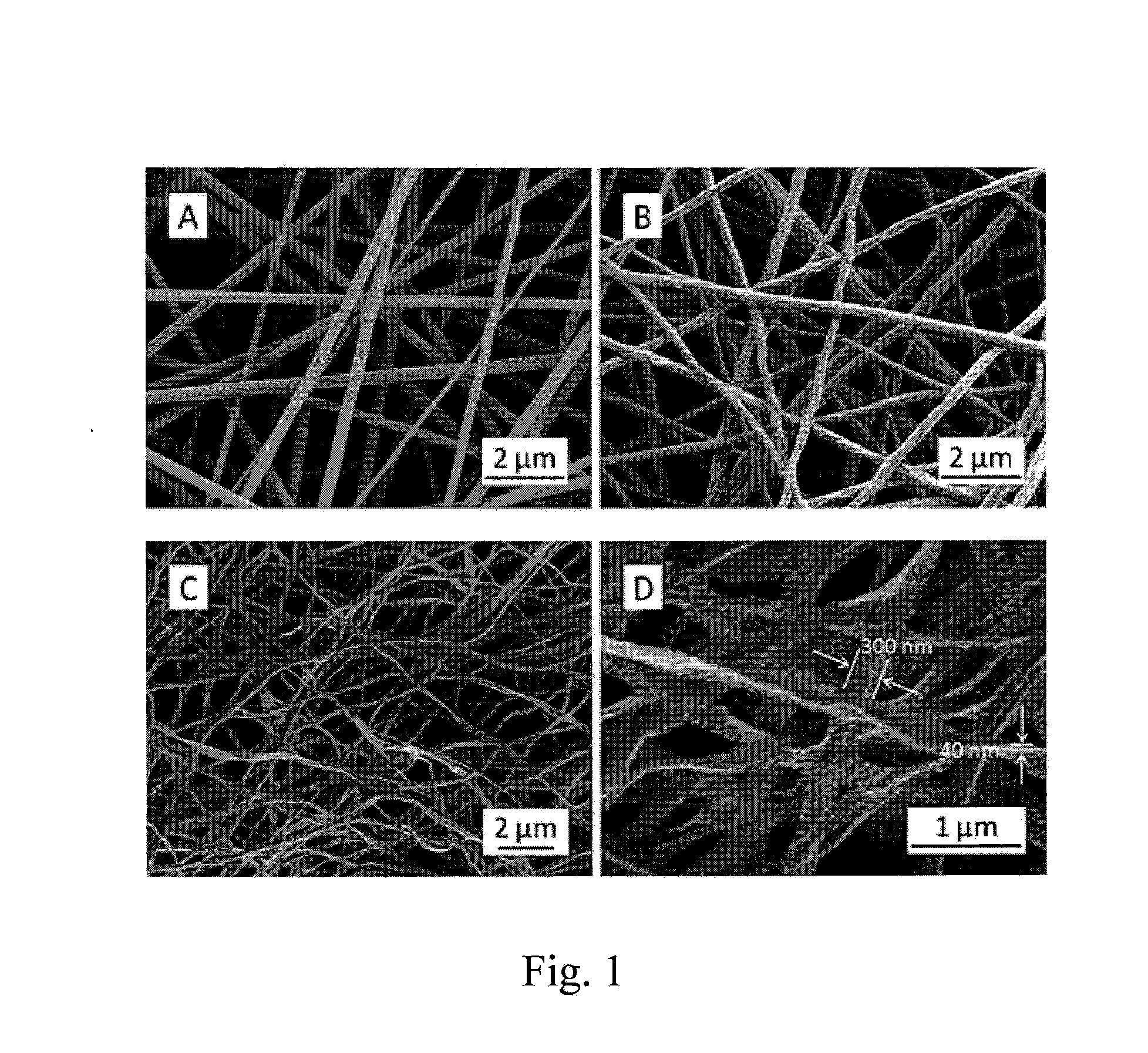

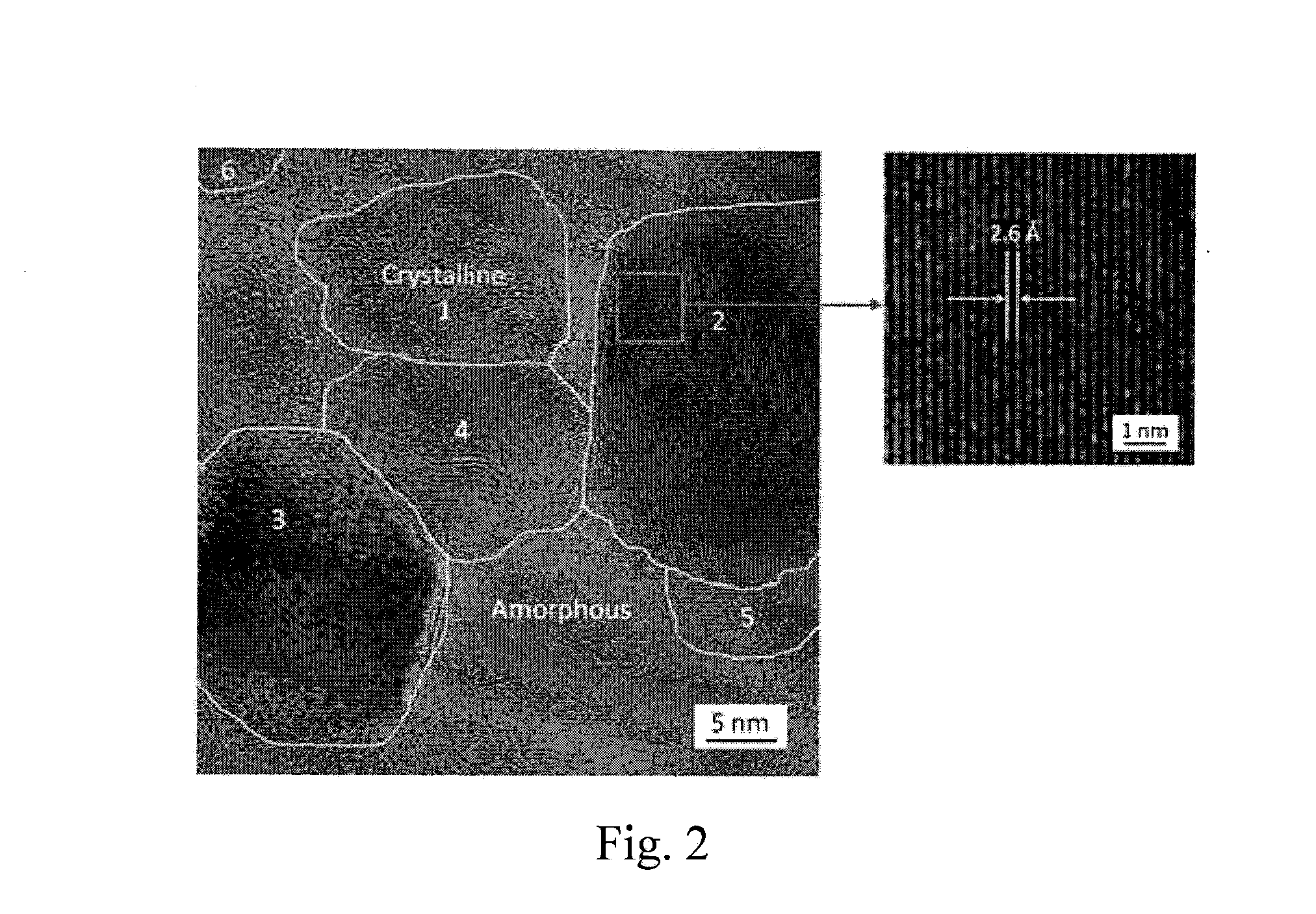

Mechanically Resilient Titanium Carbide (TIC) Nano-Fibrous Felts Consisting of Continuous Nanofibers or Nano-Ribbons with TIC Crystallites Embedded in Carbon Matrix Prepared via Electrospining Followed by Carbothermal Reduction

ActiveUS20120315815A1High specific surface areaExcellent electro capacitance propertyMaterial nanotechnologyElectric discharge heatingElectrospinningCrystallite

Owner:SOUTH DAKOTA BOARD OF REGENTS

Device with encapsulated gel

ActiveUS20130023748A1Simple interfaceReduce equipment capacityElectroencephalographySensorsMedicineBiomedical engineering

Apparatus and techniques are provided for interfacing a device with a surface. The apparatus and techniques provide gel encapsulation and isolation mechanisms to extend the shelf-life of the preparation devices, allow for the use of more effective materials, and improve the quality of the contact between a device and an application surface. Particular embodiments of these apparatus and techniques suitable for use in medical contexts are also provided.

Owner:TYCO HEALTHCARE GRP LP

Method of forming an interconnect structure with high process margins

ActiveUS20150206836A1Reduce aspect ratioReliable and reliableSemiconductor/solid-state device detailsSolid-state devicesConductive materialsMask layer

A method of forming an interconnect structure with high process margin. The present invention provides higher aligning margin for the connection of via parts and line parts. The method for forming the interconnect structure includes the steps of: forming a first mask layer with a plurality of first openings over the first insulating layer; forming a second insulating layer over the mask layer; forming a second mask layer with a plurality of second openings over the second insulating layer; performing an etching process by using the second mask layer to form a plurality of cavities penetrating through the second insulating layer, the first mask layer, and the first insulating layer; and filling the plurality of cavities with at least one conductive material.

Owner:NAN YA TECH

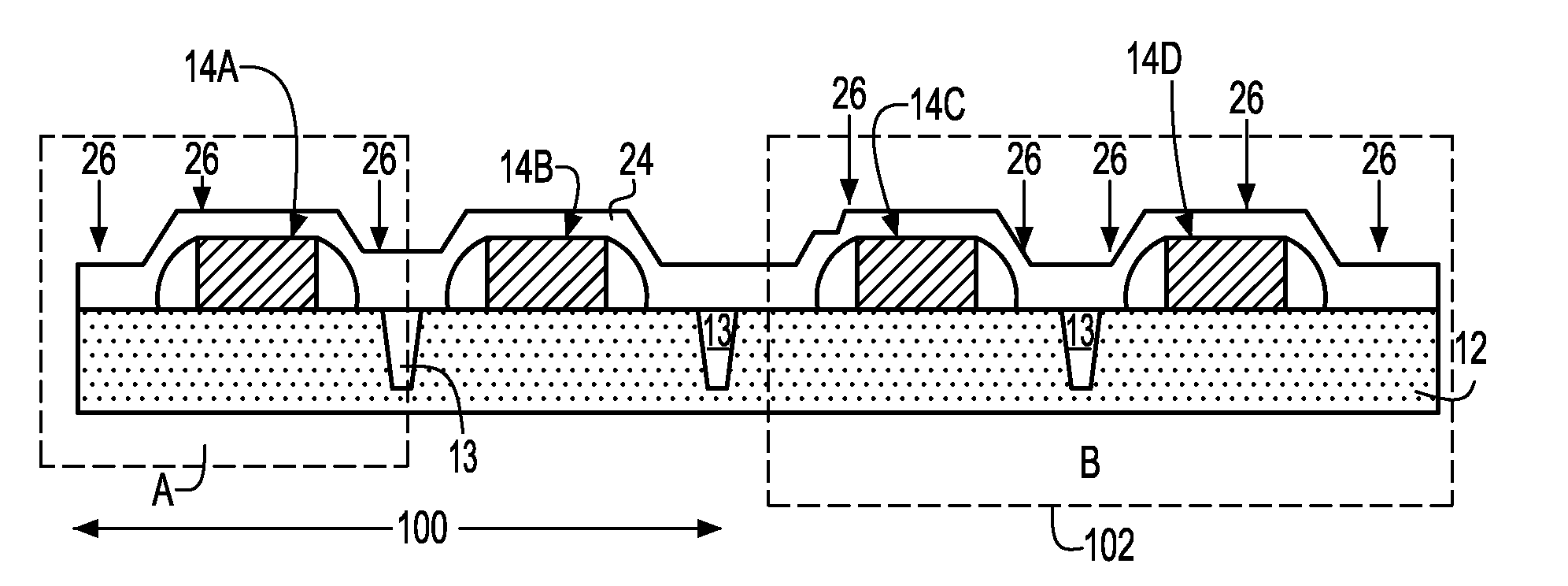

Stress engineering for SRAM stability

InactiveUS20090166757A1Improve stabilityGood writabilityTransistorSolid-state devicesStatic random-access memoryEngineering

A design structure embodied in a machine readable medium is provided for use in the design, manufacturing, and / or testing of Ics that include at least one SRAM cell. In particular, the present invention provides a design structure of an IC embodied in a machine readable medium, the IC including at least one SRAM cell with a gamma ratio of about 1 or greater. In the present invention, the gamma ratio is increased with degraded pFET device performance. Moreover, in the inventive IC, there is no stress liner boundary present in the SRAM region and ion variation for all devices is reduced as compared to that of a conventional SRAM structure. The present invention provides a design structure of an IC embodied in a machine readable medium, the IC comprising at least one static random access memory cell including at least one nFET and at least one pFET; and a continuous relaxed stressed liner located above and adjoining the at least one nFET and the at least one pFET.

Owner:IBM CORP +1