Minimizing degradation of SiC bipolar semiconductor devices

a technology of bipolar semiconductors and degradation minimization, which is applied in the direction of chemically reactive gases, crystal growth process, polycrystalline material growth, etc., can solve the problems of limiting the use of devices or sensors for high temperature applications, the respective band gap of silicon and gallium arsenide is too small to support the generation of certain wavelengths, and the specific limitations of silicon and gallium arsenide based semiconductors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

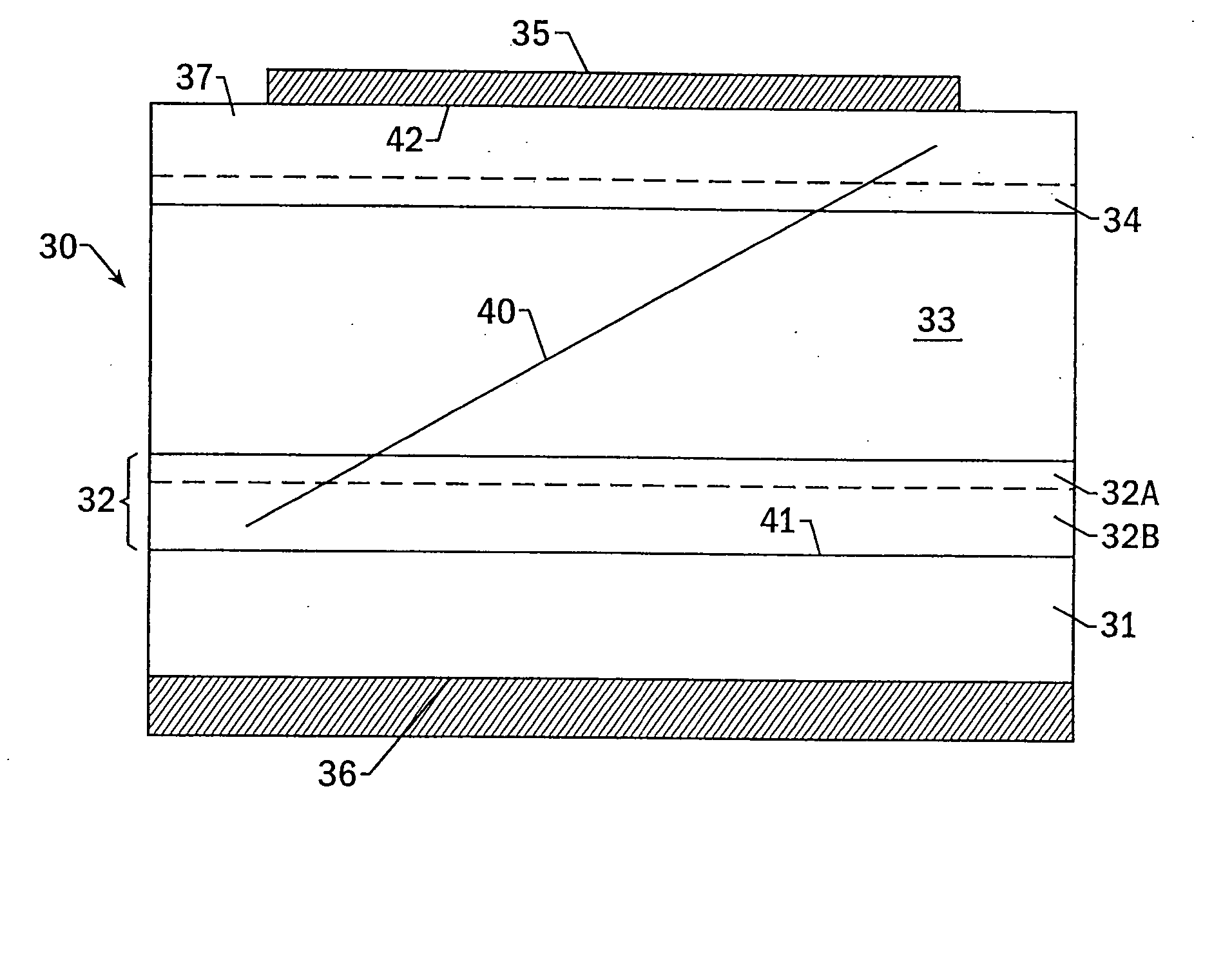

[0028]FIG. 1 is a photomicrograph of a prior art 1.2 mm×1.2 mm p-n diode broadly designated at 10. The diode depicted in plan view in FIG. 1 exhibits a patterned top side ohmic contact which permits visual inspection of the device during operation.

[0029]FIG. 1 illustrates an extensive group of stacking faults 11 that spans the entire width (vertically in the orientation of FIG. 1) of the device. Although not visible in plan view, stacking faults 11 exist in multiple atomic planes of device 10. This is typical of the type of stacking fault that grows during forward operation of the device and causes the problems referred to in the background portion of the specification. The stacking faults 11 are formed after operation of the device under forward bias conditions for 30 minutes. Regions of the stacking faults are visible in FIG. 1 because they serve as recombination centers which under some conditions produce visible light during forward bias operation due to electron-hole recombina...

PUM

| Property | Measurement | Unit |

|---|---|---|

| carrier concentration | aaaaa | aaaaa |

| carrier concentration | aaaaa | aaaaa |

| temperatures | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More